HomeBlogNMOS and PMOS Guide - How it Works, Pros and Cons, Applications, Truth Tables, Comparison of the Two

NMOS and PMOS Guide - How it Works, Pros and Cons, Applications, Truth Tables, Comparison of the Two

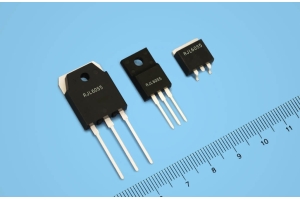

In the field of modern electronic engineering, understanding and applying semiconductor technology is one of the core skills, among which the technology and application of NMOS (negative metal oxide semiconductor) and PMOS (positive metal oxide semiconductor) transistors are crucial to circuit design. These two types of transistors work based on different charge carriers (electrons and holes) of N-type and P-type semiconductor materials respectively, demonstrating their unique physical properties and working principles. NMOS transistors conduct current through electrons, while PMOS transistors conduct current through holes. This difference directly affects their application efficiency and performance in electronic devices. This article will deeply analyze the definition, working principle, technical advantages, and disadvantages of these two transistors, and compare their application scenarios to reveal their importance and complementarity in modern electronic technology.

Catalog

1. Definition and working principle of NMOS transistor

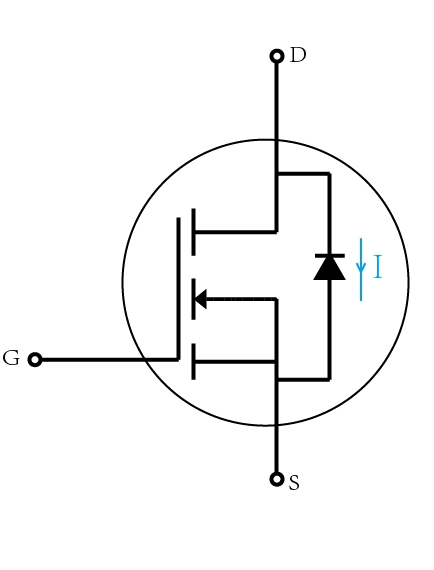

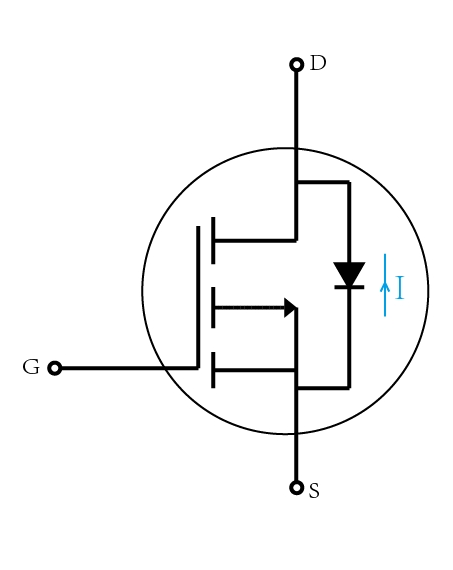

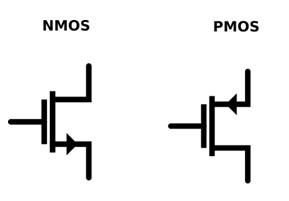

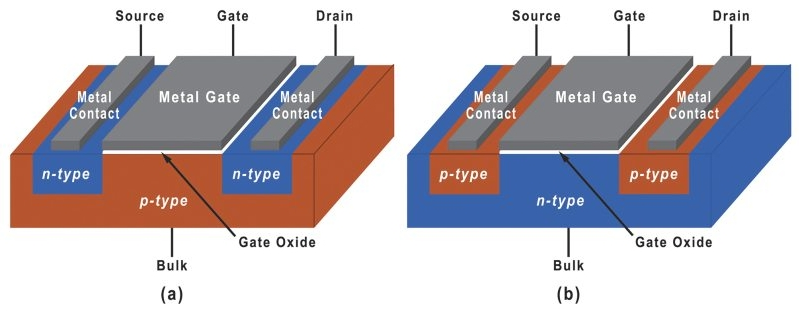

NMOS transistor is the abbreviation of N-type metal oxide semiconductor field effect transistor, which relies on electrons to conduct current. Its source and drain components are both made of N-type semiconductor materials. , the gate component regulates the current through voltage control.

NMOS transistors work by applying a positive voltage to the gate. This is usually done by turning a voltage regulator or adjusting the output of the power supply. Doing so creates an electron path between the source and the drain. This operation requires precise control of voltage levels and the timing of their application. This precision facilitates the formation of stable conductive channels. If the voltage is too high or too low or applied at the wrong time, it can cause the transistor to degrade or even be damaged.

The voltage applied to the gate is called the gate-source voltage (V_GS). Once V_GS exceeds a certain threshold, called the threshold voltage (V_th), an inversion layer forms between the source and drain. This layer is made up of electrons and is thin, but thin enough to allow current to flow, allowing the transistor to conduct electricity. The threshold voltage is affected by the transistor's physical design and manufacturing materials and is set during the design phase.

2. Technical advantages and disadvantages of NMOS transistors

2.1 Advantages of NMOS transistors:

NMOS transistors are preferred for high-speed applications because of their fast switching capabilities. This is mainly because the electrons that carry the current in NMOS transistors have higher mobility than holes and can move through the semiconductor material faster. As a result, NMOS transistors can turn on and off very quickly, resulting in faster processing and faster response times.

Another major advantage is the compact size. The physical design of NMOS transistors makes them smaller than many other types of transistors. This allows more transistors to be packed into a smaller space, helping to create smaller, denser integrated circuits. This miniaturization requires higher precision and advanced technology during the actual assembly and soldering of circuit boards. Operators often need to employ sophisticated tools and techniques, such as micro-soldering tools and precision positioning equipment, to efficiently handle and assemble these tiny components.

2.2 Disadvantages of NMOS transistors:

Despite these advantages, NMOS transistors have their disadvantages. An important issue is their relatively high power consumption in the "on" state, which is caused by the rapid movement of electrons. This can cause equipment that runs continuously for long periods to consume more energy and potentially overheat. To address this issue, operators must consider effective thermal management strategies during the design and testing phases, such as adding heat sinks or fans to dissipate excess heat.

Additionally, NMOS transistors have a lower noise margin compared to other types of transistors. Noise margin is the maximum voltage or current fluctuation that a circuit can withstand without affecting its normal function. In environments with higher electronic noise, NMOS transistors can become less stable and more susceptible to interference, affecting their performance and reliability. Operators and designers must consider this and may incorporate additional shielding or select alternative components for noise-sensitive applications.

3. Definition and working principle of PMOS transistor

PMOS transistor, namely P-type metal oxide semiconductor field-effect transistor, is a device that uses P-type semiconductor material as its source and drain. Compared with NMOS transistors of N-type semiconductors, PMOS transistors work in the opposite mechanism and rely on positive charge carriers, namely holes, to conduct current.

When a negative voltage is applied to the gate (relative to the source), the following changes will occur: the formation of the electric field causes the holes in the P-type semiconductor between the source and drain to move closer to the gate, thereby creating a gap between the source and drain. A hole accumulation area is formed between them, that is, a conductive channel. This channel allows current to flow smoothly, causing the transistor to conduct. The process of applying negative voltage requires precise control of the magnitude of the voltage and the time of application to ensure that the conductive channel is effectively formed without causing damage due to excessive voltage. This operation is usually performed through a precise power management system, which requires monitoring voltmeters and ammeters to adjust and confirm the correctness of the voltage. When adjusting the gate voltage, the required negative voltage value must be accurately calculated because this directly affects the response speed and efficiency of the transistor. A voltage that is too low may cause the transistor to fail to conduct effectively, while a voltage that is too high may damage the transistor or reduce its long-term stability.

4. Technical advantages and disadvantages of PMOS transistors

4.1 Advantages of PMOS Transistors:

PMOS transistors are highly valuable in circuits where power efficiency is important, especially because they consume less power when turned on. This increase in efficiency is because the current in a PMOS transistor is carried by holes, which require less energy to move than electrons. This feature makes PMOS transistors ideal for battery-operated or energy-sensitive devices that require energy conservation.

In addition, PMOS transistors have excellent noise tolerance, making them reliable in environments with high electrical interference. Their ability to withstand unexpected voltage fluctuations allows engineers to create more stable circuits. This stability facilitates the design of consistent and robust signal transmission paths, thereby enhancing overall device reliability during circuit layout and testing.

4.2 Disadvantages of PMOS transistors:

The downside is that PMOS transistors have some limitations that affect their performance in fast-paced applications. The mobility of holes (charge carriers in PMOS transistors) is lower than the mobility of electrons. The lower mobility results in slower switching compared to NMOS transistors. If this problem needs to be solved, circuit designers must implement careful timing control and find ways to improve response time. Strategies might include optimizing circuit layout or integrating multiple transistors in parallel to run faster.

In addition, the physical size of PMOS transistors poses a challenge to the current trend of integrated circuit miniaturization. As electronic devices become smaller and the need for compact components continues to grow, designers and engineers are forced to develop innovative approaches. These approaches may involve rethinking transistor design or employing new technologies to shrink transistor size while still maintaining the advantages of low power consumption and high noise immunity.

5. NMOS and PMOS: truth table

|

Gate Voltage (V_Gs) |

Souree-Drain Current (l Ds) |

Transistor State |

|

High (Logic 1) |

High |

ON |

|

Low (Logic 0) |

LOW |

OFF |

In both tables:

"Gate voltage (V_GS)" refers to the voltage applied to the gate terminal relative to the source terminal.

"Source-Drain Current (I_DS)" indicates whether current can flow from the source to the drain terminal.

"Transistor State" specifies whether the transistor is in the ON state (conducting) or the OFF state (not conducting).

For an NMOS transistor, when the gate voltage is high (logic 1), the transistor conducts (ON), allowing current to flow from source to drain. Conversely, when the gate voltage is low (logic 0), the transistor is turned off, and no appreciable current flows.

For PMOS transistors, when the gate voltage is low (logic 0), the transistor conducts (ON), allowing current to flow from the drain to the source. When the gate voltage is high (logic 1), the transistor is turned off, and negligible current flows.

6. Comparison between NMOS and PMOS

PMOS (Positive Metal Oxide Semiconductor) and NMOS (Negative Metal Oxide Semiconductor) transistors play an important role in electronic circuits. Each type utilizes different charge carriers and semiconductor materials, affecting its functionality and suitability for different applications.

|

Aspect |

NMOS (N-type

Metal-Oxide-Semiconductor) |

PMOS (P-type

Metal-Oxide-Semiconductor) |

|

Majority Charge Carriers |

Electrons |

Holes (Positive Charge Carriers) |

|

Semiconductor Type |

n-type |

p-type |

|

Gate Voltage Control |

Positive Voltage |

Positive Voltage |

|

Operation |

Conducts when Gate is Positive |

Conducts when Gate is Negative |

|

Switching Speed |

Faster Switching Speed |

Slower Switching Speed |

|

Power Consumption |

Higher Power Consumption |

Lower Power Consumption |

|

Noise Immunity |

Lower Noise Immunity |

Higher Noise Immunity |

|

Applications |

High-Speed Digital Circuits,

Microprocessors, Memory Cells, Integrated Circuits |

Low-Power Digital Circuits, CMOS

Technology, Analog Amplifiers, Voltage Level Shifters, Power Management

Circuits |

7. NMOS and PMOS: Which one is better?

Electrons, which are charge carriers in NMOS transistors, exhibit higher mobility compared to the holes used in PMOS transistors, a property that enables faster operation. NMOS devices are also typically less expensive to manufacture. However, they tend to consume more power, especially in the "on" state, as they draw a lot of current to keep running.

In contrast, PMOS transistors have lower leakage currents in the "off" state, making them more suitable for applications where idle power consumption needs to be minimized. Additionally, PMOS devices are more robust at high voltages, thanks to the lower mobility of holes, which makes them less susceptible to rapid changes in current. PMOS transistors typically operate slower than NMOS transistors due to their lower mobility.

The choice between NMOS and PMOS transistors depends largely on the specific needs of the application. NMOS is often the first choice for applications where speed and cost-effectiveness are a priority. PMOS, on the other hand, is more suitable for environments that require stability under high voltage conditions and low leakage current.

Many modern circuits utilize both NMOS and PMOS transistors in a complementary manner, a configuration called CMOS (Complementary Metal Oxide Semiconductor). This approach leverages the advantages of both transistor types to enable energy-saving and high-performance designs, especially beneficial for digital integrated circuits that require low power consumption and high speed.

8. Conclusion

When comparing NMOS and PMOS transistors, it is clear that each type has its advantages, especially when used in CMOS circuit designs. NMOS transistors are particularly valued for their fast switching capabilities and cost-effectiveness, making them ideal for high-performance applications that require fast response. PMOS transistors, on the other hand, excel in environments where power efficiency and high voltage are critical due to their inherently low leakage current and strong voltage stability. In practice, electronics engineers must carefully select the type of transistor to use based on the specific needs of the project. For applications where speed and budget are priorities, NMOS is often preferred. Instead, for projects where energy conservation and handling high voltages are critical, PMOS transistors are more suitable.

Frequently Asked Questions [FAQ]

1. What would happen if we interchanged PMOS and NMOS?

In many circuit designs, PMOS and NMOS are often used complementary. If they are swapped, the functionality of the circuit may completely change or cause the circuit to become inoperable. For example, in CMOS technology, PMOS is typically used to pull the output high, while NMOS is used to pull the output low. Swapping these two types of transistors will cause the output logic to be reversed, affecting the logic behavior of the entire circuit.

2. Which is better, NMOS or PMOS current source?

Both NMOS and PMOS can be used as current sources, but they each have advantages in specific applications. Generally speaking, since the mobility of NMOS transistors (the mobility of electrons) is higher than the hole mobility in PMOS, NMOS conducts electricity better in the on state and can provide a more stable current. This makes NMOS a better current source choice in most cases, especially in applications where current size and stability are important.

3. Which is bigger, NMOS or PMOS?

Since the carriers of PMOS transistors are holes and their mobility is lower than that of electrons in NMOS transistors, in order to achieve the same current capability as NMOS, the size of PMOS transistors usually needs to be larger than that of NMOS. This means that the physical size of PMOS transistors is usually larger than that of NMOS transistors in the same manufacturing process.

4. Does PMOS have higher resistance than NMOS?

Yes, PMOS generally has higher resistance than NMOS. This is because the conductive carriers of PMOS transistors are holes, whose mobility is lower than electrons in NMOS. Low mobility results in higher resistance, which is why in many applications NMOS is preferred over PMOS if area and power dissipation permit.

About us

ALLELCO LIMITED

Read more

Quick inquiry

Please send an inquiry, we will respond immediately.

→ Previous

In the intricate world of electronic components, the potentiometer stands out for its versatility and precision in controlling various parameters within a circuit. This fundamental component, integral to both amateur and professional electronic setups, allows for the adjustment of resistance, thus i...

In this article, we explore the 555 timer, a seminal integrated circuit that revolutionized electronic devices upon its debut in 1971. This chip is known for its versatility and is used in everything from everyday household items to advanced spacecraft technology. We delve into the principles, struc...

→ Next

What Is the Function of a Potentiometer?

on May 8th

Mastering the 555 Timer: Principles, Modes, Applications, and Practical Implementation

on May 7th

Popular Posts

-

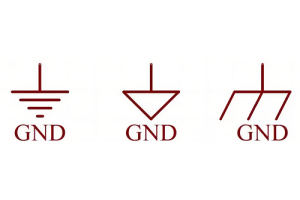

What is GND in the circuit?

on January 1th 3254

-

RJ-45 Connector Guide: RJ-45 Connector Color Codes, Wiring Schemes, R-J45 Applications, RJ-45 Datasheets

on January 1th 2801

-

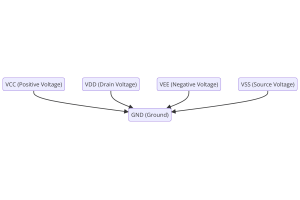

Understanding Power Supply Voltages in Electronics VCC, VDD, VEE, VSS, and GND

on November 19th 2608

-

Fiber Connector Types: SC Vs LC And LC Vs MTP

on January 1th 2250

-

Comparison Between DB9 and RS232

on January 1th 1867

-

What Is An LR44 Battery?

Electricity, that ubiquitous force, quietly permeates every aspect of our daily lives, from trivial gadgets to life-threatening medical equipment, it plays a silent role. However, truly grasping this energy, especially how to store and efficiently output it, is no easy task. It is against this background that this article will focus on a type of coin cell battery that may seem insignificant on the...on January 1th 1836

-

Understanding the Fundamentals:Inductance Resistance, andCapacitance

In the intricate dance of electrical engineering, a trio of fundamental elements takes center stage: inductance, resistance, and capacitance. Each bears unique traits that dictate the dynamic rhythms of electronic circuits. Here, we embark on a journey to decipher the complexities of these components, to uncover their distinct roles and practical uses within the vast electrical orchestra. Inductan...on January 1th 1791

-

What Is RF and Why Do We Use It?

Radio Frequency (RF) technology is a key part of modern wireless communication, enabling data transmission over long distances without physical connections. This article delves into the basics of RF, explaining how electromagnetic radiation (EMR) makes RF communication possible. We will explore the principles of EMR, the creation and control of RF signals, and their wide-ranging uses. The article ...on January 1th 1780

-

CR2430 Battery Comprehensive Guide: Specifications, Applications and Comparison to CR2032 Batteries

What is CR2430 battery ?Benefits of CR2430 BatteriesNormCR2430 Battery ApplicationsCR2430 EquivalentCR2430 VS CR2032Battery CR2430 SizeWhat to look for when buying the CR2430 and equivalentsData Sheet PDFFrequently Asked Questions Batteries are the heart of small electronic devices. Among the many types available, coin cells play a crucial role, commonly found in calculators, remote controls, and ...on January 1th 1775

-

Comprehensive guide to hFE in transistors

Transistors are crucial components in modern electronic devices, enabling signal amplification and control. This article delves into the knowledge surrounding hFE, including how to select a transistor's hFE value, how to find hFE, and the gain of different types of transistors. Through our exploration of hFE, we gain a deeper understanding of how transistors work and their role in electronic circu...on November 19th 1761