T Trigger Knowledge Guide - Pros and Cons, How It Works, Types

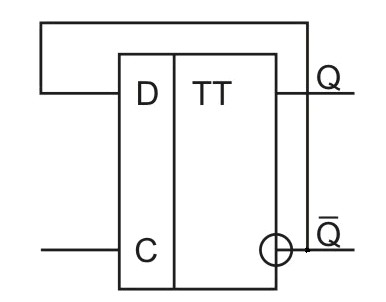

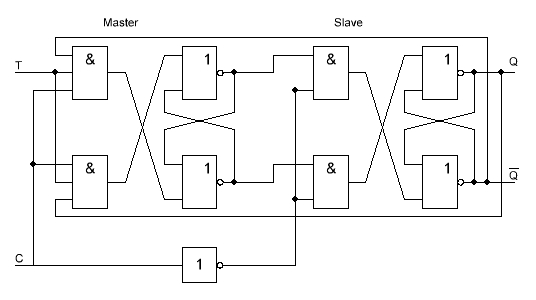

T-flip-flops are similar to JK flip-flops. By connecting the J and K inputs, one can derive a T flip-flop. Like a D flip-flop, it has only one external input along with a clock.

Catalog

How T-Flip-Flops Work

flip-flops are the simplest devices in digital automata, exhibiting two stable states. One state holds a value of “1” and the other a “0.” The state of the device and the binary information stored within it are determined by the output signals: direct and inverse. If a potential is set on the direct output corresponding to the logical output, the device is in a single-trigger state (the inverse output's potential corresponds to logical zero). If there is no potential on the direct output, the device is in the zero state.

Types of T-Flip-Flops

T-flip-flops primarily come in two varieties:

Asynchronous T-Trigger

Synchronous T-Trigger

Both types of T-flip-flops operate similarly. The only difference is in the process of transitioning from one state to another. The asynchronous type performs this transition directly, while the synchronous type operates based on this signal.

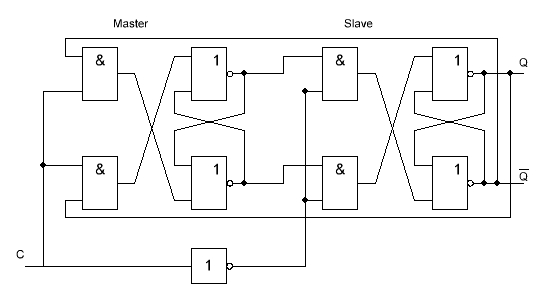

When evaluating a scenario where the clock input is always high (1), it's necessary to consider the two potential states of the toggle (T) input, either high (1) or low (0). Let’s detail the outcomes for each state and the logic gate interactions involved.

Case 1: T = 0

- Output condition: Here, both Gate1 and Gate2 are AND gates connected to T (set to 0).

- Gate1 and Gate2 output: Since an AND gate outputs 0 when any of its inputs are 0, the outputs of Gate1 and Gate2 will always be 0, regardless of their other inputs.

- Gate3/Q(n+1) logic: Gate3 is influenced by the output of Gate1. When Gate1 outputs 0, Gate3’s logic equation simplifies to NOT (0 OR NOT Q), resulting in Q.

- Gate4/Q(n+1)' logic: Gate4 follows a similar pattern, producing NOT (0 OR Q), simplifying to NOT Q or Q'.

Case 1 Summary:

- Assuming Gate1 = 0 and Gate2 = 0, and utilizing the characteristic of AND gates (any input of 0 results in an output of 0), the operation is straightforward:

- Gate3/Q(n+1) computes as Q, maintaining the current state.

- Gate4/Q(n+1)' results in Q', the complement of the current state.

Case 2: T = 1

- Output condition: When T is set to 1, the inputs of Gate1 and Gate2 now reflect the outputs of other logic operations, influencing their outputs.

- Gate1 and Gate2 output: Gate1 connects directly to the current state Q, and Gate2 to NOT Q or Q'.

- Gate4/Q(n+1)' logic: Here, the equation simplifies because the inputs of the AND gate are opposites (Q and NOT Q), resulting in 0.

- Gate3/Q(n+1) logic: On the other hand, Gate3 deals with NOT Q or Q', outputting NOT (Q AND 0), simplifying to NOT Q or Q'.

Case 2 Summary:

- The logic setup leads to interesting interactions:

- Gate1=Q, Gate2=Q', affecting subsequent logic processes.

- Gate4/Q(n+1)' directly computes as 0, since the AND operation between Q and NOT Q cannot be true.

- Gate3/Q(n+1) then computes as Q', which is the toggle from the previous state when T was 0.

T Flip-Flop Truth Table

|

CLK |

T |

Q(n+1) |

State |

|

|

0 |

Q |

NO CHANGE |

|

|

1 |

Q’ |

TOGGLE |

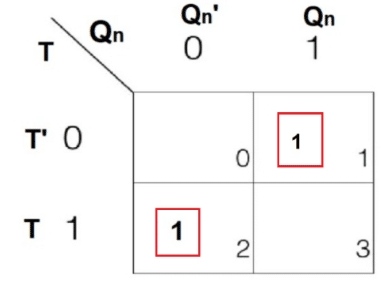

We will use this truth table to compile a characteristic table for the T flip-flop. In the truth table, you can see only one input T and one output Q(n+1). However, in the characteristic table, you will see two inputs T and Qn, and one output Q(n+1).

From the logic diagram above, it’s clear that Qn and Qn' are two complementary outputs, also acting as inputs for Gate3 and Gate4, therefore we consider Qn (i.e., the current state of the flip-flop) as an input, and Q(n+1) as the output for the next state.

After completing the characteristic table, we will construct a 2-variable K-map to derive the characteristic equation.

|

T |

Qn |

Q(n+1) |

|

0 |

0 |

0 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

From the K-map, you obtain two pairs. Solving both, we get the following characteristic equation:

Q(n+1) = TQn’ + T’Qn = T XOR Qn

Advantages of Using T-Flip-Flops

In digital circuits, T-flip-flops offer several significant benefits that simplify their function and integration:

- Single input simplicity: T-flip-flops have only one input, simplifying their operation. This single input can toggle between high and low states, allowing it to seamlessly integrate into circuit designs and easily connect with other digital circuits.

- No invalid states: T-flip-flops lack invalid states, helping to prevent unpredictable behavior in digital systems. This reliability is crucial for maintaining consistent system performance.

- Reduced power consumption: Compared to other flip-flops, T-flip-flops consume less power. This energy efficiency is beneficial for extending the battery life of portable devices and reducing the energy costs of large digital systems.

- Bistable operation: Like other flip-flops, T-flip-flops feature bistable operation, meaning they can indefinitely hold either state (0 or 1) until triggered by an input signal. This characteristic is essential for applications that require stable, long-term storage of single-bit data.

- Easy implementation: T-flip-flops can be easily implemented using basic logic gates. This simplicity makes them an economically viable choice for many digital systems, helping to reduce overall system costs.

Limitations of T-Flip-Flops

Despite these advantages, T-flip-flops also have some limitations that may affect their suitability for certain applications:

- Inverted output: The output of T-flip-flops is the opposite of its input, which can complicate the design of timing logic circuits and make the design more complex. Designers need to consider this to ensure correct circuit behavior.

- Limited functionality: T-flip-flops can only store one bit of information and are not capable of performing complex operations like addition or multiplication, limiting their use in basic memory tasks.

- Sensitivity to glitches: T-flip-flops may be sensitive to glitches and noise on the input signal, potentially causing unexpected state changes. This sensitivity can lead to unpredictable behavior in digital systems, especially in environments with high electronic interference.

- Propagation delay: Like all flip-flops, T-flip-flops encounter propagation delays, which may introduce timing issues in systems with strict timing constraints. These delays must be considered during system design to avoid timing errors and ensure reliable operation.

Applications

T-flip-flops are used in various real-world applications including:

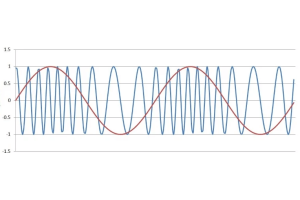

- Frequency division: T-flip-flops are often used to halve the frequency of a clock signal. By toggling the state of the flip-flop with each clock pulse, they effectively divide the frequency of the input signal by two, making them ideal for precise timing and digital clocks and frequency synthesizers.

- Frequency doubling: Conversely, T-flip-flops can also be used to double the frequency of a clock signal, known as frequency doubling. This is achieved by configuring the flip-flops in a setup that generates an output frequency twice that of the input signal.

- Data storage: T-flip-flops can be used as basic building blocks for storing single data bits, where data needs to be temporarily saved for further processing or transmission. This makes them very useful in applications such as shift registers and storage devices.

- Counters: Another significant application of T-flip-flops is creating binary counters. They can be interconnected with other digital logic gates to construct counters that can increment or decrement counting based on design requirements.

About us

ALLELCO LIMITED

Read more

Quick inquiry

Please send an inquiry, we will respond immediately.

→ Previous

Understanding your car's battery capacity and how it performs under a variety of conditions is important for any car owner, especially when faced with extreme weather challenges. The Cold Cranking Amps (CCA) rating is an indispensable measure for gauging a battery’s capability to start an engine in...

Exploring the dynamics of 1.5V batteries reveals not only their critical role in powering a diverse array of devices but also their rich historical and technological context. These batteries, which come in various forms such as AA, AAA, C, and D cells, have become indispensable in both everyday and ...

→ Next

How Much Do You Know About CCA?

on April 26th

1.5V Battery —— How Much Do You Know?

on April 25th

Popular Posts

-

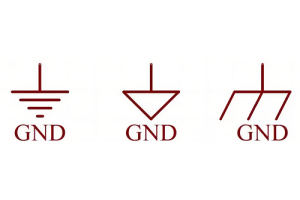

What is GND in the circuit?

on January 1th 3272

-

RJ-45 Connector Guide: RJ-45 Connector Color Codes, Wiring Schemes, R-J45 Applications, RJ-45 Datasheets

on January 1th 2815

-

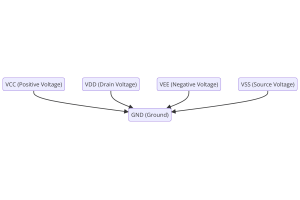

Understanding Power Supply Voltages in Electronics VCC, VDD, VEE, VSS, and GND

on November 20th 2640

-

Fiber Connector Types: SC Vs LC And LC Vs MTP

on January 1th 2265

-

Comparison Between DB9 and RS232

on January 1th 1882

-

What Is An LR44 Battery?

Electricity, that ubiquitous force, quietly permeates every aspect of our daily lives, from trivial gadgets to life-threatening medical equipment, it plays a silent role. However, truly grasping this energy, especially how to store and efficiently output it, is no easy task. It is against this background that this article will focus on a type of coin cell battery that may seem insignificant on the...on January 1th 1846

-

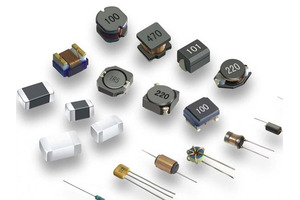

Understanding the Fundamentals:Inductance Resistance, andCapacitance

In the intricate dance of electrical engineering, a trio of fundamental elements takes center stage: inductance, resistance, and capacitance. Each bears unique traits that dictate the dynamic rhythms of electronic circuits. Here, we embark on a journey to decipher the complexities of these components, to uncover their distinct roles and practical uses within the vast electrical orchestra. Inductan...on January 1th 1808

-

What Is RF and Why Do We Use It?

Radio Frequency (RF) technology is a key part of modern wireless communication, enabling data transmission over long distances without physical connections. This article delves into the basics of RF, explaining how electromagnetic radiation (EMR) makes RF communication possible. We will explore the principles of EMR, the creation and control of RF signals, and their wide-ranging uses. The article ...on January 1th 1801

-

CR2430 Battery Comprehensive Guide: Specifications, Applications and Comparison to CR2032 Batteries

What is CR2430 battery ?Benefits of CR2430 BatteriesNormCR2430 Battery ApplicationsCR2430 EquivalentCR2430 VS CR2032Battery CR2430 SizeWhat to look for when buying the CR2430 and equivalentsData Sheet PDFFrequently Asked Questions Batteries are the heart of small electronic devices. Among the many types available, coin cells play a crucial role, commonly found in calculators, remote controls, and ...on January 1th 1799

-

Comprehensive guide to hFE in transistors

Transistors are crucial components in modern electronic devices, enabling signal amplification and control. This article delves into the knowledge surrounding hFE, including how to select a transistor's hFE value, how to find hFE, and the gain of different types of transistors. Through our exploration of hFE, we gain a deeper understanding of how transistors work and their role in electronic circu...on November 20th 1782