LM97937

www.ti.com

# LM97937 Dual 370 MSPS Receiver and Feedback IC With SNRBoost, Bit-Burst, and JESD204B Outputs

Check for Samples: LM97937

### FEATURES

- Conversion Rate: 370 MSPS

- 1.7 V<sub>P-P</sub> Input Full Scale Range

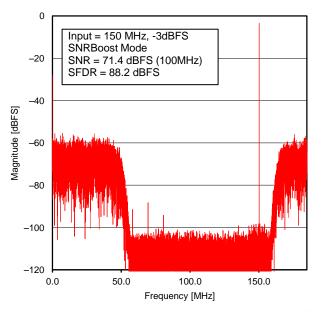

- SNRBoost Noise Shaping with 100 MHz Bandpass Bandwidth

- Noise Spectral Density: -152.0 dBFS/Hz

- Programmable Passband Center Frequency

- Bit-Burst Resolution Switching

- Resolutions: 9-bit (Low-Res), 14-bit (Hi-Res)

- Hi-Res Noise Density: -152.7 dBFS/Hz

- Programmable Burst Configurations

- Performance

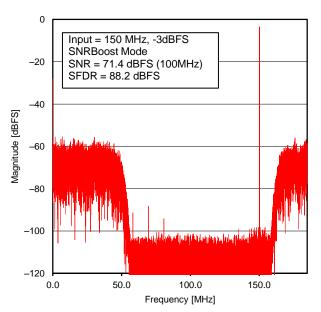

- Input: 150 MHz, -3 dBFS

- SNR (SNRBoost): 71.6 dBFS

- SNR (Bit-Burst): 69.6 dBFS

- SFDR: 88 dBFS

- non-HD2/HD3 SPUR: -90 dBFS

- Power Dissipation: 876 mW/channel

- Buffered Analog Inputs

- On-chip Precision Reference Without External Bypassing

- Input Sampling Clock Divider with Phase Synchronization (Divide-by- 1, 2, 4 or 8)

- JESD204B Subclass 1 Serial Data Interface

- Lane Rates up to 7.4 Gb/s

- Configurable as 1- or 2-lanes/channel

- Fast Over-range Signals

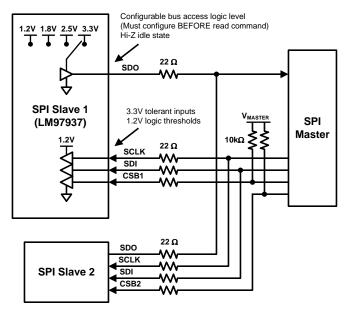

- 4-wire, 1.2 V, 1.8 V, 2.5V or 3.3V Compatible SPI

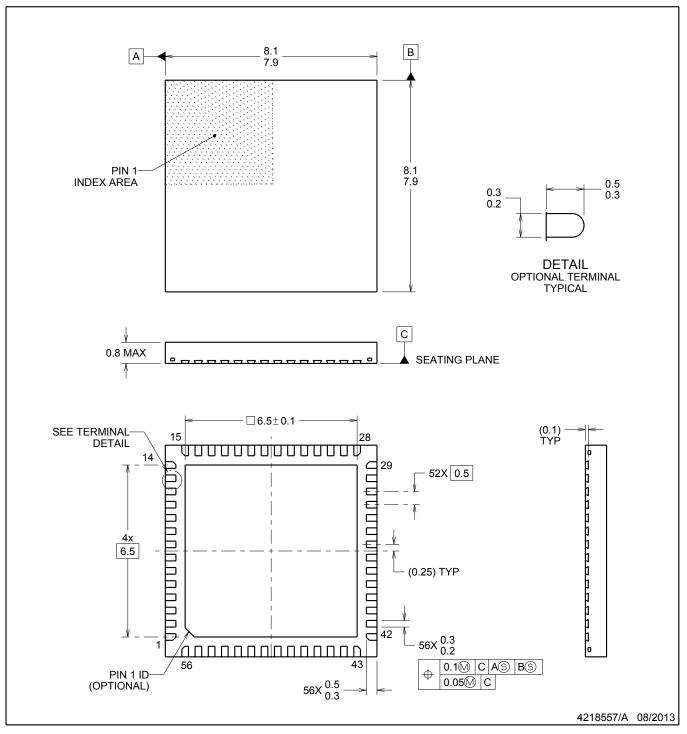

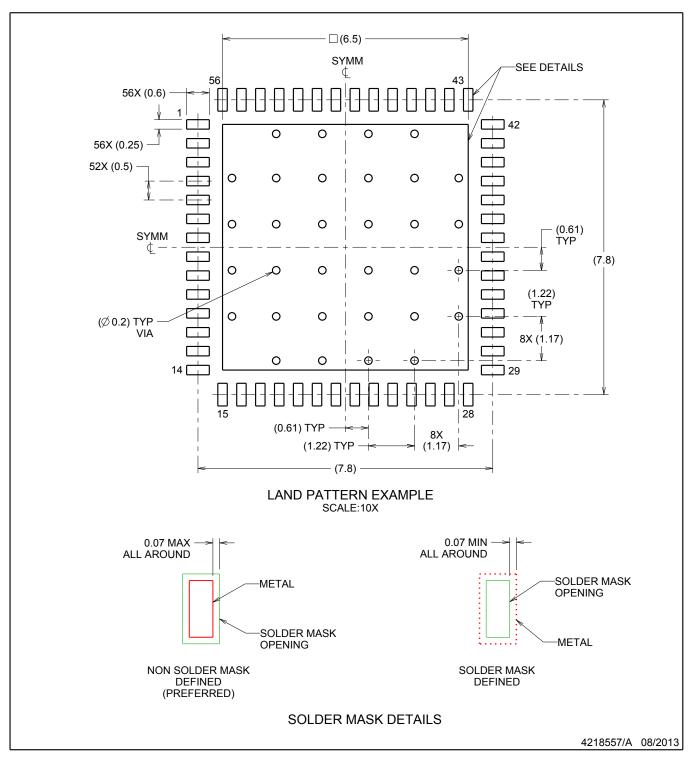

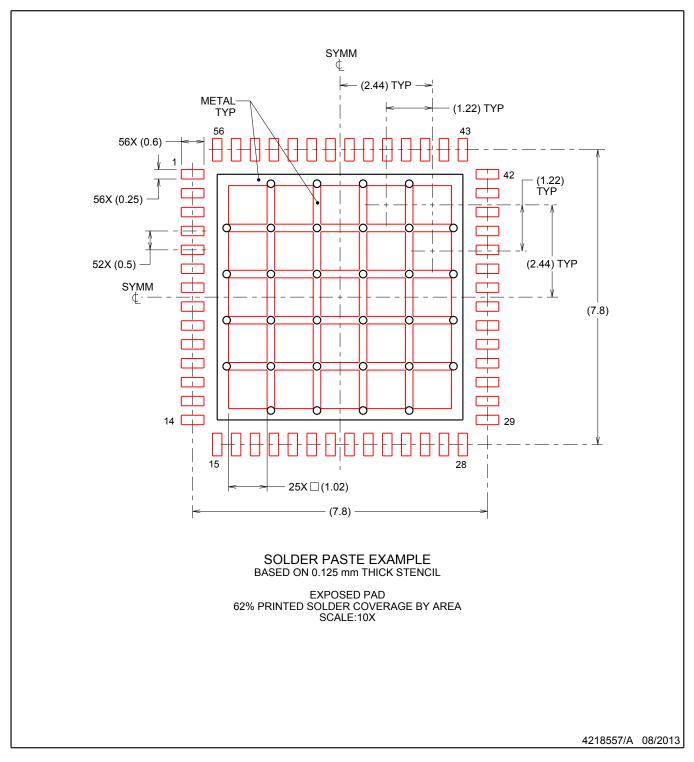

- 56-pin QFN Package, (8 x 8 mm, 0.5mm pinpitch)

### APPLICATIONS

- High IF Sampling Receivers

- Multi-Carrier Base Station Receivers

- GSM/EDGE, CDMA2000, UMTS, LTE, and WiMax

- Diversity, Multi-Mode and Multiband Receivers

- Digital Pre-Distortion

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

### DESCRIPTION

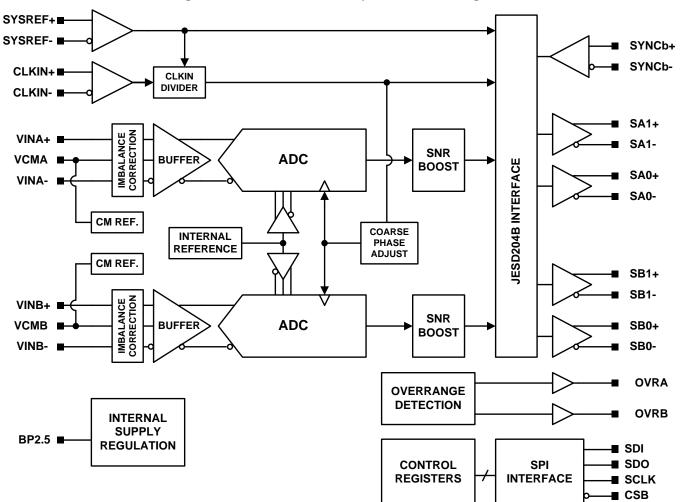

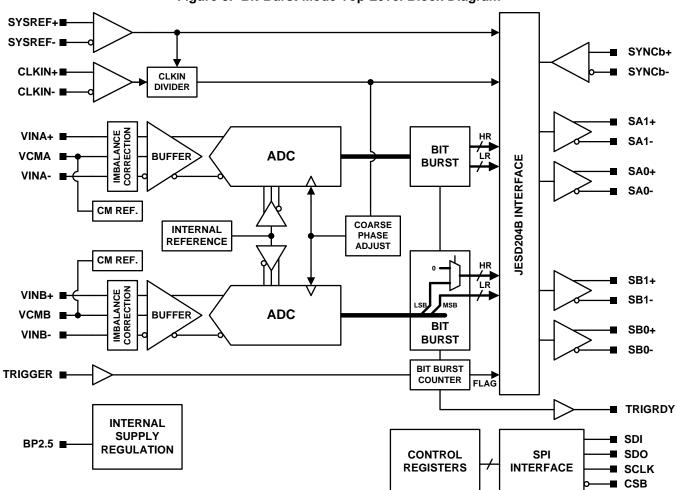

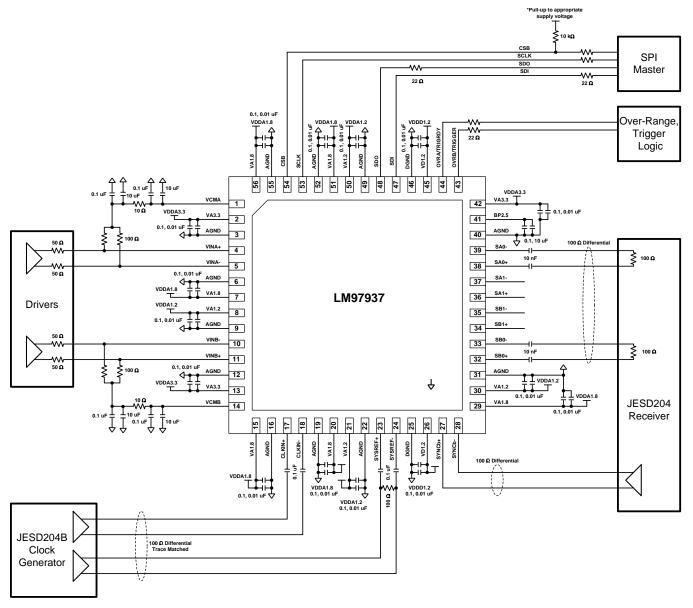

The LM97937 device is a dual-channel 370 MSPS analog-to-digital converter (ADC) with JESD204B interface operating up to 7.4 Gb/s. SNRBoost technology with bandpass spectral shaping improves the noise density at the intermediate frequency and Bit-Burst technology provides temporary and periodic resolution enhancement. The integrated input buffer reduces charge kick-back noise and eases the system level design of the driving amplifier, antialiasing filter and impedance matching. An input sampling clock divider provides integer divide ratios with configurable phase selection to simplify system clocking. The device comes in a 56-pin, 8-mm × 8-mm QFN package.

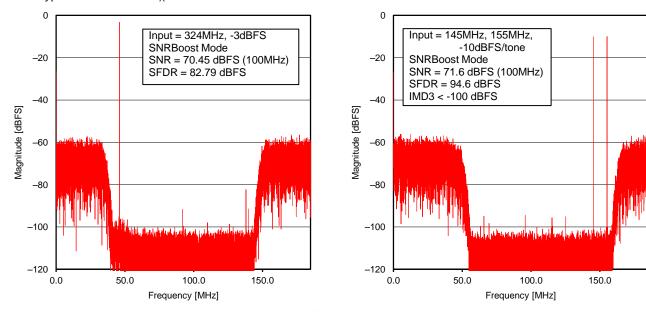

Figure 1. 1-Tone Spectrum, SNRBoost Mode, 150 MHz

SNVS990A – DECEMBER 2013 – REVISED JANUARY 2014

#### Figure 2. SNRBoost Mode Top Level Block Diagram

**Block Diagrams**

www.ti.com

SNVS990A - DECEMBER 2013 - REVISED JANUARY 2014

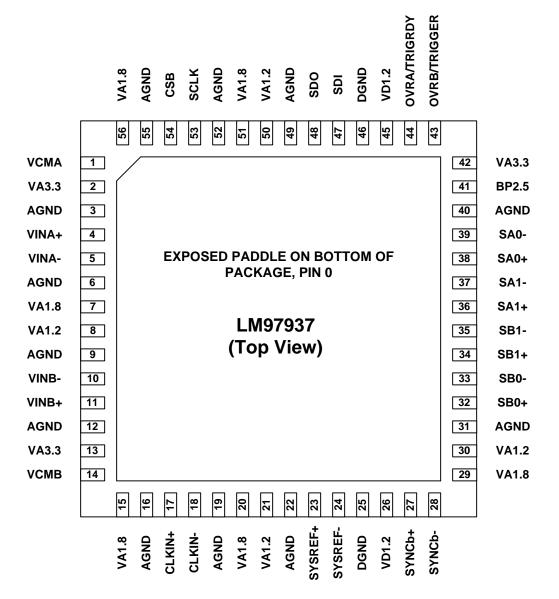

**PIN DIAGRAM**

#### SNVS990A – DECEMBER 2013 – REVISED JANUARY 2014

www.ti.com

### **PIN DESCRIPTION**

| PIN   | NAME             | TYPE/DIAGRAM      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

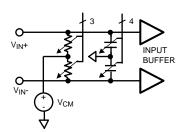

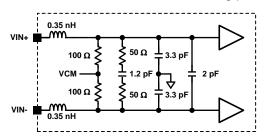

| 4,5   | VINA+, VINA-     | V <sub>A3.3</sub> | Differential analog input pins of channel A.<br>Each input pin is terminated to the internal<br>common mode reference with a resistor for<br>an internal differential termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11,10 | VINB+, VINB-     |                   | Differential analog input pins of channel B.<br>Each input pin is terminated to the internal<br>common mode reference with a resistor for<br>an internal differential termination.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1,14  | VCMA, VCMB       |                   | Input interface common mode voltage for channels A and B.<br>These pins must be bypassed to AGND with low ESL (equivalent series inductance) 0.1 $\mu$ F capacitors. One should be placed as close to the pin as possible and additional capacitors placed at the bias load points. 10 $\mu$ F capacitors should also be placed in parallel. It is recommended to use VCMA and VCMB to provide the common mode voltage for the differential analog inputs. The input common mode bias is provided internally for the ADC input, therefore external use of VCMA and VCMB is recommended but not strictly required. The recommended bypass capacitors are always required. |

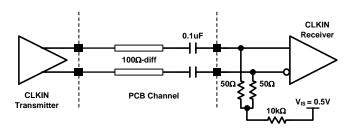

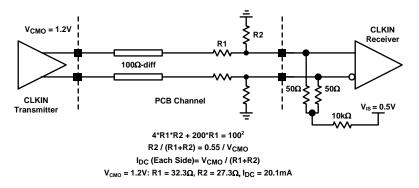

| 17,18 | CLKIN+, CLKIN–   |                   | Differential device clock input pins.<br>Each pin is internally terminated to a DC bias with a 50 $\Omega$ resistor for a 100 $\Omega$ total internal differential termination. AC coupling is required for coupling the clock input to these pins if the clock driver cannot meet the common-mode requirements. Sampling occurs on the rising edge of the differential signal (CLKIN+) – (CLKIN–).                                                                                                                                                                                                                                                                      |

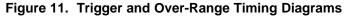

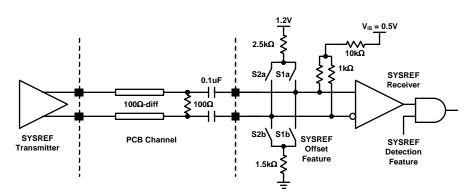

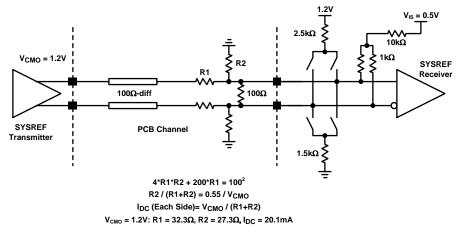

| 23,24 | SYSREF+, SYSREF- | SYSREF+           | Differential SYSREF signal input pins.<br>Each pin is internally terminated to a DC bias with a 1 k $\Omega$ resistor. An external 100 $\Omega$ differential termination must always be provided. AC coupling using capacitors is required for coupling the SYSREF signal to these pins if the clock driver cannot meet the common-mode requirements. In the case of AC coupling, the termination must be placed on the source side of the coupling capacitors.                                                                                                                                                                                                          |

### LM97937

SNVS990A - DECEMBER 2013 - REVISED JANUARY 2014

www.ti.com

| PIN            | NAME                   | TYPE/DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

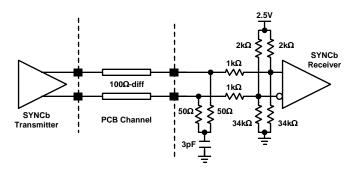

| 27, 28         | SYNCb+, SYNCb-         | V <sub>A3.3</sub><br>SYNC+<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.3<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3.4<br>VA3 | Differential SYNCb signal input pins.<br>DC coupling is required for coupling the<br>SYNCb signal to these pins. Each pin is<br>internally terminated to the DC bias with a<br>large resistor. An internal 100 $\Omega$ differential<br>termination is provided therefore an external<br>termination is not required. Additional<br>resistive components in the input structure<br>give the SYNCb input a wide input common-<br>mode range. The SYNCb signal is active low<br>and is therefore asserted when the voltage<br>at SYNCb+ is less than at SYNCb |

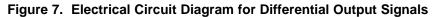

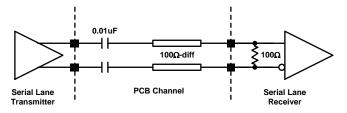

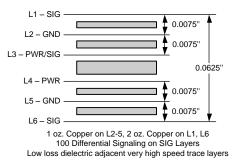

| 38, 39, 36, 37 | SA0+, SA0–, SA1+, SA1– |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Differential high speed serial data lane pins<br>for channel A.<br>These pins must be AC coupled to the<br>receiving device. The differential trace<br>routing from these pins must maintain a<br>$100\Omega$ characteristic impedance. In single-<br>lane mode, SA0 +/- is utilized to transfer<br>data and SA1+/- is undefined and may be<br>left floating.                                                                                                                                                                                               |

| 32, 33, 34, 35 | SB0+, SB0–, SB1+, SB1– |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Differential high speed serial data lane pins<br>for channel B. These pins must be AC<br>coupled to the receiving device. The<br>differential trace routing from these pins<br>must maintain a $100\Omega$ characteristic<br>impedance. In single-lane mode, SB0+/- is<br>utilized to transfer data and SB1+/- is<br>undefined and may be left floating.                                                                                                                                                                                                    |

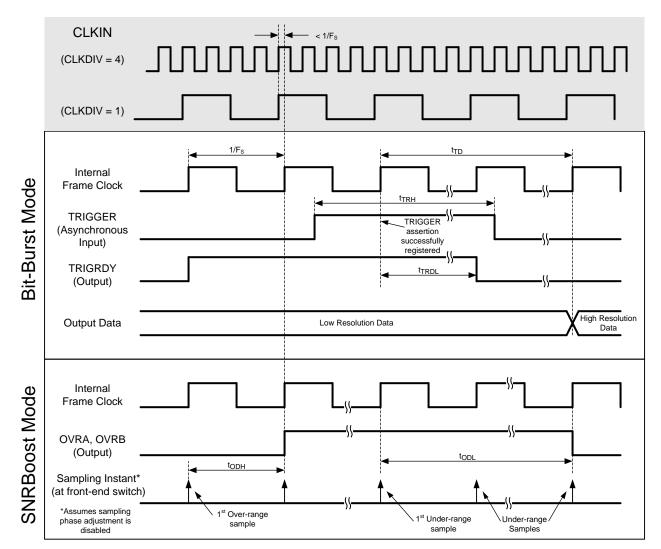

| 44             | OVRA/ TRIGRDY          | VA1.8 VA3.3<br>800<br>800<br>800<br>VRAV<br>TRIGRDY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Dual purpose pin.<br>While in SNRBoost mode, this pin outputs<br>the channel A over-range signal.<br>While in Bit-Burst mode and in Trigger sub-<br>mode, this pin outputs the "trigger ready"<br>signal that indicates when a Bit-Burst cycle<br>has completed and a new trigger edge may<br>be applied. This pin is a 1.8 V CMOS logic<br>level output.                                                                                                                                                                                                   |

| 43             | OVRB/ TRIGGER          | VA1.8<br>VA1.8<br>VA1.8<br>VA1.8<br>VA1.8<br>VA1.8<br>VA1.8<br>VA1.8<br>VA1.8<br>VA1.8<br>VA3.3<br>OVRB/<br>TRIGGER<br>VA3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Dual purpose pin.<br>While in SNRBoost mode, this pin outputs<br>the channel B over-range signal. In this<br>mode, the pin is a 1.8 V CMOS logic level<br>output.<br>While in Bit-Burst mode and Trigger sub-<br>mode, this pin is the "trigger" signal that is<br>used to start a new Bit-Burst cycle when a<br>rising edge is applied. In this mode, the pin<br>is a 1.8 V CMOS logic level asynchronous<br>input.                                                                                                                                        |

SNVS990A - DECEMBER 2013 - REVISED JANUARY 2014

| PIN                                            | NAME  | TYPE/DIAGRAM     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------------------|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

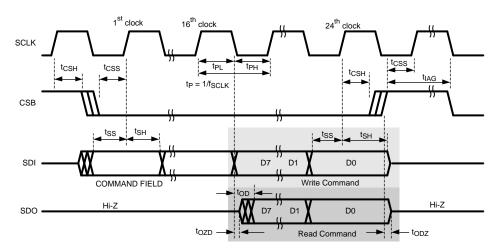

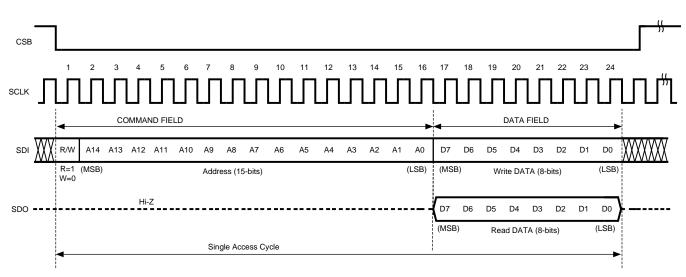

| 53                                             | SCLK  |                  | SPI Interface Serial Clock pin.<br>Serial data is shifted into and out of the device synchronous with this clock signal.<br>Compatible with $1.2 - 3.3$ V CMOS logic levels.                                                                                                                                                                                                                                                                                             |

| 54                                             | CSB   | VA3.3 VA1.2      | SPI Interface Chip Select pin.<br>When this signal is asserted, SCLK is used<br>to clock the input serial data on the SDI pin<br>or output serial data on the SDO pin. When<br>this signal is de-asserted, the SDO pin is<br>high impedance and the input data is<br>ignored. Active low. A 10 k $\Omega$ pull-up resistor<br>to the VA1.8 supply is recommended to<br>prevent undesired activation of the SPI bus.<br>Compatible with 1.2 – 3.3 V CMOS logic<br>levels. |

| 47                                             | SDI   |                  | SPI Interface Data Input pin.<br>Serial data is shifted into the device on this<br>pin while the CSB signal is asserted.<br>Compatible with $1.2 - 3.3$ V CMOS logic<br>levels.                                                                                                                                                                                                                                                                                          |

| 48                                             | SDO   |                  | SPI Interface Data Output pin.<br>Serial data is shifted out of the device on<br>this pin during a read command while CSB<br>is asserted. The output logic level is<br>configurable as 1.2 V, 1.8 V, 2.5 V or 3.3 V.<br>The output level MUST be configured after<br>power up and before performing a read<br>command. See the Register Map for<br>configuration details.                                                                                                |

| 2, 13, 42                                      | VA3.3 | Supply Input Pin | 3.3 V Analog Power Supply pin.<br>This pin must be connected to a quiet<br>source and decoupled to AGND with a 0.1<br>$\mu$ F and a 0.01 $\mu$ F capacitor located close to<br>the pin.                                                                                                                                                                                                                                                                                  |

| 7, 15, 20, 29, 51, 56                          | VA1.8 | Supply Input Pin | 1.8 V Analog Power Supply pins.<br>These pins must be connected to a quiet source and decoupled to AGND with a 0.1 $\mu$ F and a 0.01 $\mu$ F capacitor located close to each pin.                                                                                                                                                                                                                                                                                       |

| 8, 21, 30, 50                                  | VA1.2 | Supply Input Pin | 1.2 V Analog Power Supply pins.<br>These pins must be connected to a quiet source and decoupled to AGND with a 0.1 $\mu$ F and a 0.01 $\mu$ F capacitor located close to each pin.                                                                                                                                                                                                                                                                                       |

| 26, 45                                         | VD1.2 | Supply Input Pin | 1.2 V Digital Power Supply pin.<br>This pin must be connected to a quiet source and decoupled to AGND with a 0.1 $\mu$ F and a 0.01 $\mu$ F capacitor located close to each pin.                                                                                                                                                                                                                                                                                         |

| 41                                             | BP2.5 | Bypass Pins      | Capacitive Bypassing pin for internally regulated 2.5 V supply. This pin must be decoupled to AGND with a 0.1 $\mu$ F and a 10 uF capacitor located close to the pin.                                                                                                                                                                                                                                                                                                    |

| 3, 6, 9, 12, 16, 19, 22,<br>31, 40, 49, 52, 55 | AGND  | Analog Ground    | Analog Ground.<br>Must be connected to a solid ground<br>reference plane under the device.                                                                                                                                                                                                                                                                                                                                                                               |

SNVS990A – DECEMBER 2013–REVISED JANUARY 2014

www.ti.com

| PIN    | NAME | TYPE/DIAGRAM        | DESCRIPTION                                                                                                                                                                                                                                             |

|--------|------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25, 46 | DGND | Digital Ground      | Digital Ground.<br>Must be connected to the same solid ground<br>reference plane under the device to which<br>AGND connects. Bypass capacitors<br>connected to the VD1.2 pins must be<br>connected to ground as close to this DGND<br>pins as possible. |

| 0      |      | Exposed Thermal Pad | Exposed Thermal Pad.<br>The exposed pad must be connected to the<br>AGND ground plane electrically and with<br>good thermal dissipation properties to<br>ensure rated performance.                                                                      |

### **ABSOLUTE MAXIMUM RATINGS**

Absolute maximum ratings are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits.

|                                        |                                                             |                        | VALUE                                        | UNIT |

|----------------------------------------|-------------------------------------------------------------|------------------------|----------------------------------------------|------|

|                                        |                                                             | MIN                    | MAX                                          |      |

| Supply Voltage: V <sub>A3.3</sub>      |                                                             | -0.3                   | 4.2                                          | V    |

| Supply Voltage: VA1.8                  |                                                             | -0.3                   | 2.35                                         | V    |

| Supply Voltage: VA1.2, V               | / <sub>D1.2</sub>                                           | -0.3                   | 1.55                                         | V    |

| Voltage at VINA+, VINA                 | <b>-</b>                                                    | V <sub>CMA</sub> – 1.0 | V <sub>CMA</sub> + 0.75                      | V    |

| Voltage at VINB+, VINE                 | 3-                                                          | V <sub>CMB</sub> – 1.0 | V <sub>CMB</sub> + 0.75                      | V    |

| Voltage at VCMA, VCM                   | В                                                           | -0.3                   | V <sub>A3.3</sub> + 0.3, not to exceed 4.2 V | V    |

| Voltage at OVRA /TRIG                  | RDY, ORVB/TRIGGER                                           | -0.3                   | V <sub>A1.8</sub> + 0.3                      | V    |

| Voltage at SCLK, SDI, 0                | CSb                                                         | -0.3                   | V <sub>A3.3</sub> + 0.3, not to exceed 4.2 V | V    |

| Voltage at SDO                         |                                                             | -0.3                   | V <sub>SPI</sub> + 0.3, not to exceed 4.2 V  | V    |

| Voltage at CLKIN+, CLł                 | (IN-, SYSREF+, SYSREF-                                      | -0.3                   | 1.55                                         | V    |

| Voltage at SYNC+, SYN                  | IC-                                                         | -0.3                   | V <sub>BP2.5</sub> + 0.3                     | V    |

| Voltage at BP2.5                       |                                                             | -0.3                   | 3.2                                          | V    |

| Voltage at SA0+, SA0-,<br>SB1-         | SA1+, SA1–, SB0+, SB0–, SB1+,                               | -0.3                   | V <sub>BP2.5</sub> + 0.3                     | V    |

| Input Current at any Pir               | 1(1)                                                        |                        | 5                                            | mA   |

| Junction Temperature (T <sub>J</sub> ) | Maximum rated operating junction temperature <sup>(2)</sup> | +125                   |                                              | °C   |

|                                        | Recommended long-term operating junction temperature        |                        | +105                                         | °C   |

| Storage Temperature R                  | ange                                                        | -65                    | +150                                         | °C   |

| ESD Rating                             | Human Body Model                                            |                        | 1000                                         | V    |

|                                        | Charged Device Model                                        |                        | 250                                          | V    |

(1) When the input voltage at any pin exceeds the VA3.3 power supply (that is V<sub>IN</sub> > V<sub>A3.3</sub> or V<sub>IN</sub> < AGND) the current at that pin should be limited to +/-5mA. The +/-50mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of +/-5mA to 10 pins.</p>

(2) Prolonged use at this temperature may increase the device failure-in-time (FIT) rate.

SNVS990A - DECEMBER 2013 - REVISED JANUARY 2014

www.ti.com

#### THERMAL INFORMATION

|                      | THERMAL METRIC <sup>(1)</sup>                    | NOMINAL<br>VALUE | UNIT |

|----------------------|--------------------------------------------------|------------------|------|

| $\theta_{JA}$        | Thermal Resistance, Junction–Ambient             | 24.9             | °C/W |

| θ <sub>JC</sub> –Top | Thermal Resistance, Junction–Package Top         | 8.6              | °C/W |

| $\theta_{JB}$        | Thermal Resistance, Junction–Board               | 3.0              | °C/W |

| PSI <sub>JT</sub>    | Characterization parameter, Junction-Package Top | 0.2              | °C/W |

| PSIJB                | Characterization parameter, Junction-Board       | 2.9              | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953

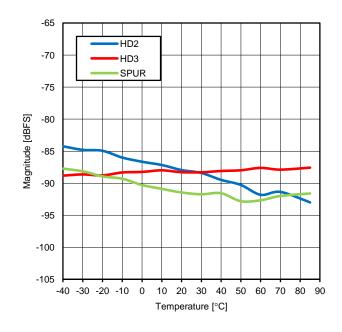

### **RECOMMENDED OPERATING CONDITIONS**

Operating Ratings indicate conditions for which the device is guaranteed to be functional, but do not guarantee specific performance limits. Guaranteed specifications and test conditions are specified in the Electrical Characteristics section. Operation of the device beyond the Operating Ratings is not recommended as it may degrade the device lifetime.

|                                                       | MIN  | MAX  | UNITS |

|-------------------------------------------------------|------|------|-------|

| Specified Temperature Range                           | -40  | 85   | °C    |

| 3.3 V Analog Supply Voltage Range: V <sub>A3.3</sub>  | 2.85 | 3.45 | V     |

| 1.8 V Analog Supply Voltage Range: V <sub>A1.8</sub>  | 1.7  | 1.9  | V     |

| 1.2 V Analog Supply Voltage Range: V <sub>A1.2</sub>  | 1.15 | 1.25 | V     |

| 1.2 V Digital Supply Voltage Range: V <sub>D1.2</sub> | 1.15 | 1.25 | V     |

| CLKIN Duty Cycle                                      | 30   | 70   | %     |

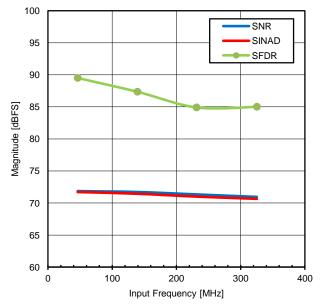

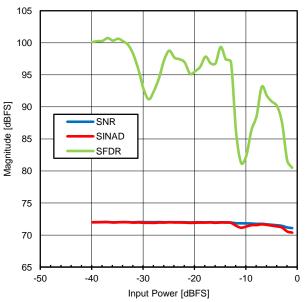

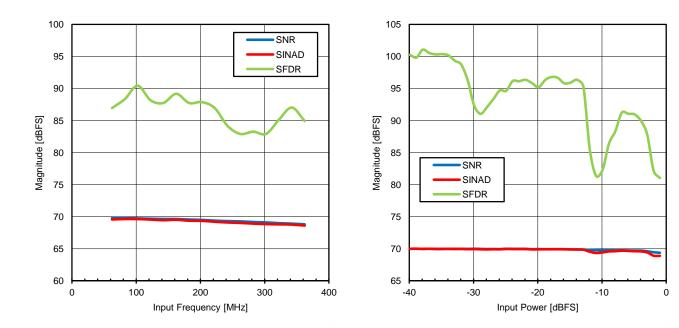

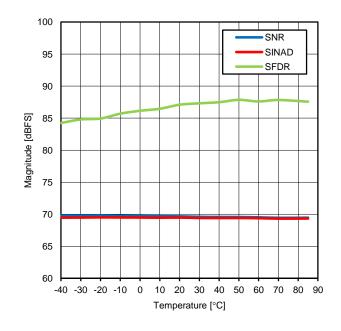

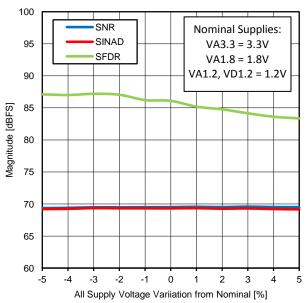

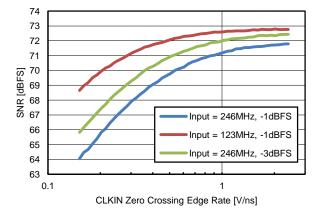

### **Converter Dynamic Performance Characteristics (SNRBoost Mode)**

Unless otherwise noted, these specifications apply for  $V_{A3.3}$ = 3.1 V;  $V_{A1.8}$  = 1.8 V;  $V_{A1.2}$  =  $V_{D1.2}$  = 1.2 V;  $F_{CLKIN}$  =  $F_{S}$  = 370 MSPS; SNRBoost Mode,  $F_{C}$ =0.25\* $F_{S}$ ; external differential resistive termination at ADC input is 66  $\Omega$ . Typical values are at  $T_{A}$  =+25°C. **Boldface limits** apply for  $T_{A}$  =  $T_{MIN}$  to  $T_{MAX}$ . All other limits apply at  $T_{A}$  =+25°C, unless otherwise noted.

| PARAMETER | DESCRIPTION / CONDITIONS                                                           | TYP    | LIMIT  | UNITS   |  |

|-----------|------------------------------------------------------------------------------------|--------|--------|---------|--|

|           | Signal to Noise Ratio Noise, integrated across 100 MHz SNRBoost Bandwidth          |        |        |         |  |

|           | Input = 46 MHz, -3 dBFS                                                            | 71.9   |        |         |  |

| SNR       | Input = 150 MHz, -3 dBFS, SNRBoost F <sub>C</sub> =0.29*F <sub>S</sub>             | 71.6   | 71.3   | dBFS    |  |

|           | Input = 231 MHz, -3 dBFS                                                           | 71.4   |        |         |  |

|           | Input = 325MHz, -3 dBFS                                                            | 71.0   |        |         |  |

|           | Input = 325MHz, -40 dBFS                                                           | 72.0   |        |         |  |

|           | Signal to Noise and Distortion Ratio, integrated across 100 MHz SNRBoost bandwidth |        |        |         |  |

|           | Input = 46 MHz, -3 dBFS                                                            | 71.7   |        |         |  |

| SINAD     | Input = 150 MHz, -3 dBFS, SNRBoost F <sub>C</sub> =0.29*F <sub>S</sub>             | 71.2   |        | dBFS    |  |

|           | Input = 231 MHz, -3 dBFS                                                           | 71.0   |        |         |  |

|           | Input = 325MHz, -3 dBFS                                                            | 70.6   |        |         |  |

|           | Input = 325MHz, -40 dBFS                                                           | 72.0   |        |         |  |

|           | Noise Spectral Density, average NSD across 100MHz SNRBoost bandwidth               |        |        |         |  |

|           | Input = 46 MHz, -3 dBFS                                                            | -151.9 |        |         |  |

| NSD       | Input = 150 MHz, -3 dBFS, SNRBoost F <sub>C</sub> =0.29*F <sub>S</sub>             | -151.6 | -151.3 |         |  |

|           | Input = 231 MHz, -3 dBFS                                                           | -151.4 |        | dBFS/Hz |  |

|           | Input = 325MHz, -3 dBFS                                                            | -151.0 |        | 1       |  |

|           | Input = 325MHz, -40 dBFS                                                           | -152.0 |        | 1       |  |

EXAS STRUMENTS

www.ti.com

SNVS990A - DECEMBER 2013 - REVISED JANUARY 2014

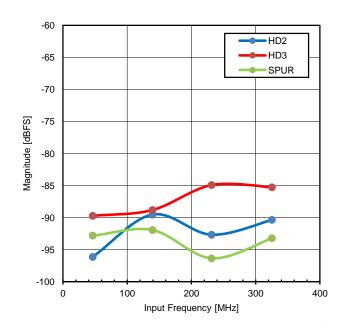

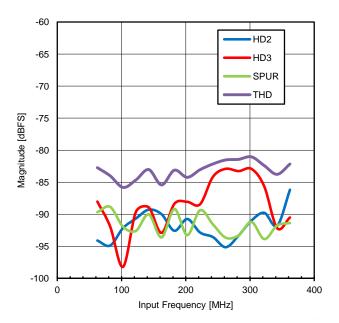

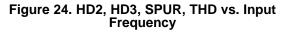

### Converter Dynamic Performance Characteristics (SNRBoost Mode) (continued)

Unless otherwise noted, these specifications apply for  $V_{A3.3}$ = 3.1 V;  $V_{A1.8}$  = 1.8 V;  $V_{A1.2}$  =  $V_{D1.2}$  = 1.2 V;  $F_{CLKIN}$  =  $F_{S}$  = 370 MSPS; SNRBoost Mode,  $F_{C}$ =0.25\* $F_{S}$ ; external differential resistive termination at ADC input is 66  $\Omega$ . Typical values are at  $T_{A}$ =+25°C. Boldface limits apply for T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>. All other limits apply at T<sub>A</sub> =+25°C, unless otherwise noted.

| PARAMETER | DESCRIPTION / CONDITIONS                                                             | TYP   | LIMIT | UNITS |  |

|-----------|--------------------------------------------------------------------------------------|-------|-------|-------|--|

|           | Single-tone Spurious Free Dynamic Range Measured across 100MHz<br>SNRBoost Bandwidth |       |       |       |  |

|           | Input = 46 MHz, -3 dBFS                                                              | 88.0  |       |       |  |

| SFDR      | Input = 150 MHz, $-3$ dBFS, SNRBoost F <sub>C</sub> =0.29*F <sub>S</sub>             | 88.0  | 80.0  | dBFS  |  |

|           | Input = 231 MHz, -3 dBFS                                                             | 85.0  |       |       |  |

|           | Input = 325MHz, -3 dBFS                                                              | 85.0  |       |       |  |

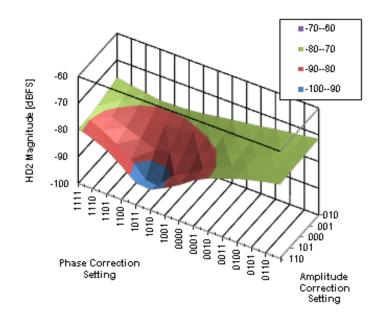

|           | 2 <sup>nd</sup> Order Harmonic Distortion                                            |       |       |       |  |

|           | Input = 46 MHz, -3 dBFS                                                              | -93.0 |       |       |  |

| HD2       | Input = 150 MHz, $-3$ dBFS, SNRBoost F <sub>C</sub> =0.29*F <sub>S</sub>             | -89.0 | -80.0 | dBFS  |  |

|           | Input = 231 MHz, -3 dBFS                                                             | -90.0 |       |       |  |

|           | Input = 325MHz, -3 dBFS                                                              | -89.0 |       |       |  |

|           | 3 <sup>rd</sup> Order Harmonic Distortion                                            |       |       |       |  |

|           | Input = 46 MHz, -3 dBFS                                                              | -88.0 |       |       |  |

| HD3       | Input = 150 MHz, -3 dBFS                                                             | -88.0 | -81.0 | dBFS  |  |

|           | Input = 231 MHz, -3 dBFS                                                             | -85.0 |       |       |  |

|           | Input = 325MHz, -3 dBFS                                                              | -85.0 |       |       |  |

|           | Largest spurious tone, not including DC, HD2 or HD3                                  |       |       |       |  |

|           | Input = 46 MHz, -3 dBFS                                                              | -90.0 |       |       |  |

| SPUR      | Input = 150 MHz, -3 dBFS                                                             | -90.0 | -88.0 | dBFS  |  |

|           | Input = 231 MHz, -3 dBFS                                                             | -90.0 |       |       |  |

|           | Input = 325MHz, -3 dBFS                                                              | -90.0 |       |       |  |

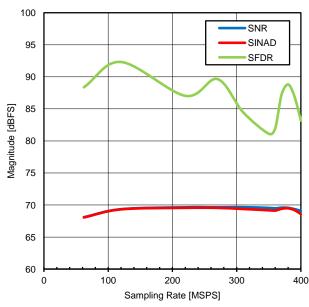

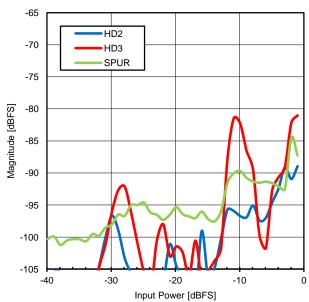

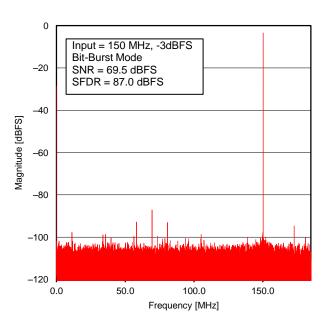

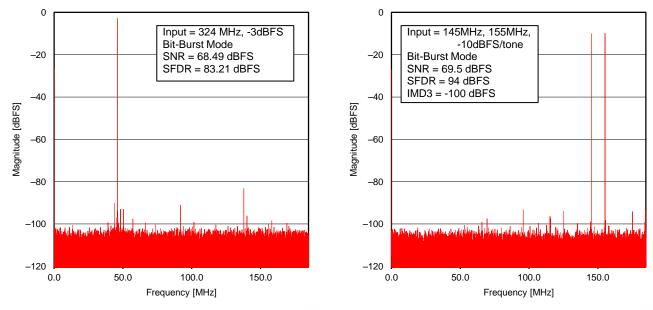

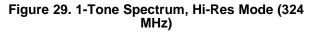

### **Converter Dynamic Performance Characteristics (Bit-Burst Mode)**

Unless otherwise noted, these specifications apply for  $V_{A3.3} = 3.1$  V;  $V_{A1.8} = 1.8$  V;  $V_{A1.2} = V_{D1.2} = 1.2$  V;  $F_{CLKIN} = F_S = 370$ MSPS; device configured for Bit-Burst Mode, 14-bit High-Resolution; external differential resistive termination at ADC input is 66 Ω. Typical values are at  $T_A = +25$ °C. Boldface limits apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ . All other limits apply at  $T_A = +25$ °C, unless otherwise noted.

| PARAMETER | DESCRIPTION / CONDITIONS                                                                           | TYP  | LIMIT | UNITS |

|-----------|----------------------------------------------------------------------------------------------------|------|-------|-------|

|           | Signal to Noise Ratio, integrated across entire Nyquist bandwidth, Low Resolution Bit-Burst phase  |      |       |       |

|           | Input = 325 MHz, Ain = -3 dBFS                                                                     | 58.4 |       |       |

|           | Signal to Noise Ratio, integrated across entire Nyquist Bandwidth, High Resolution Bit-Burst phase |      |       |       |

| SNR       | Input = 46 MHz, -3 dBFS                                                                            | 69.8 |       | dBFS  |

|           | Input = 150 MHz, -3 dBFS                                                                           | 69.6 |       |       |

|           | Input = 231 MHz, -3 dBFS                                                                           | 69.4 |       |       |

|           | Input = 325 MHz, Ain = -3 dBFS                                                                     | 69.0 |       |       |

|           | Input = 325MHz, Ain = -40 dBFS                                                                     | 70.0 |       |       |

#### SNVS990A – DECEMBER 2013 – REVISED JANUARY 2014

### Converter Dynamic Performance Characteristics (Bit-Burst Mode) (continued)

Unless otherwise noted, these specifications apply for  $V_{A3,3} = 3.1 \text{ V}$ ;  $V_{A1,8} = 1.8 \text{ V}$ ;  $V_{A1,2} = V_{D1,2} = 1.2 \text{ V}$ ;  $F_{CLKIN} = F_S = 370 \text{ MSPS}$ ; device configured for Bit-Burst Mode, 14-bit High-Resolution; external differential resistive termination at ADC input is 66  $\Omega$ . Typical values are at  $T_A = +25^{\circ}$ C. **Boldface limits** apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ . All other limits apply at  $T_A = +25^{\circ}$ C, unless otherwise noted.

| PARAMETER | DESCRIPTION / CONDITIONS                                                                                         | TYP    | LIMIT | UNITS  |  |

|-----------|------------------------------------------------------------------------------------------------------------------|--------|-------|--------|--|

|           | Signal to Noise and Distortion Ratio, integrated across entire Nyquist bandwidth, Low Resolution Bit-Burst phase |        |       |        |  |

|           | Input = 325 MHz, Ain = -3 dBFS                                                                                   | 54.7   |       |        |  |

|           | Signal to Noise and Distortion Ratio, integrated across Nyquist bandwidth,<br>High Resolution Bit Burst phase    |        |       | -      |  |

| SINAD     | Input = 46 MHz, -3 dBFS                                                                                          | 69.5   |       | dBFS   |  |

|           | Input = 150 MHz, -3 dBFS                                                                                         | 69.4   |       |        |  |

|           | Input = 231 MHz, -3 dBFS                                                                                         | 69.1   |       |        |  |

|           | Input = 325 MHz, -3 dBFS                                                                                         | 68.8   |       | -      |  |

|           | Input = 325 MHz, -40 dBFS                                                                                        | 70.0   |       |        |  |

|           | Noise Spectral Density, average NSD across entire Nyquist bandwidth, Low Resolution Bit-Burst phase              |        |       |        |  |

|           | Input = 325 MHz, -3 dBFS                                                                                         | -141.1 |       |        |  |

|           | Noise Spectral Density, average NSD across Nyquist bandwidth, High Resolution Bit Burst phase                    |        |       | -      |  |

| NSD       | Input = 46 MHz, -3 dBFS                                                                                          | -152.5 |       | dBFS/H |  |

|           | Input = 150 MHz, -3 dBFS                                                                                         | -152.3 |       |        |  |

|           | Input = 231 MHz, -3 dBFS                                                                                         | -152.1 |       | _      |  |

|           | Input = 325 MHz, -3 dBFS                                                                                         | -151.7 |       |        |  |

|           | Input = 325 MHz, -40 dBFS                                                                                        | -152.7 |       |        |  |

|           | Spurious Free Dynamic Range, Single Tone, High Resolution Bit Burst phase                                        |        |       |        |  |

|           | Input = 46 MHz, -3 dBFS                                                                                          | 88     |       | dBFS   |  |

| SFDR      | Input = 150 MHz, -3 dBFS                                                                                         | 88     |       |        |  |

|           | Input = 231 MHz, -3 dBFS                                                                                         | 85     |       |        |  |

|           | Input = 325 MHz, -3 dBFS                                                                                         | 85     |       |        |  |

|           | 2 <sup>nd</sup> Order Harmonic Distortion                                                                        |        |       |        |  |

|           | Input = 46 MHz, -3 dBFS                                                                                          | -93    |       |        |  |

| HD2       | Input = 150 MHz, -3 dBFS                                                                                         | -89    |       | dBFS   |  |

|           | Input = 231 MHz, -3 dBFS                                                                                         | -90    |       |        |  |

|           | Input = 325MHz, -3 dBFS                                                                                          | -89    |       |        |  |

|           | 3 <sup>rd</sup> Order Harmonic Distortion                                                                        |        |       |        |  |

|           | Input = 46 MHz, -3 dBFS                                                                                          | -88    |       |        |  |

| HD3       | Input = 150 MHz, -3 dBFS                                                                                         | -88    |       | dBFS   |  |

|           | Input = 231 MHz, -3 dBFS                                                                                         | -85    |       |        |  |

|           | Input = 325MHz, -3 dBFS                                                                                          | -85    |       |        |  |

|           | Largest spurious tone, not including DC, HD2 or HD3                                                              |        |       |        |  |

|           | Input = 46 MHz, -3 dBFS                                                                                          | -90    |       |        |  |

| SPUR      | Input = 150 MHz, -3 dBFS                                                                                         | -90    |       | dBFS   |  |

|           | Input = 231 MHz, -3 dBFS                                                                                         | -90    |       |        |  |

|           | Input = 325MHz, -3 dBFS                                                                                          | -90    |       |        |  |

|           | Third-order Intermodulation, Dual Tone, High Resolution Bit Burst phase                                          |        |       |        |  |

| IMD3      | Tone 1 = 145 MHz, -10 dBFS<br>Tone 2 = 155 MHz, -10 dBFS                                                         | -102   |       | dBFS   |  |

SNVS990A - DECEMBER 2013 - REVISED JANUARY 2014

STRUMENTS www.ti.com

XAS

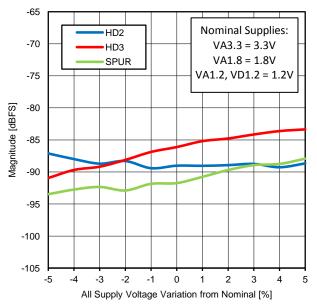

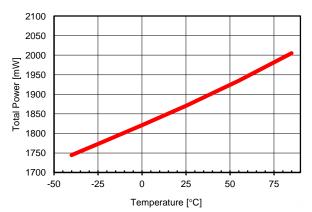

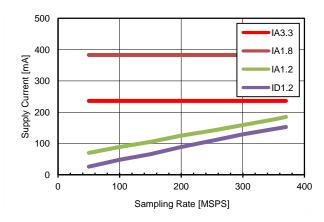

### POWER SUPPLY ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

Unless otherwise noted, these specifications apply for  $V_{A3.3} = 3.3 \text{ V}$ ;  $V_{A1.8} = 1.8 \text{ V}$ ;  $V_{A1.2} = V_{D1.2} = 1.2 \text{ V}$ ;  $F_{CLKIN} = F_S = 370 \text{ MSPS}$ . Typical values are at  $T_A =+25^{\circ}\text{C}$ . **Boldface limits** apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ . All other limits apply at  $T_A =+25^{\circ}\text{C}$ , unless otherwise noted.

| PARAMETER          |                                                                                         | DESCRIPTION / CONDITIONS                                                                                                                                                                                              | TYP   | LIMIT | UNIT |

|--------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|

|                    | V <sub>A3.3</sub> supply current                                                        | Normal operation, single data lane per channel                                                                                                                                                                        | 236   |       |      |

| I <sub>A3.3</sub>  | consumption                                                                             | Normal operation, dual data lane per channel                                                                                                                                                                          | 255   |       | mA   |

|                    |                                                                                         | Power down mode                                                                                                                                                                                                       | 8.7   |       |      |

|                    | VA1.8 supply current                                                                    | Normal operation                                                                                                                                                                                                      | 383   |       |      |

| I <sub>A1.8</sub>  | consumption                                                                             | Power down mode                                                                                                                                                                                                       | 3.6   |       | mA   |

| . V                | V <sub>A1.2</sub> supply current                                                        | Normal operation                                                                                                                                                                                                      | 176   |       |      |

| I <sub>A1.2</sub>  | I <sub>A1.2</sub> consumption                                                           | Power down mode                                                                                                                                                                                                       | 3.3   |       | mA   |

|                    | V <sub>D1.2</sub> supply current                                                        | SNRBoost Mode, F <sub>C</sub> =0.25*F <sub>S</sub>                                                                                                                                                                    | 141   |       |      |

| I <sub>D1.2</sub>  | consumption                                                                             | Bit-Burst Mode                                                                                                                                                                                                        | 46    |       | mA   |

|                    |                                                                                         | Power down mode                                                                                                                                                                                                       | 3.3   |       |      |

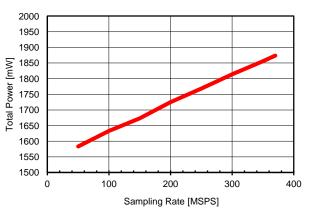

|                    | Total power consumption of the V_{A3.3} and V_{A1.8} and V_{A1.2} and V_{D1.2} supplies |                                                                                                                                                                                                                       |       |       |      |

| PT                 | SNRBoost Mode, $F_C=0.25^*F_S$ , Single Serial Lane per Channel                         |                                                                                                                                                                                                                       | 1,871 | 1978  | mW   |

|                    | Bit-Burst Mode, Single Serial Lane per Channel                                          |                                                                                                                                                                                                                       | 1,752 | 1854  |      |

| P <sub>PD</sub>    | Power Consumption d                                                                     | uring Power Down State, external clock active                                                                                                                                                                         | 30    |       | mW   |

| P <sub>SL</sub>    | Power Consumption d                                                                     | uring Sleep state, external clock active                                                                                                                                                                              | 30    |       | mW   |

| V <sub>BP2.5</sub> | Voltage at the BP2.5 p                                                                  | bin                                                                                                                                                                                                                   | 2.65  |       | V    |

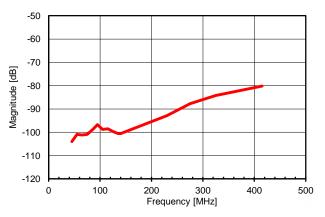

|                    | supply at 500kHz. Ana<br>the spur appears as p                                          | loise<br>r resulting from a 100mV sinusoidal signal modulating a<br>alog input is a -3 dBFS 150 MHz single tone. In all cases,<br>art of a pair symmetric about the fundamental that scales<br>fundamental amplitude. |       |       |      |

|                    | VA3.3                                                                                   |                                                                                                                                                                                                                       | -72.5 |       | dBFS |

|                    | VA1.8                                                                                   |                                                                                                                                                                                                                       | -58.0 |       |      |

|                    | VA1.2                                                                                   |                                                                                                                                                                                                                       | -37.7 |       |      |

|                    | VD1.2                                                                                   |                                                                                                                                                                                                                       | -78.0 |       |      |

(1) Power values indicate consumption during normal conversion assuming JESD204 link establishment and proper ADC calibration as described in ADC Core Calibration

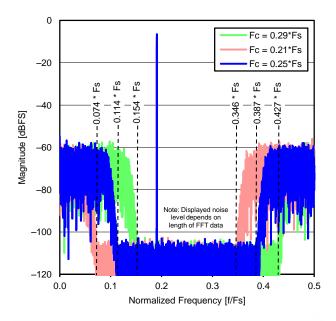

### **SNRBoost Mode Functional Characteristics**

Unless otherwise noted, these specifications apply for all supply and temperature conditions.

| PARAMETER         | DESCRIPTION / CONDITIONS                                                                                                                                                                                                                                       | VALUE                                                                   | UNIT  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------|

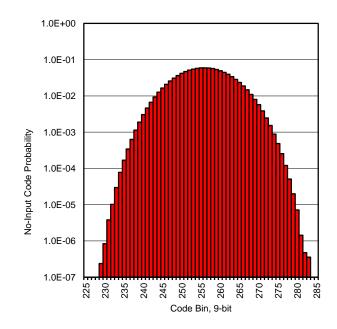

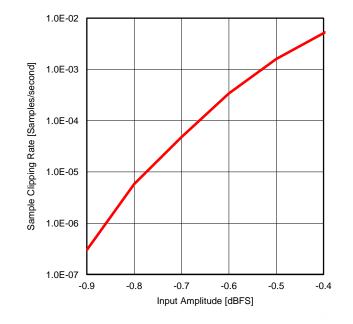

| FSR <sub>SB</sub> | SNRBoost Mode Digital Full Scale At Clipping<br>Maximum sinusoidal power before 9-bit clipping results in a sample clipping rate of 1e–5                                                                                                                       | -0.8                                                                    | dBFS  |

| BW <sub>SB</sub>  | Low-Noise Bandwidth<br>Dependent on sampling rate (F <sub>S</sub> )                                                                                                                                                                                            | 0.273 * F <sub>S</sub>                                                  | MHz   |

| FC <sub>SB</sub>  | Noise Shaping Center Frequencies<br>Configurable via SPI, dependent on sampling rate (F <sub>S</sub> ).                                                                                                                                                        | 0.21 * F <sub>S</sub><br>0.25 * F <sub>S</sub><br>0.29 * F <sub>S</sub> | MHz   |

| NQ <sub>SB</sub>  | Total Quantization Noise Power<br>Integrated noise across full Nyquist zone with no input signal.                                                                                                                                                              | -31.5                                                                   | dBFS  |

| OVRTH             | Over-range Detection Threshold<br>Configurable via SPI                                                                                                                                                                                                         | 0 (max)<br>–48.16 (min)                                                 | dBFS  |

| OVRTHS            | Over-range Detection Threshold Step<br>Expressed as the change in the total code range outside of which an over-range event<br>occurs. Half of the step value is changed at the upper boundary of the code range and half<br>is changed at the lower boundary. | 256                                                                     | Codes |

SNVS990A - DECEMBER 2013 - REVISED JANUARY 2014

#### www.ti.com

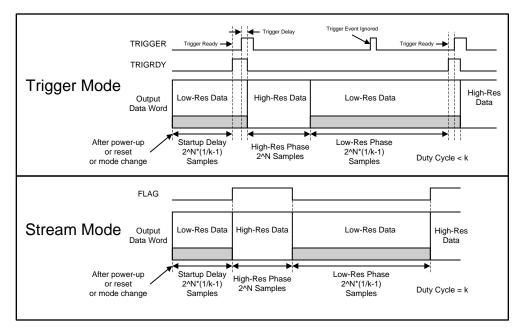

### **Bit-Burst Mode Functional Characteristics**

Unless otherwise noted, these specifications apply for all supply and temperature conditions.

| PARAMETER            | DESCRIPTION / CONDITIONS                                                                                                                                                                             | VALUE                         | UNIT    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------|

| R <sub>LOW-RES</sub> | Low-Res Phase Resolution<br>Bit resolution of the sampled data during the low-resolution phase of the Bit-Burst<br>cycle.                                                                            | 9                             | Bits    |

| R <sub>HI-RES</sub>  | High-Res Phase Resolution<br>Bit resolution of the sampled data during the high-resolution phase of the Bit-Burst<br>cycle; Configurable via SPI.                                                    | 12 or 14                      | Bits    |

| N <sub>HI-RES</sub>  | High-Res Phase Duration<br>Number of samples output during the High-Resolution phase of the Bit-Burst cycle;<br>Configurable via SPI.                                                                | 2^10 (min, def)<br>2^25 (max) | Samples |

| N <sub>LOW-RES</sub> | Low-Res Phase Duration Number of samples output during the Low-Resolution phase of the Bit-Burst cycle; Depends on $R_{HI-RES}$ and $N_{HI-RES}$ .                                                   |                               | Samples |

| LOW-RES              | R <sub>HI-RES</sub> = 14 bits                                                                                                                                                                        | 3 * N <sub>HI-RES</sub>       | Campico |

|                      | R <sub>HI-RES</sub> = 12 bits                                                                                                                                                                        | N <sub>HI-RES</sub>           |         |

| DC <sub>HI-RES</sub> | Bit-Burst Duty Cycle Ratio of $N_{HI-RES}$ to the total number of samples in a full Bit-Burst cycle; Depends on $R_{HI-RES}$ .                                                                       |                               |         |

| - OHI-RES            | R <sub>HI-RES</sub> = 14 bits                                                                                                                                                                        | 1 / 4                         |         |

|                      | R <sub>HI-RES</sub> = 12 bits                                                                                                                                                                        | 1 / 2                         |         |

| N <sub>D-BB</sub>    | Bit-Burst Mode Start-up Delay<br>Low-Resolution start-up time that must complete before High-Resolution bits appear<br>(Stream sub-mode) or High-Resolution bits may be triggered (Trigger sub-mode) |                               |         |

|                      | After supply power-up                                                                                                                                                                                | 3 * 2^10                      | Samples |

| D-DD                 | After soft power-up via SPI                                                                                                                                                                          | N <sub>LOW-RES</sub>          | 0       |

|                      | After changing R <sub>HI-RES</sub>                                                                                                                                                                   | N <sub>LOW-RES</sub>          |         |

|                      | After entering Bit-Burst Mode or switching between Trigger and Stream configurations                                                                                                                 | N <sub>LOW-RES</sub>          |         |

#### Input Clock Divider and Clock Phase Adjustment Functional Characteristics

Unless otherwise noted, these specifications apply for  $V_{A3,3} = 3.3 \text{ V}$ ;  $V_{A1,8} = 1.8 \text{ V}$ ;  $V_{A1,2} = V_{D1,2} = 1.2 \text{ V}$ ;  $F_{CLKIN} = F_S = 370 \text{ MSPS}$ . Typical values are at  $T_A = +25^{\circ}\text{C}$ . **Boldface limits** apply for  $T_A = T_{MIN}$  to  $T_{MAX}$ . All other limits apply at  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.

| PARAMETER       | DESCRIPTION / CONDITIONS                                                                                                                                                                                | TYP                            | LIMIT | UNIT |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|-------|------|

| CLKDIV          | Input CLKIN Divider Factor<br>Configurable via SPI                                                                                                                                                      | 1 (default), 2, 4, or 8        |       |      |

| ΝΦ <sub>C</sub> | Number of Available Coarse Phase Adjustment Steps                                                                                                                                                       |                                |       |      |

| Φ <sub>C</sub>  | Nominal CLKIN Coarse Phase Adjustment Step<br>Coarse step of CLKIN divider phase adjustment range; Common to both<br>channels; Depends on clock divider factor (CLKDIV) and sampling rate<br>( $F_S$ ). | 1 / (2*CLKDIV*F <sub>S</sub> ) |       | S    |

| ΔΦ <sub>C</sub> | Typical Coarse Phase Adjustment Step $Error^{(1)}$ Percent variation of actual phase adjustment step relative to the nominal step ( $\Phi_C$ ). Assumes ideal 50% CLKIN duty cycle                      |                                |       |      |

| <u>⊿</u> ⊕C     | CLKDIV = 8, F <sub>S</sub> = 250MSPS                                                                                                                                                                    | +/- 6                          |       | 0/   |

|                 | CLKDIV = 4, F <sub>S</sub> = 370MSPS                                                                                                                                                                    | +/- 4                          |       | %    |

(1) CLKIN duty cycles that are not 50/50% increase the coarse delay step error

SNVS990A - DECEMBER 2013-REVISED JANUARY 2014

www.ti.com

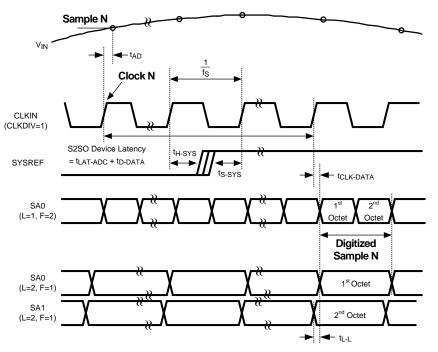

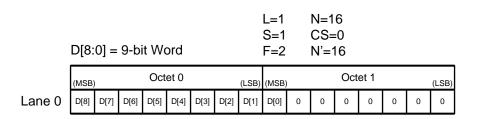

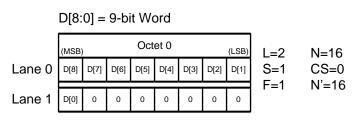

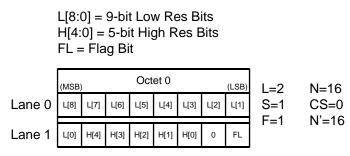

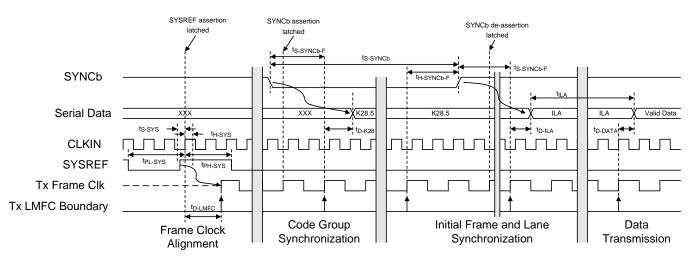

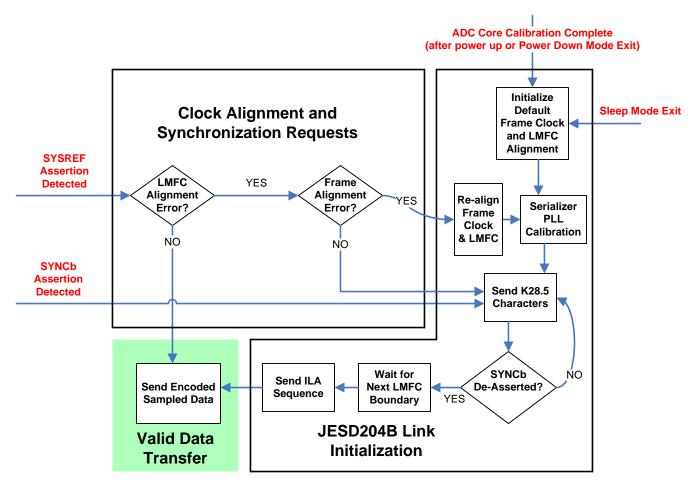

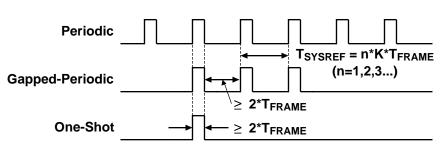

### **JESD204B Interface Functional Characteristics**

Unless otherwise noted, these specifications apply for all supply and temperature conditions.

| PARAMETER | DESCRIPTION / CONDITIONS                                                                                   | VALUE                                |

|-----------|------------------------------------------------------------------------------------------------------------|--------------------------------------|

| LSF       | Supported Configurations<br>L = Number of lanes/converter<br>S = Samples per frame<br>F = Octets per frame | L=1, S=1, F=2<br>or<br>L=2, S=1, F=1 |

| к         | Number of Frames per Multi-Frame<br>Configurable via SPI.                                                  |                                      |

|           | L=1, S=1, F=2                                                                                              | 9 (min)<br>32 (max, default)         |

|           | L=2, S=1, F=1                                                                                              | 17 (min)<br>32 (max, default)        |

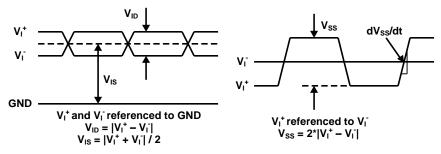

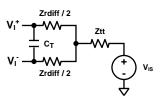

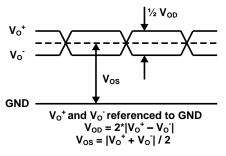

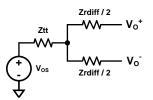

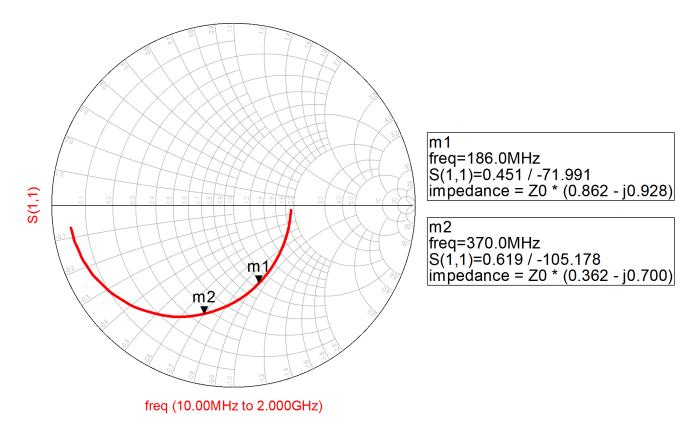

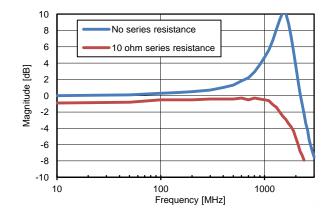

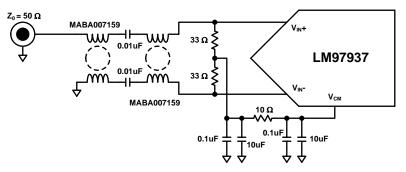

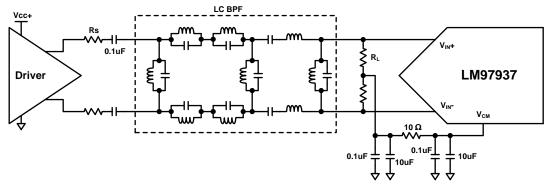

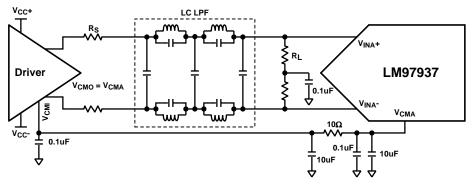

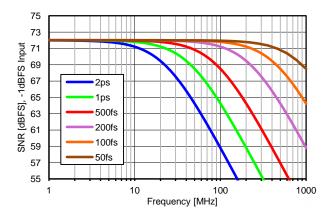

### **Analog Interface Electrical Characteristics**