Stereo Audio Codec, 8- to 96-kHz, With Integrated Headphone Amplifier

# **Data Manual**

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

> Literature Number: SGLS240C March 2004–Revised June 2012

## Stereo Audio Codec, 8- to 96-kHz, With Integrated Headphone Amplifier

Check for Samples: TLV320AIC23B-Q1

## 1 1 Introduction

- 1.1 Features

- Qualified for Automotive Applications

- High-Performance Stereo Codec

- 90-dB SNR Multibit Sigma-Delta ADC (Aweighted at 48 kHz)

- 100-dB SNR Multibit Sigma-Delta DAC (Aweighted at 48 kHz)

- 1.42 V 3.6 V Core Digital Supply: Compatible With TI C54x DSP Core Voltages

- 2.7 V 3.6 V Buffer and Analog Supply: Compatible Both TI C54x DSP Buffer Voltages

- 8-kHz 96-kHz Sampling-Frequency Support

- Software Control Via TI McBSP-Compatible Multiprotocol Serial Port

- 2-wire-Compatible and SPI-Compatible Serial-Port Protocols

- Glueless Interface to TI McBSPs

- Audio-Data Input/Output Via TI McBSP-Compatible Programmable Audio Interface

- I<sup>2</sup>S-Compatible Interface Requiring Only One McBSP for both ADC and DAC

- Standard I<sup>2</sup>S, MSB, or LSB Justified-Data Transfers

- 16/20/24/32-Bit Word Lengths

- Audio Master/Slave Timing Capability Optimized for TI DSPs (250/272 f<sub>s</sub>), USB mode

- Industry-Standard Master/Slave Support Provided Also (256/384 f<sub>s</sub>), Normal mode

- Glueless Interface to TI McBSPs

## 1.2 Description

- Integrated Total Electret-Microphone Biasing and Buffering Solution

- Low-Noise MICBIAS pin at 3/4 AVDD for Biasing of Electret Capsules

- Integrated Buffer Amplifier With Tunable Fixed Gain of 1 to 5

- Additional Control-Register Selectable Buffer Gain of 0 dB or 20 dB

- Stereo-Line Inputs

- Integrated Programmable Gain Amplifier

- Analog Bypass Path of Codec

- ADC Multiplexed Input for Stereo-Line Inputs and Microphone

- Stereo-Line Outputs

- Analog Stereo Mixer for DAC and Analog Bypass Path

- Volume Control With Mute on Input and Output

- Highly Efficient Linear Headphone Amplifier

- 30 mW into 32  $\Omega$  From a 3.3-V Analog Supply Voltage

- Flexible Power Management Under Total Software Control

- 23-mW Power Consumption During Playback Mode

- Standby Power Consumption < 150 μW</li>

- Power-Down Power Consumption < 15 μW</li>

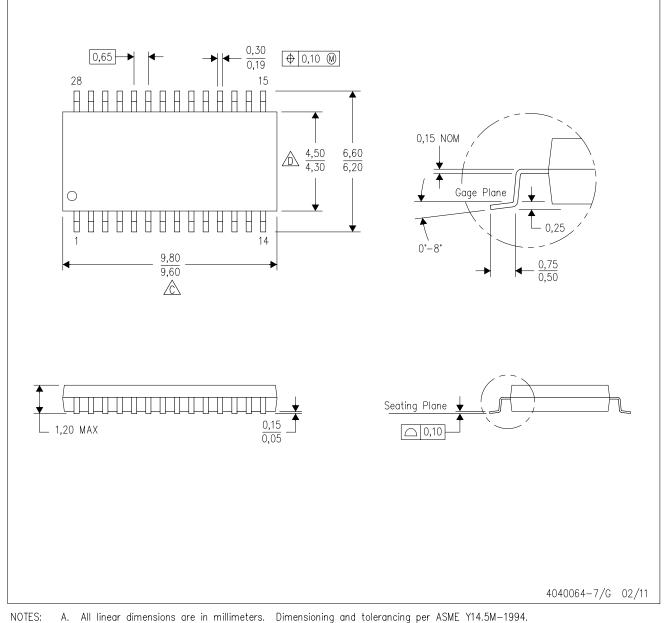

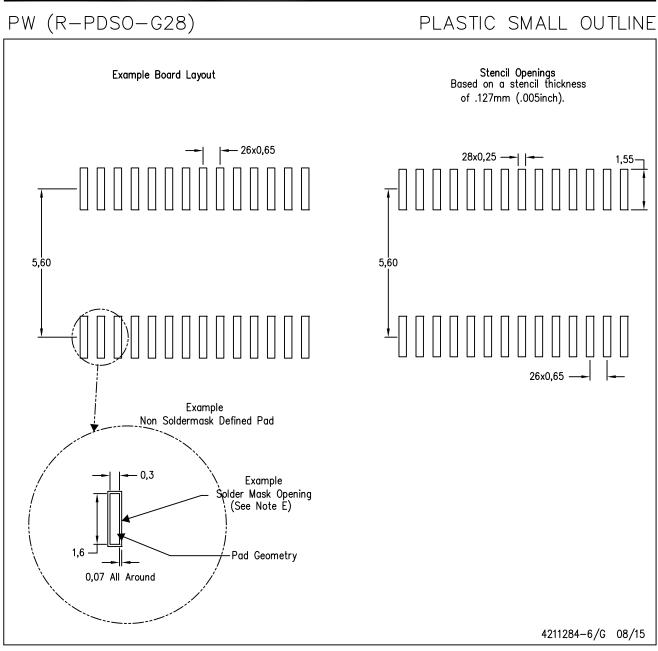

- 28-Pin TSSOP (62 mm<sup>2</sup> Total Board Area)

- Ideally Suitable for Portable Solid-State Audio Players and Recorders

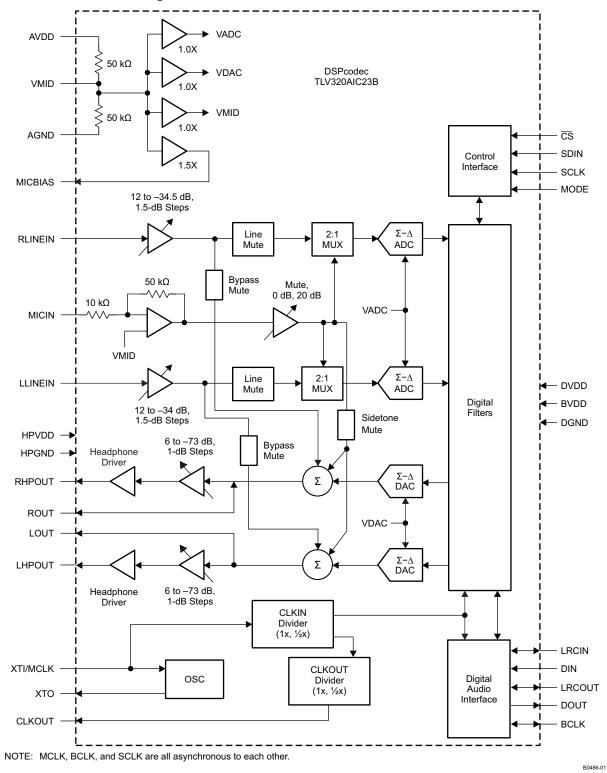

The TLV320AIC23B-Q1 is a high-performance stereo audio codec with highly integrated analog functionality. The analog-to-digital converters (ADCs) and digital-to-analog converters (DACs) within the TLV320AIC23B-Q1 use multibit sigma-delta technology with integrated oversampling digital interpolation filters. Data-transfer word lengths of 16, 20, 24, and 32 bits, with sample rates from 8 kHz to 96 kHz, are supported. The ADC sigma-delta modulator features third-order multibit architecture with up to 90-dBA signal-to-noise ratio (SNR) at audio sampling rates up to 96 kHz, enabling high-fidelity audio recording in a compact, power-saving design. The DAC sigma-delta modulator features a second-order multibit architecture with up to 100-dBA SNR at audio sampling rates up to 96 kHz, enabling high-quality digital audio-playback capability, while consuming less than 23 mW during playback only. The TLV320AIC23B-Q1 is the ideal analog input/output (I/O) choice for portable digital audio-player and recorder applications, such as MP3 digital audio players.

SGLS240C - MARCH 2004 - REVISED JUNE 2012

Integrated analog features consist of stereo-line inputs with an analog bypass path, a stereo headphone amplifier, with analog volume control and mute, and a complete electret-microphone-capsule biasing and buffering solution. The headphone amplifier is capable of delivering 30 mW per channel into 32  $\Omega$ . The analog bypass path allows use of the stereo-line inputs and the headphone amplifier with analog volume control, while completely bypassing the codec, thus enabling further design flexibility, such as integrated FM tuners. A microphone bias-voltage output provides a low-noise current source for electret-capsule biasing. The AIC23B has an integrated adjustable microphone amplifier (gain adjustable from 1 to 5) and a programmable gain microphone amplifier (0 dB or 20 dB). The microphone signal can be mixed with the output signals if a sidetone is required.

While the TLV320AIC23B-Q1 supports the industry-standard oversampling rates of 256  $f_s$  and 384  $f_s$ , unique oversampling rates of 250  $f_s$  and 272  $f_s$  are provided, which optimize interface considerations in designs using TI C54x digital signal processors (DSPs) and universal serial bus (USB) data interfaces. A single 12-MHz crystal can supply clocking to the DSP, USB, and codec. The TLV320AIC23B-Q1 features an internal oscillator that, when connected to a 12-MHz external crystal, provides a system clock to the DSP and other peripherals at either 12 MHz or 6 MHz, using an internal clock buffer and selectable divider. Audio sample rates of 48 kHz and compact-disc (CD) standard 44.1 kHz are supported directly from a 12-MHz master clock with 250  $f_s$  and 272  $f_s$  oversampling rates.

Low power consumption and flexible power management allow selective shutdown of codec functions, thus extending battery life in portable applications. This design solution makes powerful portable stereo audio designs easily realizable in a cost-effective, space-saving total analog I/O solution: the TLV320AIC23B-Q1.

## **1.3 Functional Block Diagram**

SGLS240C - MARCH 2004 - REVISED JUNE 2012

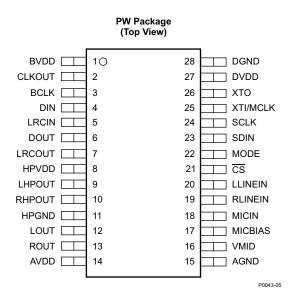

## 1.4 Pin Assignments

## 1.5 Ordering Information

| T <sub>A</sub> | PACKAGE | REEL | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|---------|------|-----------------------|------------------|

| -40°C to 85°C  | TSSOP   | 2000 | TLV320AIC23BIPWRQ1    | AIC23BIQ1        |

www.ti.com

## 1.6 Pin Functions

## Table 1-1. Pin Functions

| PI            | N   | 1/0 | DECODIDION                                                                                                                                                                                                                    |

|---------------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME          | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                   |

| AGND          | 15  |     | Analog supply return                                                                                                                                                                                                          |

| AVDD          | 14  |     | Analog supply input. Voltage level is 3.3 V nominal.                                                                                                                                                                          |

| BCLK          | 3   | I/O | I <sup>2</sup> S serial-bit clock. In audio master mode, the AIC23B generates this signal and sends it to the DSP. In audio slave mode, the signal is generated by the DSP.                                                   |

| BVDD          | 1   |     | Buffer supply input. Voltage range is from 2.7 V to 3.6 V.                                                                                                                                                                    |

| CLKOUT        | 2   | 0   | Clock output. This is a buffered version of the XTI input and is available in 1X or 1/2X frequencies of XTI. Bit 07 in the sample rate control register controls frequency selection.                                         |

| <del>CS</del> | 21  | I   | Control port input latch/address select. For SPI control mode this input acts as the data latch control. For 2-wire control mode this input defines the seventh bit in the device address field. See Section 3.1 for details. |

| DIN           | 4   | I   | I <sup>2</sup> S format serial data input to the sigma-delta stereo DAC                                                                                                                                                       |

| DGND          | 28  |     | Digital supply return                                                                                                                                                                                                         |

| DOUT          | 6   | 0   | I <sup>2</sup> S format serial data output from the sigma-delta stereo ADC                                                                                                                                                    |

| DVDD          | 27  |     | Digital supply input. Voltage range is 1.4 V to 3.6 V.                                                                                                                                                                        |

| HPGND         | 11  |     | Analog headphone amplifier supply return                                                                                                                                                                                      |

| HPVDD         | 8   |     | Analog headphone amplifier supply input. Voltage level is 3.3 V nominal.                                                                                                                                                      |

| LHPOUT        | 9   | 0   | Left stereo mixer-channel amplified headphone output. Nominal 0-dB output level is 1 VRMS. Gain of<br>-73 dB to 6 dB is provided in 1-dB steps.                                                                               |

| LLINEIN       | 20  | I   | Left stereo-line input channel. Nominal 0-dB input level is 1 VRMS. Gain of –34.5 dB to 12 dB is provided in 1.5-dB steps.                                                                                                    |

| LOUT          | 12  | 0   | Left stereo mixer-channel line output. Nominal output level is 1.0 VRMS.                                                                                                                                                      |

| LRCIN         | 5   | I/O | I <sup>2</sup> S DAC-word clock signal. In audio master mode, the AIC23B generates this framing signal and sends it to the DSP. In audio slave mode, the signal is generated by the DSP.                                      |

| LRCOUT        | 7   | I/O | I <sup>2</sup> S ADC-word clock signal. In audio master mode, the AIC23B generates this framing signal and sends it to the DSP. In audio slave mode, the signal is generated by the DSP.                                      |

| MICBIAS       | 17  | 0   | Buffered low-noise-voltage output suitable for electret-microphone-capsule biasing. Voltage level is 3/4 AVDD nominal.                                                                                                        |

| MICIN         | 18  | I   | Buffered amplifier input suitable for use with electret-microphone capsules. Without external resistors a default gain of 5 is provided. See Section 2.3.1.2 for details.                                                     |

| MODE          | 22  | I   | Serial-interface-mode input. See Section 3.1 for details.                                                                                                                                                                     |

| NC            |     |     | Not Used—No internal connection                                                                                                                                                                                               |

| RHPOUT        | 10  | 0   | Right stereo mixer-channel amplified headphone output. Nominal 0-dB output level is 1 VRMS. Gain of<br>-73 dB to 6 dB is provided in 1-dB steps.                                                                              |

| RLINEIN       | 19  | I   | Right stereo-line input channel. Nominal 0-dB input level is 1 VRMS. Gain of –34.5 dB to 12 dB is provided in 1.5-dB steps.                                                                                                   |

| ROUT          | 13  | 0   | Right stereo mixer-channel line output. Nominal output level is 1.0 VRMS.                                                                                                                                                     |

| SCLK          | 24  | I   | Control-port serial-data clock. For SPI and 2-wire control modes this is the serial-clock input. See Section 3.1 for details.                                                                                                 |

| SDIN          | 23  | I   | Control-port serial-data input. For SPI and 2-wire control modes this is the serial-data input and also is used to select the control protocol after reset. See Section 3.1 for details.                                      |

| VMID          | 16  | I   | Midrail voltage decoupling input. 10- $\mu$ F and 0.1- $\mu$ F capacitors should be connected in parallel to this terminal for noise filtering. Voltage level is 1/2 AVDD nominal.                                            |

| XTI/MCLK      | 25  | I   | Crystal or external-clock input. Used for derivation of all internal clocks on the AIC23B.                                                                                                                                    |

| хто           | 26  | 0   | Crystal output. Connect to external crystal for applications where the AIC23B is the audio timing master. Not used in applications where external clock source is used.                                                       |

www.ti.com

## 2 Electrical Specifications

## 2.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                                  |                                                                              | VALUE                    | UNIT |

|------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------|------|

| Supply voltage range <sup>(2)</sup>                              | $AV_{DD}$ to AGND, $DV_{DD}$ to DGND, $BV_{DD}$ to DGND, $HPV_{DD}$ to HPGND | -0.3 to 3.63             | V    |

| Analog supply return to digital supply return                    | AGND to DGND                                                                 | -0.3 to 3 .63            | V    |

|                                                                  | Digital                                                                      | –0.3 to DV <sub>DD</sub> | V    |

| Input voltage range, all input signals                           | Analog                                                                       | –0.3 to AV <sub>DD</sub> | V    |

| Case temperature for 10 seconds                                  |                                                                              | 240                      | °C   |

| Operating free-air temperature range: Industrial, T <sub>A</sub> |                                                                              | -40 to 85                | °C   |

| Storage temperature range, T <sub>stg</sub>                      |                                                                              | -65 to 150               | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) DV<sub>DD</sub> may not exceed BV<sub>DD</sub> 0.3 V; BV<sub>DD</sub> may not exceed AV<sub>DD</sub> 0.3 V or HPV<sub>DD</sub> 0.3.

## 2.2 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                                                            | MIN  | NOM | MAX   | UNIT             |

|----------------------------------------------------------------------------|------|-----|-------|------------------|

| Analog supply voltage, AV <sub>DD</sub> , HPV <sub>DD</sub> <sup>(1)</sup> | 2.7  | 3.3 | 3.6   | V                |

| Digital buffer supply voltage, BV <sub>DD</sub> <sup>(1)</sup>             | 2.7  | 3.3 | 3.6   | V                |

| Digital core supply voltage, DV <sub>DD</sub> <sup>(1)</sup>               | 1.42 | 1.5 | 3.6   | V                |

| Analog input voltage, full scale - 0 dB (AV <sub>DD</sub> = 3.3 V)         |      | 1   |       | V <sub>RMS</sub> |

| Stereo-line output load resistance                                         | 10   |     |       | kΩ               |

| Headphone-amplifier output load resistance                                 | 0    |     |       | Ω                |

| CLKOUT digital output load capacitance                                     |      | 20  |       | pF               |

| All other digital output load capacitance                                  |      | 10  |       | pF               |

| Stereo-line output load capacitance                                        |      | 50  |       | pF               |

| XTI master clock Input                                                     |      |     | 18.43 | MHz              |

| ADC or DAC conversion rate                                                 |      |     | 96    | kHz              |

| Operating free-air temperature, T <sub>A</sub> Industrial                  |      | -40 | 85    | °C               |

(1) Digital voltage values are with respect to DGND; analog voltage values are with respect to AGND.

## 2.3 Electrical Characteristics

over recommended operating conditions,  $AV_{DD}$ ,  $HPV_{DD}$ ,  $BV_{DD} = 3.3$  V,  $DV_{DD} = 1.5$  V, slave mode, XTI/MCLK = 256 f<sub>s</sub>, f<sub>s</sub> = 48 kHz (unless otherwise stated)

## 2.3.1 ADC

### 2.3.1.1 Line Input to ADC

| PARAMETER                                                         | TEST CONDITIONS                            | MIN   | TYP | MAX | UNIT             |

|-------------------------------------------------------------------|--------------------------------------------|-------|-----|-----|------------------|

| Input signal level (0 dB)                                         |                                            |       | 1   |     | V <sub>RMS</sub> |

| Signal to point ratio A weighted 0 dD gain $(1)(2)$               | f <sub>s</sub> = 48 kHz (3.3 V)            | 85    | 90  |     | dB               |

| Signal-to-noise ratio, A-weighted, 0-dB gain $^{(1)(2)}$          | f <sub>s</sub> = 48 kHz (2.7 V)            |       | 90  |     | uБ               |

| Dynamia range Augishtad $CO dD full each input (2)$               | AV <sub>DD</sub> = 3.3 V                   | 85    | 90  |     | dB               |

| Dynamic range, A-weighted, -60-dB full-scale input <sup>(2)</sup> | AV <sub>DD</sub> = 2.7 V                   |       | 90  |     | uБ               |

| Total harmonic distortion 1 dB input 0 dB agin                    | AV <sub>DD</sub> = 3.3 V                   |       | -80 |     | dB               |

| Total harmonic distortion, -1-dB input, 0-dB gain                 | AV <sub>DD</sub> = 2.7 V                   |       | 80  |     | uБ               |

| Power supply rejection ratio                                      | 1 kHz, 100 mV <sub>pp</sub>                |       | 50  |     | dB               |

| ADC channel separation                                            | 1 kHz input tone                           |       | 90  |     | dB               |

| Programmable gain                                                 | 1 kHz input tone, $R_{SOURCE} < 50 \Omega$ | -34.5 |     | 12  | dB               |

| Programmable gain step size                                       | Monotonic                                  |       | 1.5 |     | dB               |

| Mute attenuation                                                  | 0 dB, 1 kHz input tone                     |       | 80  |     | dB               |

|                                                                   | 12 dB input gain                           | 10    |     | 20  | 1.0              |

| Input resistance                                                  | 0 dB input gain                            | 28    | 35  |     | kΩ               |

| Input capacitance                                                 |                                            |       | 10  |     | pF               |

(1) Ratio of output level with 1-kHz full-scale input, to the output level with the input short circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

(2) All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

## 2.3.1.2 Microphone Input to ADC

0-dB Gain,  $f_s = 8 \text{ kHz}$  (40-K $\Omega$  source impedance, see Section 1.3)

| PARAMETER                                                         | TEST CONDITIONS                              | MIN | TYP | MAX | UNIT             |

|-------------------------------------------------------------------|----------------------------------------------|-----|-----|-----|------------------|

| Input signal level (0 dB)                                         |                                              |     | 1   |     | V <sub>RMS</sub> |

| Signal-to-noise ratio, A-weighted, 0-dB gain <sup>(1)(2)</sup>    | AV <sub>DD</sub> = 3.3 V                     | 77  | 85  |     | dB               |

| Signal-to-hoise ratio, A-weighted, 0-dB gainted                   | $AV_{DD} = 2.7 V$                            |     | 84  |     | uБ               |

| Durantia range A unighted 20 dB full acale input <sup>(2)</sup>   | AV <sub>DD</sub> = 3.3 V                     | 77  | 85  |     |                  |

| Dynamic range, A-weighted, -60-dB full-scale input <sup>(2)</sup> | AV <sub>DD</sub> = 2.7 V                     |     | 84  |     | dB               |

| Total harmonic distortion 1 dD input 0 dD acin                    | AV <sub>DD</sub> = 3.3 V                     |     | -60 |     | ٩D               |

| Total harmonic distortion, -1-dB input, 0-dB gain                 | $AV_{DD} = 2.7 V$                            |     | -60 |     | dB               |

| Power supply rejection ratio                                      | 1 kHz, 100 mV <sub>pp</sub>                  |     | 50  |     | dB               |

| Programmable gain boost                                           | 1 kHz input tone, $R_{SOURCE}$ < 50 $\Omega$ |     | 20  |     | dB               |

| Microphone-path gain                                              | MICBOOST = 0, $R_{SOURCE} < 50 \Omega$       |     | 14  |     | dB               |

| Mute attenuation                                                  | 0 dB, 1 kHz input tone                       | 60  | 80  |     | dB               |

| Input resistance                                                  |                                              | 8   | 14  |     | kΩ               |

| Input capacitance                                                 |                                              |     | 10  |     | pF               |

(1) Ratio of output level with 1-kHz full-scale input, to the output level with the input short circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

(2) All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

#### 2.3.1.3 Microphone Bias

| PARAMETER            | TEST CONDITIONS | MIN                          | ТҮР                  | MAX                          | UNIT   |

|----------------------|-----------------|------------------------------|----------------------|------------------------------|--------|

| Bias voltage         |                 | 3/4 AV <sub>DD</sub> - 100 m | 3/4 AV <sub>DD</sub> | 3/4 AV <sub>DD</sub> + 100 m | V      |

| Bias-current source  |                 |                              |                      | 3                            | mA     |

| Output noise voltage | 1 kHz to 20 kHz |                              | 25                   |                              | nV/√Hz |

## 2.3.2 DAC

Line output, load =  $10 \text{ k}\Omega$ , 50 pF

| PARAMETER                                                         | TES                         | TEST CONDITIONS          |    | TYP | MAX | UNIT             |

|-------------------------------------------------------------------|-----------------------------|--------------------------|----|-----|-----|------------------|

| 0-dB full-scale output voltage (FFFFF)                            |                             |                          |    | 1   |     | V <sub>RMS</sub> |

| Signal-to-noise ratio, A-weighted, 0-dB gain <sup>(1)(2)(3)</sup> | $AV_{DD} = 3.3 V$           | $f_s = 48 kHz$           | 90 | 100 |     | dB               |

|                                                                   | $AV_{DD} = 2.7 V$           | $f_s = 48 \text{ kHz}$   |    | 100 |     | uБ               |

| Dynamic range, A-weighted <sup>(2)</sup>                          | $AV_{DD} = 3.3 V$           | AV <sub>DD</sub> = 3.3 V |    | 90  |     | dB               |

| bynamic range, A-weighted                                         | $AV_{DD} = 2.7 V$           |                          |    | TBD |     | uБ               |

|                                                                   |                             | 1 kHz, 0 dB              |    | -88 | -80 | ٩D               |

| Total harmonic distortion                                         | $AV_{DD} = 3.3 V$           | 1 kHz, –3 dB             |    | -92 | -86 | dB               |

|                                                                   |                             | 1 kHz, 0 dB              |    | -85 |     | dB               |

|                                                                   | $AV_{DD} = 2.7 V$           | 1 kHz, –3 dB             |    | -88 |     | uБ               |

| Power supply rejection ratio                                      | 1 kHz, 100 mV <sub>pp</sub> | ·                        |    | 50  |     | dB               |

| DAC channel separation                                            |                             |                          |    | 100 |     | dB               |

(1) Ratio of output level with 1-kHz full-scale input, to the output level with the input short circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer

(2) All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

(3) Ratio of output level with 1-kHz full-scale input, to the output level with all zeros into the digital input, measured A-weighted over a 20-Hz to 20-kHz bandwidth.

## 2.3.3 Analog Line Input to Line Output (Bypass)

| PARAMETER                                                      | TEST CONDITIONS             |                          | MIN | TYP | MAX | UNIT             |

|----------------------------------------------------------------|-----------------------------|--------------------------|-----|-----|-----|------------------|

| 0-dB full-scale output voltage                                 |                             |                          |     | 1   |     | V <sub>RMS</sub> |

| Circulto noise ratio A weighted 0 dD $acin^{(1)}(2)$           | $AV_{DD} = 3.3 V$           |                          | 90  | 95  |     | dB               |

| Signal-to-noise ratio, A-weighted, 0-dB gain <sup>(1)(2)</sup> | $AV_{DD} = 2.7 V$           | AV <sub>DD</sub> = 2.7 V |     | 95  |     | uБ               |

|                                                                | AV <sub>DD</sub> = 3.3 V    | 1 kHz, 0 dB              |     | -86 | -80 | - dB             |

| Total bernania distantian                                      |                             | 1 kHz, –3 dB             |     | -92 | -86 |                  |

| Total harmonic distortion                                      | AV( 0.7.)(                  | 1 kHz, 0 dB              |     | -86 |     |                  |

|                                                                | $AV_{DD} = 2.7 V$           | 1 kHz, –3 dB             |     | -92 |     | dB               |

| Power supply rejection ratio                                   | 1 kHz, 100 mV <sub>pp</sub> |                          |     | 50  |     | dB               |

| DAC channel separation (left to right)                         | 1 kHz, 0 dB                 |                          |     | 80  |     | dB               |

(1) Ratio of output level with 1-kHz full-scale input, to the output level with the input short circuited, measured A-weighted over a 20-Hz to 20-kHz bandwidth using an audio analyzer.

(2) All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

Texas Instruments

www.ti.com

## 2.3.4 Stereo Headphone Output

| PARAMETER                             | TES                                       | T CONDITIONS | MIN | TYP | MAX | UNIT |

|---------------------------------------|-------------------------------------------|--------------|-----|-----|-----|------|

| 0-dB full-scale output voltage        |                                           |              |     | 1   |     | VRMS |

| Maximum dan tanan D                   | RL = 32 Ω                                 |              |     | 30  |     |      |

| Maximum output power, P <sub>O</sub>  | RL = 16 Ω                                 | RL = 16 Ω    |     |     |     | mW   |

| Signal-to-noise ratio, A-weighted (1) | AV <sub>DD</sub> = 3.3 V                  |              | 88  | 97  |     | dB   |

|                                       | AV <sub>DD</sub> = 3.3 V,<br>1 kHz output | PO = 10 mW   |     |     | 0.1 |      |

| Total harmonic distortion             |                                           | PO = 20 mW   |     |     | 1   | %    |

| Power supply rejection ratio          | 1 kHz, 100 mV <sub>pp</sub>               |              |     | 50  |     | dB   |

| Programmable gain                     | 1 kHz output                              |              | -73 |     | 6   | dB   |

| Programmable-gain step size           |                                           |              |     | 1   |     | dB   |

| Mute attenuation                      | 1 kHz output                              |              |     | 80  |     | dB   |

(1) All performance measurements done with 20-kHz low-pass filter and, where noted, A-weighted filter. Failure to use such a filter results in higher THD + N and lower SNR and dynamic range readings than shown in the Electrical Characteristics. The low-pass filter removes out-of-band noise, which, although not audible, may affect dynamic specification values.

### 2.3.5 Analog Reference Levels

| PARAMETER          | MIN                         | TYP | MAX                         | UNIT |

|--------------------|-----------------------------|-----|-----------------------------|------|

| Reference voltage  | AV <sub>DD</sub> /2 – 50 mV |     | $AV_{DD}/2 + 50 \text{ mV}$ | V    |

| Divider resistance | 40                          | 50  | 60                          | kΩ   |

## 2.3.6 Digital I/O

|                 | PARAMETER         | MIN                  | TYP | MAX                  | UNIT |

|-----------------|-------------------|----------------------|-----|----------------------|------|

| VIL             | Input low level   |                      |     | $0.3 \times BV_{DD}$ | V    |

| VIH             | Input high level  | $0.7 \times BV_{DD}$ |     |                      | V    |

| V <sub>OL</sub> | Output low level  |                      |     | $0.1 \times BV_{DD}$ | V    |

| V <sub>OH</sub> | Output high level | $0.9 \times BV_{DD}$ |     |                      | V    |

## 2.3.7 Supply Current

| PARAMETER                        | TEST (                                                      | MIN                 | TYP | MAX  | UNIT |    |

|----------------------------------|-------------------------------------------------------------|---------------------|-----|------|------|----|

|                                  | Record and playback (all active)                            |                     | 20  | 24   | 26   |    |

|                                  | Record and playback (osc, clk, and MIC output powered down) |                     | 16  | 18   | 20   |    |

|                                  | Line playback only                                          |                     | 6   | 7.5  | 9    |    |

| Total supply current,            | Record only                                                 |                     | 11  | 13.5 | 15   | mA |

| No input signal I <sub>TOT</sub> | Analog bypass (line in to line o                            | ut)                 | 4   | 4.5  | 6    |    |

|                                  | Power down, $DV_{DD} = 1.5 V$ ,                             | Oscillator enabled  | 0.8 | 1.5  | 3    |    |

|                                  | $AV_{DD}$<br>= $BV_{DD}$ = $HPV_{DD}$ = 3.3 V               | Oscillator disabled |     | 0.01 |      |    |

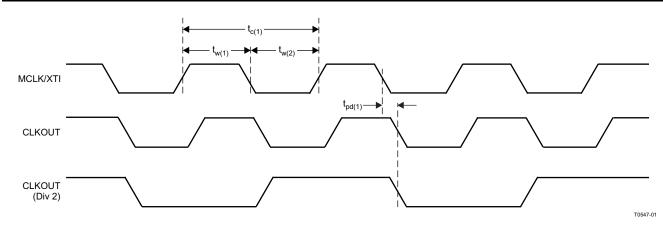

### 2.4 Digital-Interface Timing

|        | PARAMETER                                                 |      |       | TYP MAX | UNIT |

|--------|-----------------------------------------------------------|------|-------|---------|------|

| tw(1)  | System clock pulse duration MCLK/VTL                      | High | 18    |         | ns   |

| tw(2)  | <ul> <li>System-clock pulse duration, MCLK/XTI</li> </ul> | Low  | 18    |         |      |

| tc(1)  | 1) System-clock period, MCLK/XTI                          |      | 54    |         | ns   |

|        | Duty cycle, MCLK/XTI                                      |      | 40/60 | 60/40   | %    |

| tpd(1) | tpd(1) Propagation delay, CLKOUT                          |      | 0     | 10      | ns   |

## TLV320AIC23B-Q1

SGLS240C - MARCH 2004 - REVISED JUNE 2012

Figure 2-1. System-Clock Timing Requirements

|                               |                    | T   |         |      |

|-------------------------------|--------------------|-----|---------|------|

|                               | PARAMETER          | MIN | TYP MAX | UNIT |

| tpd(2) Propagation delay, LRC | N/LRCOUT           | 0   | 10      | ns   |

| tpd(3) Propagation delay, DOL | Т                  | 0   | 10      | ns   |

| tsu(1) Setup time, DIN        |                    | 10  |         | ns   |

| th(1) Hold time, DIN          |                    | 10  |         | ns   |

| BCLK                          |                    |     | /       |      |

|                               |                    |     |         |      |

|                               | X                  |     |         |      |

|                               | t <sub>pd(3)</sub> |     |         |      |

|                               | t <sub>su(1)</sub> | X   | X       |      |

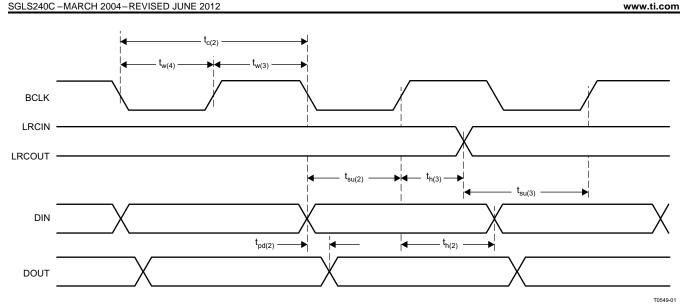

## 2.4.1 Audio Interface (Master Mode)

Figure 2-2. Master-Mode Timing Requirements

## 2.4.2 Audio Interface (Slave-Mode)

|                          | PARAMETER                   |      |    | TYP MAX | UNIT |

|--------------------------|-----------------------------|------|----|---------|------|

| tw(3)                    | Dulas duration BCLK         | High | 20 |         |      |

| tw(4)                    | Pulse duration, BCLK        | Low  | 20 |         | ns   |

| tc(2)                    | 2) Clock period, BCLK       |      | 50 |         | ns   |

| tpd(4)                   | (4) Propagation delay, DOUT |      | 0  | 10      | ns   |

| tsu(2)                   | 2) Setup time, DIN          |      | 10 |         | ns   |

| th(2)                    | h(2) Hold time, DIN         |      | 10 |         | ns   |

| tsu(3) Setup time, LRCIN |                             | 10   |    | ns      |      |

| th(3)                    | Hold time, LRCIN            |      | 10 |         | ns   |

Copyright © 2004–2012, Texas Instruments Incorporated

T0548-01

ÈXAS NSTRUMENTS

SGLS240C -MARCH 2004-REVISED JUNE 2012

Figure 2-3. Slave-Mode Timing Requirements

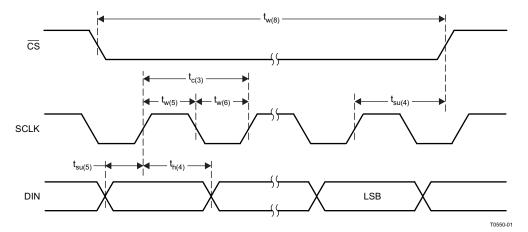

## 2.4.3 3-Wire Control Interface (SDIN)

|        | PARAMETER                      |              | MIN | ТҮР | MAX | UNIT |

|--------|--------------------------------|--------------|-----|-----|-----|------|

| tw(5)  | Clock pulse duration SCLK      | High         | 20  |     |     | 20   |

| tw(6)  | Clock pulse duration, SCLK     | Low          | 20  |     |     | ns   |

| tc(3)  | Clock period, SCLK             |              | 80  |     |     | ns   |

| tsu(4) | Clock rising edge to CS risin  | g edge, SCLK | 60  |     |     | ns   |

| tsu(5) | ) Setup time, SDIN to SCLK     |              | 20  |     |     | ns   |

| th(4)  | Hold time, SCLK to SDIN        |              | 20  |     |     | ns   |

| tw(7)  | Dulas duration $\frac{1}{100}$ | High         | 20  |     |     |      |

| tw(8)  | Pulse duration, CS             | Low          | 20  |     |     | ns   |

Figure 2-4. 3-Wire Control Interface Timing Requirements

## www.ti.com

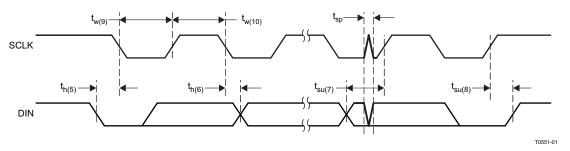

## 2.4.4 2-Wire Control Interface

|        |                                                | PARAMETER          | MIN | TYP | MAX | UNIT |

|--------|------------------------------------------------|--------------------|-----|-----|-----|------|

| tw(9)  | Clash sulas duration COLK                      | High               | 1.3 |     |     | μs   |

| tw(10) | <ul> <li>Clock pulse duration, SCLK</li> </ul> | Low                | 600 |     |     | ns   |

| f(sf)  | Clock frequency, SCLK                          |                    | 0   |     | 400 | kHz  |

| th(5)  | Hold time (start condition)                    |                    | 600 |     |     | ns   |

| tsu(6) | Setup time (start condition)                   |                    | 600 |     |     | ns   |

| th(6)  | Data hold time                                 |                    |     |     | 900 | ns   |

| tsu(7) | Data setup time                                |                    | 100 |     |     | ns   |

| tr     | Rise time, SDIN, SCLK                          |                    |     |     | 300 | ns   |

| tf     | Fall time, SDIN, SCLK                          |                    |     |     | 300 | ns   |

| tsu(8) | Setup time (stop condition)                    |                    | 600 |     |     | ns   |

| tsp    | Pulse width of spikes suppress                 | ed by input filter |     | 0   | 50  | ns   |

Figure 2-5. 2-Wire Control Interface Timing Requirements

## TEXAS INSTRUMENTS

www.ti.com

## 3 How to Use the TLV320AIC23B-Q1

## 3.1 Control Interfaces

The TLV320AIC23B-Q1 has many programmable features. The control interface is used to program the registers of the device. The control interface complies with SPI (3-wire operation) and 2-wire operation specifications. The state of the MODE terminal selects the control interface type. The MODE pin must be hardwired to the required level.

| MODE | INTERFACE |

|------|-----------|

| 0    | 2-wire    |

| 1    | SPI       |

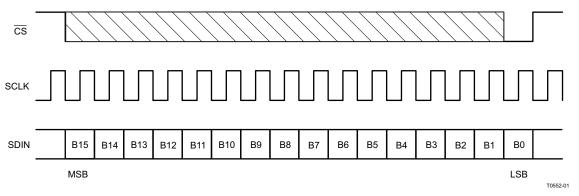

## 3.1.1 SPI

In SPI mode, SDIN carries the serial data, SCLK is the serial clock and CS latches the data word into the TLV320AIC23B-Q1. The interface is compatible with microcontrollers and DSPs with an SPI interface.

A control word consists of 16 bits, starting with the MSB. The data bits are latched on the rising edge of SCLK. A rising edge on CS after the 16th rising clock edge latches the data word into the AIC (see Figure 3-1).

The control word is divided into two parts. The first part is the address block, the second part is the data block:

B[15:9] Control Address Bits

B[8:0] Control Data Bits

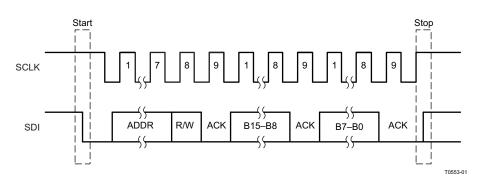

## 3.1.2 2-Wire

In 2-wire mode, the data transfer uses SDIN for the serial data and SCLK for the serial clock. The start condition is a falling edge on SDIN while SCLK is high. The seven bits following the start condition determine which device on the 2-wire bus receives the data. R/W determines the direction of the data transfer. The TLV320AIC23B-Q1 is a write only device and responds only if R/W is 0. The device operates only as a slave device whose address is selected by setting the state of the CS pin as follows.

| CS STATE<br>(Default = 0) | ADDRESS |

|---------------------------|---------|

| 0                         | 0011010 |

| 1                         | 0011011 |

The device that recognizes the address responds by pulling SDIN low during the ninth clock cycle, acknowledging the data transfer. The control follows in the next two eight-bit blocks. The stop condition after the data transfer is a rising edge on SDIN when SCLK is high (see Figure 3-2).

The 16-bit control word is divided into two parts. The first part is the address block, the second part is the data block:

B[15:9] Control Address Bits

B[8:0] Control Data Bits

Figure 3-2. 2-Wire Compatible Timing

#### 3.1.3 Register Map

The TLV320AIC23B-Q1 has the following set of registers, which are used to program the modes of operation. To minimize corruption and potential noise injection due to improper sequencing, program the registers while the device is powered down (Register 0x06, value 0x80). After the registers are programmed, power on the device (Register 0x06, value 0x28).

| ADDRESS | REGISTER                                |

|---------|-----------------------------------------|

| 000000  | Left line input channel volume control  |

| 0000001 | Right line input channel volume control |

| 0000010 | Left channel headphone volume control   |

| 0000011 | Right channel headphone volume control  |

| 0000100 | Analog audio path control               |

| 0000101 | Digital audio path control              |

| 0000110 | Power down control                      |

| 0000111 | Digital audio interface format          |

| 0001000 | Sample rate control                     |

| 0001001 | Digital interface activation            |

| 0001111 | Reset register                          |

| Table 3-1. Left Line Input Channel Volume Control (Address: 00000 |

|-------------------------------------------------------------------|

|-------------------------------------------------------------------|

| BIT      | D8  | D7  | D6 | D5 | D4   | D3   | D2   | D1   | D0   |

|----------|-----|-----|----|----|------|------|------|------|------|

| Function | LRS | LIM | Х  | х  | LIV4 | LIV3 | LIV2 | LIV1 | LIV0 |

| Default  | 0   | 1   | 0  | 0  | 1    | 0    | 1    | 1    | 1    |

| LRS      | Left/right line simultaneous volume/mute update       |                      |             |  |  |

|----------|-------------------------------------------------------|----------------------|-------------|--|--|

|          | Simultaneous update                                   | 0 = Disabled         | 1 = Enabled |  |  |

| LIM      | Left line input mute                                  | 0 = Normal           | 1 = Muted   |  |  |

| LIV[4:0] | Left line input volume control (10111 = 0 dB default) |                      |             |  |  |

|          | 11111 = 12 dB down to 00000                           | = -34.5 dB in 1.5-dE | 3 steps     |  |  |

| Х        | Reserved                                              |                      |             |  |  |

Copyright © 2004–2012, Texas Instruments Incorporated

#### SGLS240C - MARCH 2004 - REVISED JUNE 2012

RUMENTS

| BIT      | D8  | D7  | D6 | D5 | D4   | D3   | D2   | D1   | D0   |

|----------|-----|-----|----|----|------|------|------|------|------|

| Function | RLS | RIM | х  | х  | RIV4 | RIV3 | RIV2 | RIV1 | RIV0 |

| Default  | 0   | 1   | 0  | 0  | 1    | 0    | 1    | 1    | 1    |

RLS Right/left line simultaneous volume/mute update

Simultaneous update 0 = Disabled 1 = Enabled

RIM Right line input mute 0 = Normal 1 = Muted

RIV[4:0] Right line input volume control (10111 = 0 dB default)

11111 = 12 dB down to 00000 = -34.5 dB in 1.5-dB steps

X Reserved

## Table 3-3. Left Channel Headphone Volume Control (Address: 0000010)

| BIT      | D8  | D7  | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|----------|-----|-----|------|------|------|------|------|------|------|

| Function | LRS | LZC | LHV6 | LHV5 | LHV4 | LHV3 | LHV2 | LHV1 | LHV0 |

| Default  | 0   | 1   | 1    | 1    | 1    | 1    | 0    | 0    | 1    |

LRS Left/right headphone channel simultaneous volume/mute update Simultaneous update 0 = Disabled 1 = Enabled

LZC Left channel zero-cross detect

Zero-cross detect 0 = Off 1 = On

LHV[6:0] Left Headphone volume control (1111001 = 0 dB default)

1111111 = 6 dB, 79 steps between 6 dB and −73 dB (mute), 0110000 = −73 dB (mute), anything below 0110000 does nothing − you are still muted

## Table 3-4. Right Channel Headphone Volume Control (Address: 0000011)

|          | 1   |     | -    | -    |      |      |      | -    |      |

|----------|-----|-----|------|------|------|------|------|------|------|

| BIT      | D8  | D7  | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

| Function | RLS | RZC | RHV6 | RHV5 | RHV4 | RHV3 | RHV2 | RHV1 | RHV0 |

| Default  | 0   | 1   | 1    | 1    | 1    | 1    | 0    | 0    | 1    |

LRS Right/left headphone channel simultaneous volume/mute update Simultaneous update 0 = Disabled 1 = Enabled

Simultaneous update 0 = RZC Right channel zero-cross detect

Zero-cross detect 0 = Off 1 = On

RHV[6:0] Right headphone volume control (1111001 = 0 dB default)

1111111 = 6 dB, 79 steps between 6 dB and -73 dB (mute), 0110000 = -73 dB (mute), any thing below 0110000 does nothing – you are still muted

SGLS240C - MARCH 2004 - REVISED JUNE 2012

| BIT        | D8          | D7         | D6          |      | D5 [        | 04     | D3  | D2    | D1   | D0   |

|------------|-------------|------------|-------------|------|-------------|--------|-----|-------|------|------|

| Function   | STA2        | STA1       | STA0        | 5    | STE [       | DAC    | BYP | INSEL | MICM | MICE |

| Default    | 0           | 0          | 0           | C    | ) 1         |        | 1   | 0     | 1    | 0    |

| STA[2:0] a | nd STE      |            |             |      |             |        |     |       |      |      |

|            | STE         | STA2       | STA1        | STA0 | ADDED SI    | DETONE |     |       |      |      |

|            | 1           | 1          | Х           | Х    | 0 d         | В      |     |       |      |      |

|            | 1           | 0          | 0           | 0    | -6 d        | IB     |     |       |      |      |

|            | 1           | 0          | 0           | 1    | -9 d        | IB     |     |       |      |      |

|            | 1           | 0          | 1           | 0    | -12 (       | dB     |     |       |      |      |

|            | 1           | 0          | 1           | 1    | -18 (       | dB     |     |       |      |      |

|            | 0           | Х          | Х           | Х    | Disab       | oled   |     |       |      |      |

| DAC        | DAC selec   | t          | 0 = DAC of  | ff   | 1 = DAC se  | lected |     |       |      |      |

| BYP        | Bypass      |            | 0 = Disable | ed   | 1 = Enableo | ł      |     |       |      |      |

| INSEL      | Input selec | ct for ADC | 0 = Line    |      | 1 = Microph | none   |     |       |      |      |

| MICM       | Microphon   | e mute     | 0 = Norma   | l    | 1 = Muted   |        |     |       |      |      |

| MICB       | Microphon   | e boost    | 0 = dB      |      | 1 = 20 dB   |        |     |       |      |      |

| Х          | Reserved    |            |             |      |             |        |     |       |      |      |

## Table 3-5. Analog Audio Path Control (Address: 0000100)

## Table 3-6. Digital Audio Path Control (Address: 0000101)

| BIT                              | D8 | D7         | D6                                            | D5                                        | D4           | D3         | D2     | D1     | D0    |

|----------------------------------|----|------------|-----------------------------------------------|-------------------------------------------|--------------|------------|--------|--------|-------|

| Function                         | Х  | Х          | х                                             | х                                         | х            | DACM       | DEEMP1 | DEEMP0 | ADCHP |

| Default                          | 0  | 0          | 0                                             | 0                                         | 0            | 0          | 1      | 0      | 0     |

| DACM<br>DEEMP[1:0]<br>ADCHP<br>X | •  | is control | 0 = Disabled<br>00 = Disabled<br>1 = Disabled | 1 = Enabled<br>01 = 32 kHz<br>0 = Enabled | 10 = 44.1 kl | Hz 11 = 48 | s kHz  |        |       |

| BIT D         | 08         | D7     | D6      | D5  | D4  | D3  | D2  | D1  | D0   |

|---------------|------------|--------|---------|-----|-----|-----|-----|-----|------|

| Function X    | (          | OFF    | CLK     | OSC | OUT | DAC | ADC | MIC | LINE |

| Default 0     |            | 0      | 0       | 0   | 0   | 0   | 1   | 1   | 1    |

| OFF Device    | power      | 0 = On | 1 = Off |     |     |     |     |     |      |

| CLK Clock     |            | 0 = On | 1 = Off |     |     |     |     |     |      |

| OSC Oscillat  | tor        | 0 = On | 1 = Off |     |     |     |     |     |      |

| OUT Outputs   | S          | 0 = On | 1 = Off |     |     |     |     |     |      |

| DAC DAC       |            | 0 = On | 1 = Off |     |     |     |     |     |      |

| ADC ADC       |            | 0 = On | 1 = Off |     |     |     |     |     |      |

| MIC Microph   | hone input | 0 = On | 1 = Off |     |     |     |     |     |      |

| LINE Line inp | put        | 0 = On | 1 = Off |     |     |     |     |     |      |

| X Reserv      | ved        |        |         |     |     |     |     |     |      |

### Table 3-7. Power Down Control (Address: 0000110)

#### SGLS240C - MARCH 2004 - REVISED JUNE 2012

TEXAS INSTRUMENTS

www.ti.com

| Table 3-8. Digital Audio I | nterface Format | (Address: | 0000111) |  |

|----------------------------|-----------------|-----------|----------|--|

|----------------------------|-----------------|-----------|----------|--|

| BIT      | D8 D7              |      | D6                | D5                 | D4            | D3             | D2              | D1   | D0   |

|----------|--------------------|------|-------------------|--------------------|---------------|----------------|-----------------|------|------|

| Function | X X                |      | MS                | LRSWAP             | LRP           | IWL1           | IWL0            | FOR1 | FOR0 |

| Default  | 0 0                |      | 0                 | 0                  | 0             | 0              | 0               | 0    | 1    |

| MS       | Maser/slave mode   | 0    | = Slave           | 1 = Master         |               |                |                 |      |      |

| RSWAP    | DAC left/right swa | o 0  | = Disabled        | 1 = Enabled        |               |                |                 |      |      |

| LRP      | DAC left/right pha | se O | = Right chan      | nel on, LRCIN I    | nigh          |                |                 |      |      |

|          | 0 1                | 1    | = Right chan      | nel on, LRCIN I    | ow            |                |                 |      |      |

|          |                    | D    | SP mode           |                    |               |                |                 |      |      |

|          |                    | 1    | = MSB is ava      | ailable on secor   | nd BCLK risin | ng edge after  | LRCIN rising e  | dae  |      |

|          |                    | 0    | = MSB is ava      | ailable on first B | CLK rising e  | edge after LRC | CIN rising edge |      |      |

| IWL[1:0] | Input bit length   | 00   | ) = 16 bit        | 01 = 20 bit        | 10 = 24 bit   | 11 = 32 bit    | 0 0             |      |      |

| FOR[1:0] | Data format        | 11   | I = DSP form      | nat, frame sync i  | followed by t | wo data word   | S               |      |      |

|          |                    | 10   | $ = I^2 S $ forma | t, MSB first, left | - 1 aligned   |                |                 |      |      |

|          |                    | 01   | I = MSB first,    | , left aligned     | 0             |                |                 |      |      |

|          |                    | 00   | ) = MSB first,    | , right aligned    |               |                |                 |      |      |

| V        | Deserved           |      |                   | 5 0                |               |                |                 |      |      |

#### X Reserved

NOTES: 1. In master mode, the TLV320AIC23B-Q1 supplies the BCLK, LRCOUT, and LRCIN. In slave mode, BCLK, LRCOUT, and LRCIN are supplied to the TLV320AIC23B-Q1.

2. In normal mode, BCLK = MCLK/4 for all sample rates except for 88.2 kHz and 96 kHz. For 88.2 kHz and 96 kHz sample rate, BCLK = MCLK.

3. In USB mode, bit BCLK = MCLK

#### Table 3-9. Sample Rate Control (Address: 0001000)

| BIT      | D8       | D7              | D6               | D5          | D4              | D3  | D2  | D1   | D0             |

|----------|----------|-----------------|------------------|-------------|-----------------|-----|-----|------|----------------|

| Function | Х        | CLKOUT          | CLKIN            | SR3         | SR2             | SR1 | SR0 | BOSR | USB/Norma<br>I |

| Default  | 0        | 0               | 0                | 1           | 0               | 0   | 0   | 0    | 0              |

| CLKIN    | Clock i  | nput divider    | 0 = MCLK         | 1 = MC      | CLK/2           |     |     |      |                |

| CLKOUT   | Clock of | output divider  | 0 = MCLK         | 1 = MC      | CLK/2           |     |     |      |                |

| SR[3:0]  | Sampli   | ng rate control | (see Section 3.3 | 3.2.1 and S | ection 3.3.2.2) | )   |     |      |                |

| BOSR     | Base o   | versampling rat | e                |             |                 |     |     |      |                |

| BOSR       | Base oversampling rate |                        |                        |

|------------|------------------------|------------------------|------------------------|

|            | USB mode:              | $0 = 250 f_{s}$        | 1 = 272 f <sub>s</sub> |

|            | Normal mode:           | 0 = 256 f <sub>s</sub> | 1 = 384 f <sub>s</sub> |

| USB/Normal | Clock mode select:     | 0 = Normal             | 1 = USB                |

| Х          | Reserved               |                        |                        |

#### Table 3-10. Digital Interface Activation (Address: 0001001)

| BIT      | D8 | D7  | D6  | D5 | D4 | D3 | D2 | D1 | D0  |

|----------|----|-----|-----|----|----|----|----|----|-----|

| Function | х  | RES | RES | Х  | Х  | х  | Х  | Х  | ACT |

| Default  | 0  | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0   |

ACT Activate interface 0 = Inactive 1 = Active

X Reserved

#### Table 3-11. Reset Register (Address: 0001111)

| BIT      | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Function | RES |

| Default  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

RES Write 00000000 to this register triggers reset

## 3.2 Analog Interface

## 3.2.1 Line Inputs

The TLV320AIC23B-Q1 has line inputs for the left and the right audio channels (RLINEIN and LLINEIN). Both line inputs have independently programmable volume controls and mutes. Active and passive filters for the two channels prevent high frequencies from folding back into the audio band.

The line-input gain is logarithmically adjustable from 12 dB to -34.5 dB in 1.5-dB steps. The ADC full-scale range is 1 V<sub>RMS</sub> at AV<sub>DD</sub> = 3.3 V. The full-scale range tracks linearly with analog supply voltage AV<sub>DD</sub>. To avoid distortions, it is important not to exceed the full-scale range.

The gain is independently programmable on both left and right line-inputs. To reduce the number of software write cycles required. Both channels can be locked to the same value by setting the RLS and LRS bits (see Section 3.1.3).

The line inputs are biased internally to VMID. When the line inputs are muted or the device is set to standby mode, the line inputs are kept biased to VMID using special antithump circuitry. This reduces audible clicks that otherwise might be heard when reactivating the inputs.

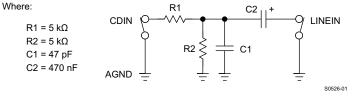

For interfacing to a CD system, the line input should be scaled to 1  $V_{RMS}$  to avoid clipping, using the circuit shown in Figure 3-3.

Figure 3-3. Analog Line Input Circuit

R1 and R2 divide the input signal by two, reducing the 2  $V_{RMS}$  from the CD player to the nominal 1  $V_{RMS}$  of the AIC23B inputs. The C1 filters high-frequency noise, and C2 removes any dc component from the signal.

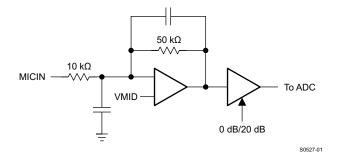

## 3.2.2 Microphone Input

MICIN is a high-impedance, low-capacitance input that is compatible with a wide range of microphones. It has a programmable volume control and a mute function. Active and passive filters prevent high frequencies from folding back into the audio band.

The MICIN signal path has two gain stages. The first stage has a nominal gain of G1 = 50 k/10 k = 5. By adding an external resistor ( $R_{MIC}$ ) in series with MICIN, the gain of the first stage can be adjusted by G1 = 50 k/(10 k +  $R_{MIC}$ ). For example,  $R_{MIC}$  = 40 k gives a gain of 0 dB. The second stage has a software programmable gain of 0 dB or 20 dB (see Section 3.1.3).

Figure 3-4. Microphone Input Circuit

How to Use the TLV320AIC23B-Q1

The microphone input is biased internally to VMID. When the line inputs are muted, the MICIN input is kept biased to VMID using special antithump circuitry. This reduces audible clicks that may otherwise be heard when reactivating the input.

The MICBIAS output provides a low-noise reference voltage suitable for biasing electret type microphones and the associated external resistor biasing network. The maximum source current capability is 3 mA. This limits the smallest value of external biasing resistors that safely can be used.

The MICBIAS output is not active in standby mode.

## 3.2.3 Line Outputs

The TLV320AIC23B-Q1 has two low-impedance line outputs (LLINEOUT and RLINEOUT) capable of driving line loads with  $10-k\Omega$  and 50-pF impedances.

The DAC full-scale output voltage is 1  $V_{RMS}$  at  $AV_{DD} = 3.3$  V. The full-scale range tracks linearly with the analog supply voltage  $AV_{DD}$ . The DAC is connected to the line outputs via a low-pass filter that removes out-of-band components. No further external filtering is required in most applications.

The DAC outputs, line inputs, and the microphone signal are summed into the line outputs. These sources can be switched off independently. For example, in bypass mode, the line inputs are routed to the line outputs, bypassing the ADC and the DAC. If sidetone is enabled, the microphone signal is routed to both line outputs via a four-step programmable attenuation circuit.

The line outputs are muted by either muting the DAC (analog) or soft muting (digital) and disabling the bypass and sidetone paths (see Section 3.1.3).

### 3.2.4 Headphone Output

The TLV320AIC23B-Q1 has stereo headphone outputs (LHPOUT and RHPOUT), and is designed to drive 16- $\Omega$  or 32- $\Omega$  headphones. The headphone output includes a high-quality volume control and mute function.

The headphone volume is logarithmically adjustable from 6 dB to -73 dB in 1-dB steps. Writing 000000 to the volume-control registers (see Section 3.1.3) mutes the headphone output. When the headphone output is muted or the device is placed in standby mode, the dc voltage is maintained at the outputs to prevent audible clicks.

A zero-cross detection circuit is provided under the control of the LZC and RZC bits. If this circuit is enabled, the volume-control values are updated only when the input signal to the gain stage is close to the analog ground level.

This minimizes audible clicks as the volume is changed or the device is muted. This circuit has no timeout, so, if only dc levels are being applied to the gain stage input of more than 20 mV, the gain is not updated.

The gain is independently programmable on the left and right channels. Both channels can be locked to the same value by setting the RLS and LRS bits (see Section 3.1.3).

## 3.2.5 Analog Bypass Mode

The TLV320AIC23B-Q1 includes a bypass mode in which the analog line inputs are directly routed to the analog line outputs, bypassing the ADC and DAC. This is enabled by selecting the bypass bit in the analog audio path control register (see Section 3.1.3).

For a true bypass mode, the output from the DAC and the sidetone should be disabled. The line input and headphone output volume controls and mutes are still operational in bypass mode. Therefore the line inputs, DAC output, and microphone input can be summed together. The maximum signal at any point in the bypass path must be no greater than 1  $V_{RMS}$  at  $AV_{DD} = 3.3$  V to avoid clipping and distortion. This amplitude tracks linearly with  $AV_{DD}$ .

www.ti.com

## 3.2.6 Sidetone Insertion

The TLV320AIC23B-Q1 has a sidetone insertion made where the microphone input is routed to the line and headphone outputs. This is useful for telephony and headset applications. The attenuation of the sidetone signal may be set to  $-6 \, dB$ ,  $-9 \, dB$ ,  $-12 \, dB$ ,  $-15 \, dB$ , or 0 dB, by software selection (see Section 3.1.3). If this mode is used to sum the microphone input with the DAC output and line inputs, care must be taken not to exceed signal level to avoid clipping and distortion.

## 3.3 Digital Audio Interface

## 3.3.1 Digital Audio-Interface Modes

The TLV320AIC23B-Q1 supports four audio-interface modes.

- Right justified

- Left justified

- I<sup>2</sup>S mode

- DSP mode

The four modes are MSB first and operate with a variable word width between 16 to 32 bits (except rightjustified mode, which does not support 32 bits).

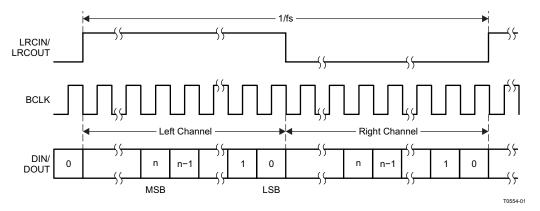

The digital audio interface consists of clock signal BCLK, data signals DIN and DOUT, and synchronization signals LRCIN and LRCOUT. BCLK is an output in master mode and an input in slave mode.

### 3.3.1.1 Right-Justified Mode

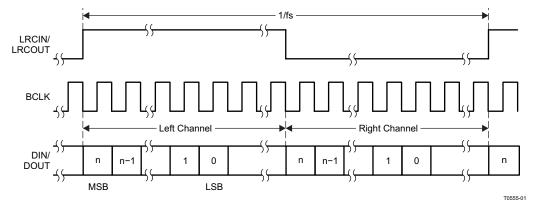

In right-justified mode, the LSB is available on the rising edge of BCLK, preceding a falling edge on LRCIN or LRCOUT (see Figure 3-5).

Figure 3-5. Right-Justified Mode Timing

## 3.3.1.2 Left-Justified Mode

In left-justified mode, the MSB is available on the rising edge of BCLK, following a rising edge on LRCIN or LRCOUT (see Figure 3-6).

Texas Instruments

SGLS240C - MARCH 2004 - REVISED JUNE 2012

www.ti.com

Figure 3-6. Left-Justified Mode Timing

## 3.3.1.3 I<sup>2</sup>S Mode

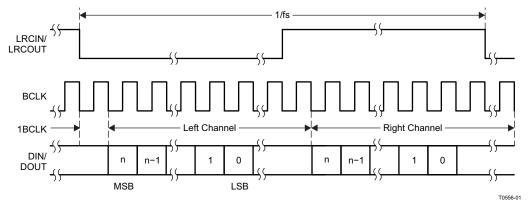

In I<sup>2</sup>S mode, the MSB is available on the second rising edge of BCLK, after the falling edge on LRCIN or LRCOUT (see Figure 3-7).

Figure 3-7. I<sup>2</sup>S Mode Timing

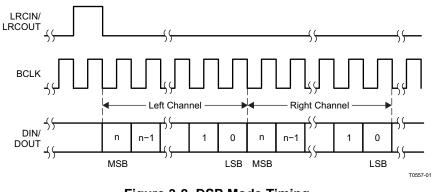

## 3.3.1.4 DSP Mode

The DSP mode is compatible with the McBSP ports of TI DSPs. LRCIN and LRCOUT must be connected to the Frame Sync signal of the McBSP. A falling edge on LRCIN or LRCOUT starts the data transfer. The left-channel data consists of the first data word, which is immediately followed by the right channel data word (see Figure 3-8). Input word length is defined by the IWL register. Figure 3-8 shows LRP = 1 (default LRP = 0).

### 3.3.2 Audio Sampling Rates

The TLV320AIC23B-Q1 can operate in master or slave clock mode. In the master mode, the TLV320AIC23B-Q1 clock and sampling rates are derived from a 12-MHz MCLK signal. This 12-MHz clock signal is compatible with the USB specification. The TLV320AIC23B-Q1 can be used directly in a USB system.

In the slave mode, an appropriate MCLK or crystal frequency and the sample rate control register settings control the TLV320AIC23B-Q1 clock and sampling rates.

The settings in the sample rate control register control the clock mode and sampling rates.

| BIT        | D8                                                        | D7                                       | D6            | D5          | D4       | D3  | D2  | D1   | D0         |

|------------|-----------------------------------------------------------|------------------------------------------|---------------|-------------|----------|-----|-----|------|------------|

| Function   | Х                                                         | CLKOUT                                   | CLKIN         | SR3         | SR2      | SR1 | SR0 | BOSR | USB/Normal |

| Default    | 0                                                         | 0                                        | 0             | 1           | 0        | 0   | 0   | 0    | 0          |

| CLKIN      | Clock                                                     | input divider                            | 0 = MCLK      | 1 = M0      | CLK/2    |     |     |      |            |

| CLKOUT     | Clock                                                     | Clock output divider 0 = MCLK 1 = MCLK/2 |               |             |          |     |     |      |            |

| SR[3:0]    | Samp                                                      | ling rate control                        | (see Sections | 3.3.2.1 AND | 3.3.2.2) |     |     |      |            |

| BOSR       | Base                                                      | oversampling ra                          | ate           |             |          |     |     |      |            |

|            | USB mode: $0 = 250 \text{ f}_{s}$ $1 = 272 \text{ f}_{s}$ |                                          |               |             |          |     |     |      |            |

|            | Normal mode: $0 = 256 f_s$ $1 = 384 f_s$                  |                                          |               |             |          |     |     |      |            |

| USB/Normal | Clock mode select: 0 = Normal 1 = USB                     |                                          |               |             |          |     |     |      |            |

| x          | Reser                                                     | ved                                      |               |             |          |     |     |      |            |

|  | Table 3-12. Sam | ple Rate Control | (Address: 0001000) |

|--|-----------------|------------------|--------------------|

|--|-----------------|------------------|--------------------|

The clock circuit of the AIC23B has two internal dividers. The first, controlled by CLKIN, applies to the sampling-rate generator of the codec. The second, controlled by CLKOUT, applies only to the CLKOUT terminal. By setting CLKIN to 1, the entire codec is clocked with half the frequency, effectively dividing the resulting sampling rates by two. The following sampling-rate tables are based on CLKIN = MCLK.

#### 3.3.2.1 USB-Mode Sampling Rates (MCLK = 12 MHz)

In the USB mode, the following ADC and DAC sampling rates are available:

| SAMPLIN   | SAMPLING RATE <sup>(1)</sup> |             |     | SAMPLING-RATE CONTROL SETTINGS |     |     |      |  |  |

|-----------|------------------------------|-------------|-----|--------------------------------|-----|-----|------|--|--|

| ADC (kHz) | DAC (kHz)                    | FILTER TYPE | SR3 | SR2                            | SR1 | SR0 | BOSR |  |  |

| 96        | 96                           | 3           | 0   | 1                              | 1   | 1   | 0    |  |  |

| 88.2      | 88.2                         | 2           | 1   | 1                              | 1   | 1   | 1    |  |  |

| 48        | 48                           | 0           | 0   | 0                              | 0   | 0   | 0    |  |  |

| 44.1      | 44.1                         | 1           | 1   | 0                              | 0   | 0   | 1    |  |  |

| 32        | 32                           | 0           | 0   | 1                              | 1   | 0   | 0    |  |  |

| 8.021     | 8.021                        | 1           | 1   | 0                              | 1   | 1   | 1    |  |  |

| 8         | 8                            | 0           | 0   | 0                              | 1   | 1   | 0    |  |  |

| 48        | 8                            | 0           | 0   | 0                              | 0   | 1   | 0    |  |  |

| 44.1      | 8.021                        | 1           | 1   | 0                              | 0   | 1   | 1    |  |  |

| 8         | 48                           | 0           | 0   | 0                              | 1   | 0   | 0    |  |  |

| 8.021     | 44.1                         | 1           | 1   | 0                              | 1   | 0   | 1    |  |  |

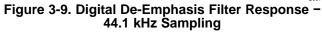

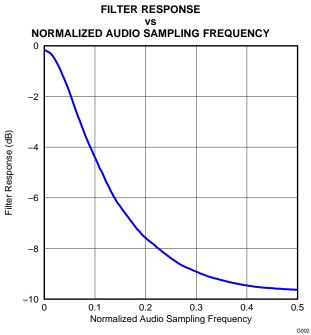

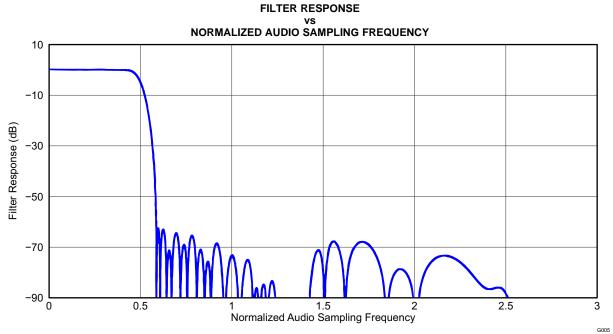

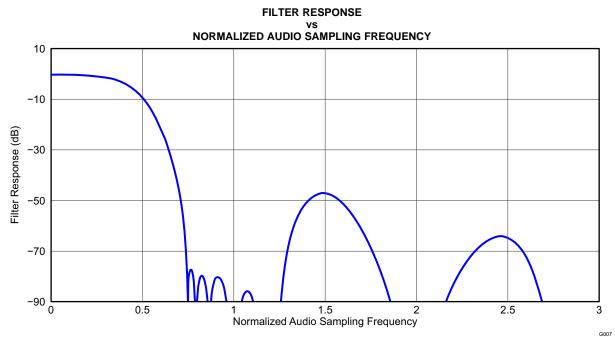

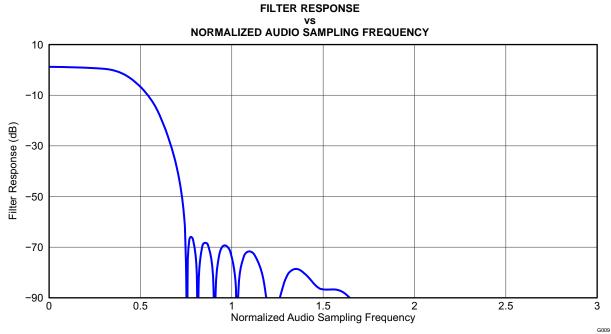

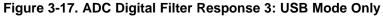

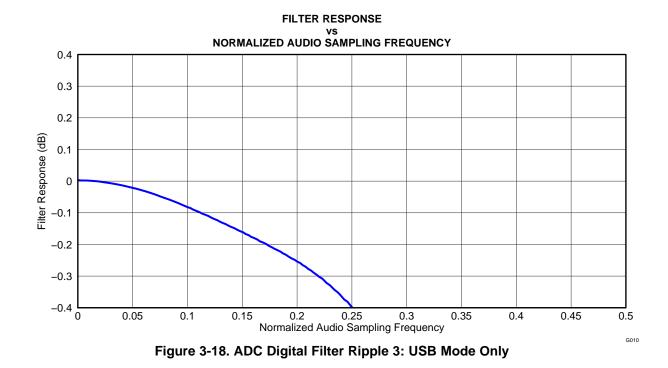

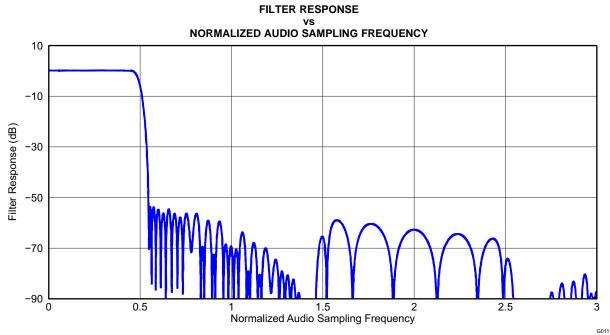

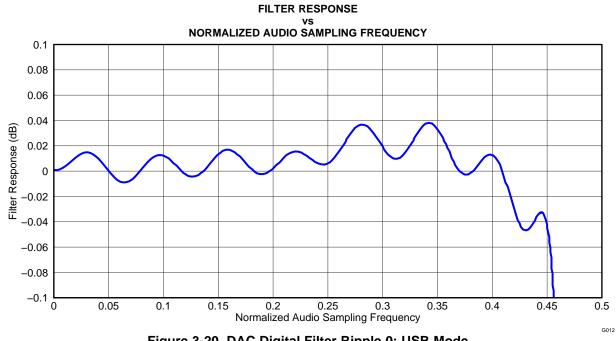

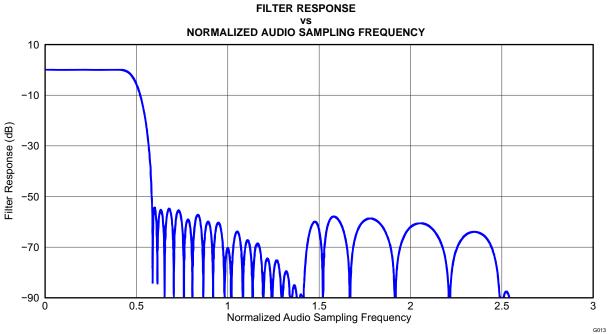

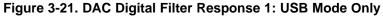

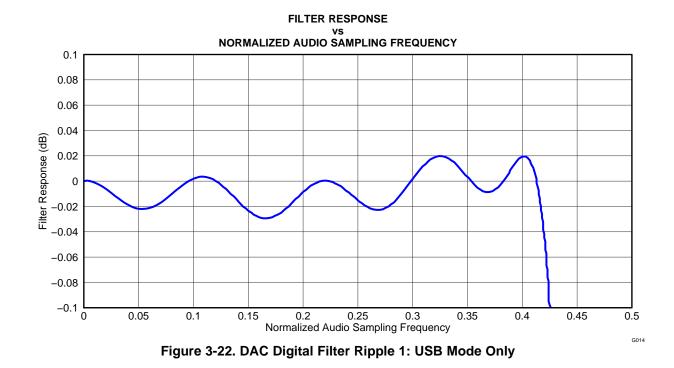

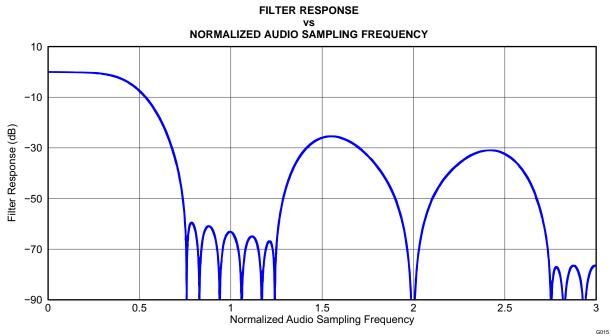

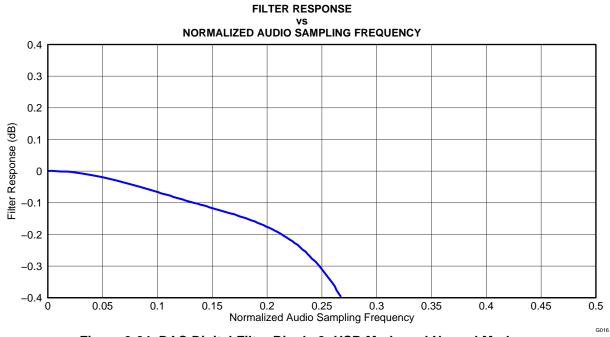

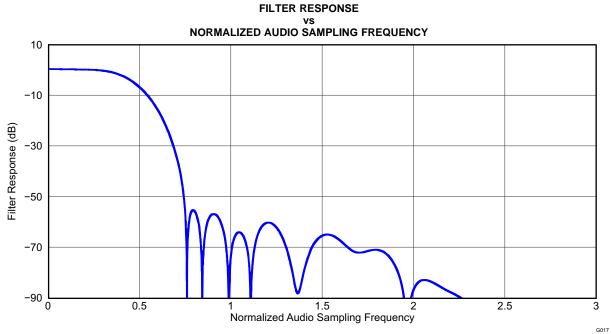

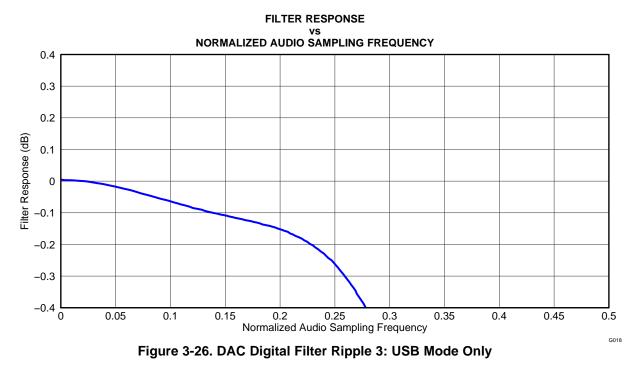

(1) The sampling rates are derived from the 12-MHz master clock. The available oversampling rates do not produce exactly 8-kHz, 44.1-kHz, and 88.2-kHz sampling rates, but 8.021 kHz, 44.117 kHz, and 88.235 kHz, respectively. See Figure 3-9 through Figure 3-26 for filter responses.

#### 3.3.2.2 Normal-Mode Sampling Rates

In normal mode, the following ADC and DAC sampling rates, depending on the MCLK frequency, are available:

www.ti.com

| Ν | ACI | K = | 12 | 288 | MHz |

|---|-----|-----|----|-----|-----|

| SAMPLI    | NG RATE   |             | SAMPLING-RATE CONTROL SETTINGS |     |     |     |      |  |  |

|-----------|-----------|-------------|--------------------------------|-----|-----|-----|------|--|--|

| ADC (kHz) | DAC (kHz) | FILTER TYPE | SR3                            | SR2 | SR1 | SR0 | BOSR |  |  |

| 96        | 96        | 2           | 0                              | 1   | 1   | 1   | 0    |  |  |

| 48        | 48        | 1           | 0                              | 0   | 0   | 0   | 0    |  |  |

| 32        | 32        | 1           | 0                              | 1   | 1   | 0   | 0    |  |  |

| 8         | 8         | 1           | 0                              | 0   | 1   | 1   | 0    |  |  |

| 48        | 8         | 1           | 0                              | 0   | 0   | 1   | 0    |  |  |

| 8         | 48        | 1           | 0                              | 0   | 1   | 0   | 0    |  |  |

### MCLK = 11.2896 MHz

| SAMPLI    | SAMPLING RATE |             | SAMPLING-RATE CONTROL SETTINGS |     |     |     |      |  |

|-----------|---------------|-------------|--------------------------------|-----|-----|-----|------|--|

| ADC (kHz) | DAC (kHz)     | FILTER TYPE | SR3                            | SR2 | SR1 | SR0 | BOSR |  |

| 88.2      | 88.2          | 2           | 1                              | 1   | 1   | 1   | 0    |  |

| 44.1      | 44.1          | 1           | 1                              | 0   | 0   | 0   | 0    |  |

| 8.021     | 8.021         | 1           | 1                              | 0   | 1   | 1   | 0    |  |

| 44.1      | 8.021         | 1           | 1                              | 0   | 0   | 1   | 0    |  |

| 8.021     | 44.1          | 1           | 1                              | 0   | 1   | 0   | 0    |  |

## MCLK = 18.432 MHz

| SAMPLI    | SAMPLING RATE |             | SAMPLING-RATE CONTROL SETTINGS |     |     |     |      |  |

|-----------|---------------|-------------|--------------------------------|-----|-----|-----|------|--|

| ADC (kHz) | DAC (kHz)     | FILTER TYPE | SR3                            | SR2 | SR1 | SR0 | BOSR |  |

| 96        | 96            | 2           | 0                              | 1   | 1   | 1   | 1    |  |

| 48        | 48            | 1           | 0                              | 0   | 0   | 0   | 1    |  |

| 32        | 32            | 1           | 0                              | 1   | 1   | 0   | 1    |  |

| 8         | 8             | 1           | 0                              | 0   | 1   | 1   | 1    |  |

| 48        | 8             | 1           | 0                              | 0   | 0   | 1   | 1    |  |

| 8         | 48            | 1           | 0                              | 0   | 1   | 0   | 1    |  |

#### MCLK = 16.9344 MHz

| SAMPLI    | NG RATE   | FILTER TYPE | SAMPLING-RATE CONTROL SETTINGS |     |     |     |      |  |

|-----------|-----------|-------------|--------------------------------|-----|-----|-----|------|--|

| ADC (kHz) | DAC (kHz) | FILTER TTPE | SR3                            | SR2 | SR1 | SR0 | BOSR |  |

| 88.2      | 88.2      | 2           | 1                              | 1   | 1   | 1   | 1    |  |

| 44.1      | 44.1      | 1           | 1                              | 0   | 0   | 0   | 1    |  |

| 8.021     | 8.021     | 1           | 1                              | 0   | 1   | 1   | 1    |  |

| 44.1      | 8.021     | 1           | 1                              | 0   | 0   | 1   | 1    |  |

| 8.021     | 44.1      | 1           | 1                              | 0   | 1   | 0   | 1    |  |

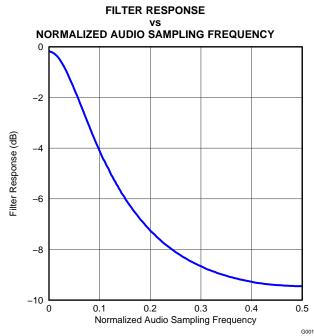

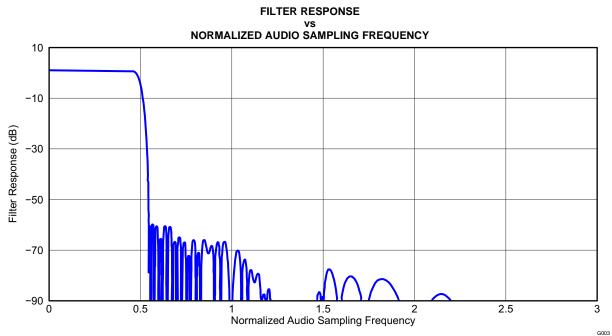

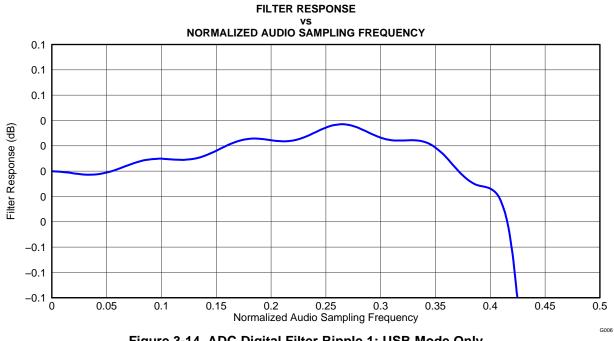

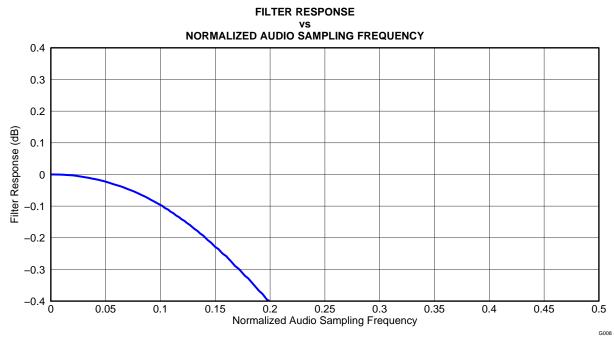

## 3.3.3 Digital Filter Characteristics

| PARAMETER                          | TEST CONDITIONS                               | MIN                   | TYP                | MAX   | UNIT |

|------------------------------------|-----------------------------------------------|-----------------------|--------------------|-------|------|

| ADC Filter Characteristics (TI DSP | 250 f <sub>s</sub> Mode Operation)            |                       |                    |       |      |

| Passband                           | ±0.05 dB                                      | 0.416 f <sub>s</sub>  |                    |       | Hz   |

| Stopband                           | 6 dB                                          |                       | 0.5 f <sub>s</sub> |       | Hz   |

| Passband ripple                    |                                               |                       |                    | ±0.05 | dB   |

| Stopband attenuation               | f > 0.584 f <sub>s</sub>                      |                       | -60                |       | dB   |

| ADC Filter Characteristics (TI DSP | 272 f <sub>s</sub> and Normal Mode Operation) |                       |                    |       |      |

| Passband                           | ±0.05 dB                                      | 0.4535 f <sub>s</sub> |                    |       | Hz   |