# 2-in-1 Notebook DDR Power Controller

The NCP5218 2-in-1 Notebook DDR Power Controller is specifically designed as a total power solution for notebook DDR memory system. This IC combines the efficiency of a PWM controller for the  $V_{DDQ}$  supply with the simplicity of linear regulators for the  $V_{TT}$  termination voltage and the buffered low noise reference. This IC contains a synchronous PWM buck controller for driving two external NFETs to form the DDR memory supply voltage ( $V_{DDQ}$ ). The DDR memory termination regulator output voltage ( $V_{TT}$ ) and the buffered  $V_{REF}$  are internally set to track at the half of  $V_{DDQ}$ . An internal power good voltage monitor tracks  $V_{DDQ}$  output and notifies the user whether the  $V_{DDQ}$  output is within target range. Protective features include soft–start circuitries, undervoltage monitoring of supply voltage,  $V_{DDQ}$  overcurrent protection,  $V_{DDQ}$  overvoltage and undervoltage protections, and thermal shutdown. The IC is packaged in DFN22.

#### **Features**

- Incorporates V<sub>DDQ</sub>, V<sub>TT</sub> Regulator, Buffered V<sub>REF</sub>

- Adjustable V<sub>DDO</sub> Output

- V<sub>TT</sub> and V<sub>REF</sub> Track V<sub>DDQ</sub>/2

- Operates from Single 5.0 V Supply

- Supports V<sub>DDQ</sub> Conversion Rails from 4.5 V to 24 V

- Power-saving Mode for High Efficiency at Light Load

- Integrated Power FETs with V<sub>TT</sub> Regulator Sourcing/Sinking 1.5 A DC and 2.4 A Peak Current

- Requires Only 20 μF Ceramic Output Capacitor for V<sub>TT</sub>

- Buffered Low Noise 15 mA V<sub>REF</sub> Output

- All External Power MOSFETs are N-channel

- <5.0 μA Current Consumption During Shutdown

- Fixed Switching Frequency of 400 kHz

- Soft-start Protection for V<sub>DDQ</sub> and V<sub>TT</sub>

- Undervoltage Monitor of Supply Voltage

- Overvoltage Protection and Undervoltage Protection for V<sub>DDO</sub>

- Short-circuit Protection for V<sub>DDQ</sub> and V<sub>TT</sub>

- Thermal Shutdown

- Housed in DFN22

- This is a Pb-Free Device

#### **Typical Applications**

- Notebook DDR/DDR2 Memory Supply and Termination Voltage

- Active Termination Busses (SSTL-18, SSTL-2, SSTL-3)

#### ON Semiconductor®

http://onsemi.com

#### MARKING DIAGRAM

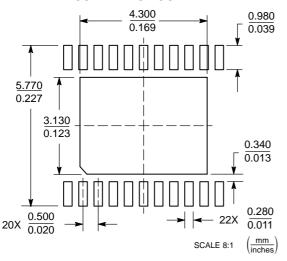

DFN22 MN SUFFIX CASE 506AF

NCP5218= Specific Device Code

= Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

Pb-Free Package

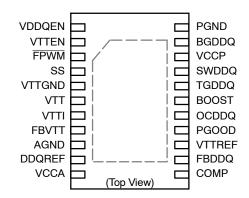

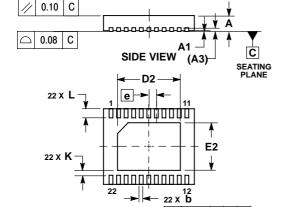

#### **PIN CONNECTIONS**

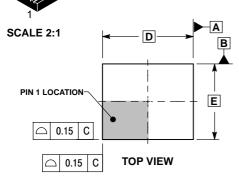

NOTE: Pin 23 is the thermal pad on the bottom of the device.

# **ORDERING INFORMATION**

| Device       | Package            | Shipping†        |

|--------------|--------------------|------------------|

| NCP5218MNR2G | DFN22<br>(Pb-Free) | 2500 Tape & Reel |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

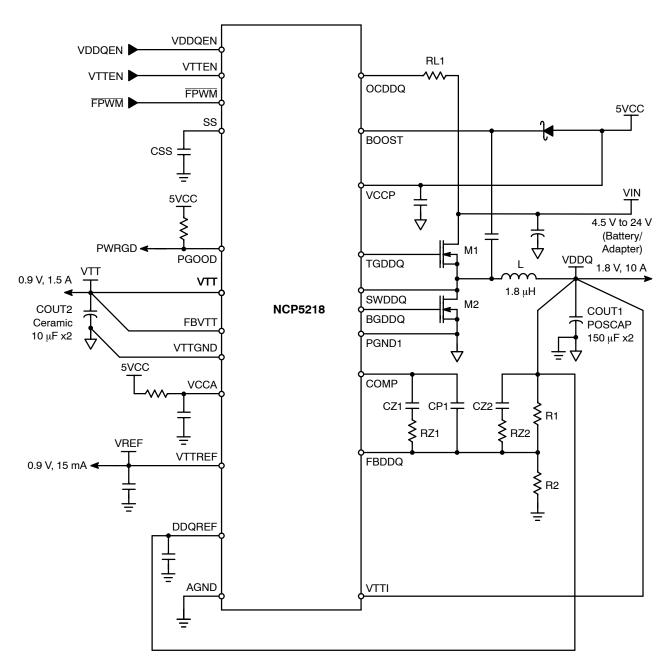

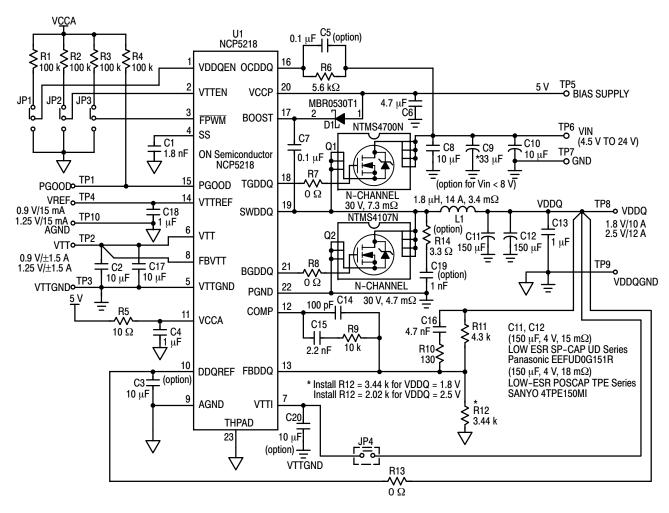

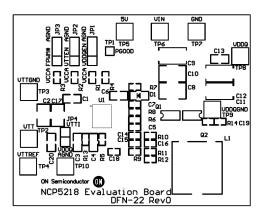

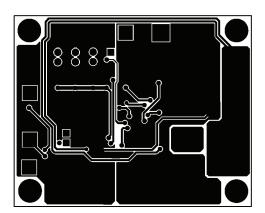

Figure 1. Typical Application Diagram

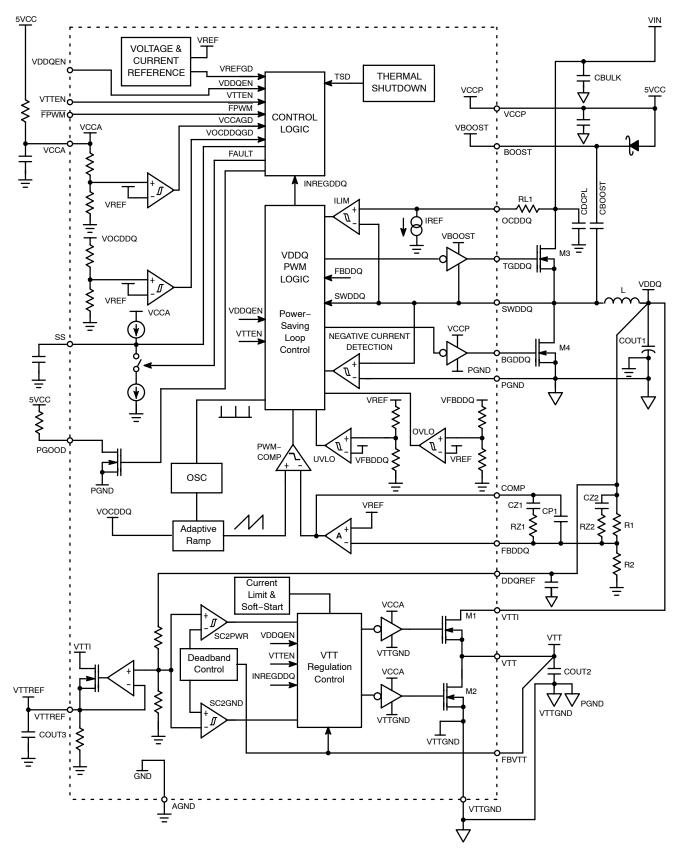

Figure 2. Detailed Block Diagram

# PIN FUNCTION DESCRIPTION

| Pin | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                 |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VDDQEN | V <sub>DDQ</sub> regulator enable input. High to enable.                                                                                                                                                                                                                                                                                                                    |

| 2   | VTTEN  | V <sub>TT</sub> regulator enable input. High to enable.                                                                                                                                                                                                                                                                                                                     |

| 3   | FPWM   | Forced PWM enable input. Low to enable forced PWM mode and disable power-saving mode.                                                                                                                                                                                                                                                                                       |

| 4   | SS     | V <sub>DDQ</sub> Soft-start capacitor connection to ground.                                                                                                                                                                                                                                                                                                                 |

| 5   | VTTGND | Power ground for the $V_{TT}$ regulator.                                                                                                                                                                                                                                                                                                                                    |

| 6   | VTT    | V <sub>TT</sub> regulator output.                                                                                                                                                                                                                                                                                                                                           |

| 7   | VTTI   | Power input for $V_{TT}$ regulator which is normally connected to the $V_{DDQ}$ output of the buck regulator.                                                                                                                                                                                                                                                               |

| 8   | FBVTT  | V <sub>TT</sub> regulator feedback pin for closed loop regulation.                                                                                                                                                                                                                                                                                                          |

| 9   | AGND   | Analog ground connection and remote ground sense.                                                                                                                                                                                                                                                                                                                           |

| 10  | DDQREF | External reference input which is used to regulate V <sub>TT</sub> and V <sub>TTREF</sub> to 1/2V <sub>DDQREF</sub>                                                                                                                                                                                                                                                         |

| 11  | VCCA   | 5.0 V supply input for the IC's control and logic section, which is monitored by undervoltage lock out circuitry.                                                                                                                                                                                                                                                           |

| 12  | COMP   | V <sub>DDQ</sub> error amplifier compensation node.                                                                                                                                                                                                                                                                                                                         |

| 13  | FBDDQ  | V <sub>DDQ</sub> regulator feedback pin for closed loop regulation.                                                                                                                                                                                                                                                                                                         |

| 14  | VTTREF | DDR reference voltage output.                                                                                                                                                                                                                                                                                                                                               |

| 15  | PGOOD  | Power good signal open-drain output.                                                                                                                                                                                                                                                                                                                                        |

| 16  | OCDDQ  | Overcurrent sense and program input for the high–side FET of V <sub>DDQ</sub> regulator. Also the battery voltage input for the internal ramp generator to implement the voltage feedforward rejection to the input voltage variation. This pin must be connected to the V <sub>IN</sub> through a resistor to perform the current limit and voltage feedforward functions. |

| 17  | BOOST  | Positive supply input for high-side gate driver of V <sub>DDQ</sub> regulator and boost capacitor connection.                                                                                                                                                                                                                                                               |

| 18  | TGDDQ  | Gate driver output for V <sub>DDQ</sub> regulator high-side N-Channel power FET.                                                                                                                                                                                                                                                                                            |

| 19  | SWDDQ  | V <sub>DDQ</sub> regulator inductor driven node, return for high-side gate driver, and current limit sense input.                                                                                                                                                                                                                                                           |

| 20  | VCCP   | Power supply for the V <sub>DDQ</sub> regulator low-side gate driver and also supply voltage for the bootstrap capacitor of the V <sub>DDQ</sub> regulator high-side gate driver supply.                                                                                                                                                                                    |

| 21  | BGDDQ  | Gate driver output for V <sub>DDQ</sub> regulator low-side N-Channel power FET.                                                                                                                                                                                                                                                                                             |

| 22  | PGND   | Power ground for the V <sub>DDQ</sub> regulator.                                                                                                                                                                                                                                                                                                                            |

| 23  | THPAD  | Copper pad on bottom of IC used for heatsinking. This pin should be connected to the ground plane under the IC.                                                                                                                                                                                                                                                             |

#### **MAXIMUM RATINGS**

| Rating                                                                                | Symbol                                     | Value                             | Unit |

|---------------------------------------------------------------------------------------|--------------------------------------------|-----------------------------------|------|

| Power Supply Voltage (Pin 11, 20) to AGND (Pin 9)                                     | V <sub>CCA</sub> , V <sub>CCP</sub>        | -0.3, 6.0                         | V    |

| High-Side Gate Drive Supply: BOOST (Pin 17) to SWDDQ (Pin 19)                         | V <sub>BOOST</sub> -V <sub>SWDDQ</sub>     | -0.3, 6.0                         | V    |

| Input/Output Pins to AGND (Pin 9) Pins 1–4, 6–8, 10, 12–15                            | V <sub>IO</sub>                            | -0.3, 6.0                         | ٧    |

| Overcurrent Sense Input (Pin 16) to AGND (Pin 9)                                      | V <sub>OCDDQ</sub>                         | 27                                | V    |

| Switch Node (Pin 19)                                                                  | V <sub>SWDDQ</sub>                         | -4.0 (<100 ns),<br>-0.3 (dc), 32  | V    |

| High-Side FET Gate Drive Voltage: TGDDQ (Pin 18) To SWDDQ (Pin 19)                    | V <sub>TGDDQ</sub> -<br>V <sub>SWDDQ</sub> | -2.0 (< 100 ns)<br>-0.3 (dc), 6.0 | ٧    |

| Low-Side FET Gate Drive Voltage: BGDDQ (Pin 21) To PGND (Pin 22)                      | $V_{BGDDQ}$                                | -2.0 (< 100 ns)<br>-0.3 (dc), 6.0 | V    |

| PGND (Pin 22), VTTGND (Pin 5) to AGND (Pin 9)                                         | $V_{GND}$                                  | -0.3, 0.3                         | V    |

| Thermal Characteristics DFN22 Plastic Package Thermal Resistance, Junction-to-Ambient | $R_{	hetaJA}$                              | 35                                | °C/W |

| Operating Junction Temperature Range                                                  | TJ                                         | 0 to +150                         | °C   |

| Operating Ambient Temperature Range                                                   | T <sub>A</sub>                             | -40 to +85                        | °C   |

| Storage Temperature Range                                                             | T <sub>stg</sub>                           | -55 to +150                       | °C   |

| Moisture Sensitivity Level                                                            | MSL                                        | 1                                 | -    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- This device series contains ESD protection and exceeds the following tests:

Human Body Model (HBM) ≤2.0 kV per JEDEC standard: JESD22–A114 except Pin 17 which is ≤ 1 kV.

Machine Model (MM) ≤200 V per JEDEC standard: JESD22–A115 except Pin 17 which is ≤ 150 V.

- 2. Latchup Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78.

- 3. Pin 16 (OCDDQ) must be pulled high to V<sub>IN</sub> through a resistor.

**ELECTRICAL CHARACTERISTICS** (V<sub>IN</sub> = 12 V, T<sub>A</sub> = -40 to 85°C, V<sub>CCA</sub> = V<sub>CCP</sub> = V<sub>BOOST</sub> - V<sub>SWDDQ</sub> = 5.0 V, L = 1.8 μH, C<sub>OUT1</sub> = 150 μF x 2, C<sub>OUT2</sub> = 22 μF x 2, RL1 = 5.6 kΩ, R1 = 4.3 kΩ, R2 = 3.3 kΩ, RZ1 = 10 kΩ, RZ2 = 130 Ω, CP1 = 100 pF, CZ1 = 2.2 nF, CZ2 = 4.7 nF, for min/max values unless otherwise noted. Typical values are at T<sub>A</sub> = 25°C.)

| Characteristic                                     | Symbol                               | Test Conditions                                                                | Min            | Тур        | Max            | Unit       |

|----------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------|----------------|------------|----------------|------------|

| SUPPLY VOLTAGE                                     |                                      |                                                                                | ·              |            |                |            |

| Input Voltage                                      | V <sub>IN</sub>                      | -                                                                              | 4.5            | -          | 24             | V          |

| V <sub>CCA</sub> Operating Voltage                 | V <sub>CCA</sub>                     | -                                                                              | 4.5            | 5.0        | 5.5            | V          |

| V <sub>CCP</sub> Operating Voltage                 | V <sub>CCP</sub>                     | -                                                                              | 4.5            | 5.0        | 5.5            | V          |

| SUPPLY CURRENT                                     |                                      |                                                                                |                |            | •              |            |

| V <sub>CCA</sub> Quiescent Supply Current in S0    | lvcca_so                             | V <sub>DDQEN</sub> = 5.0 V, V <sub>TTEN</sub> = 5.0 V                          | -              | 3.5        | 10             | mA         |

| V <sub>CCA</sub> Quiescent Supply Current in S3    | Ivcca_s3                             | V <sub>DDQEN</sub> = 5.0 V, V <sub>TTEN</sub> = 0 V                            | _              | 0.9        | 5.0            | mA         |

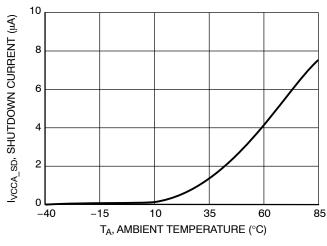

| V <sub>CCA</sub> Shutdown Current                  | I <sub>VCCA_SD</sub>                 | $V_{DDQEN} = 0 \text{ V}, V_{TTEN} = 0 \text{ V},$ $T_A = 25^{\circ}\text{C}$  | -              | 1.0        | 4.0            | μΑ         |

| V <sub>CCP</sub> Quiescent Supply Current in S0    | I <sub>VCCP_S0</sub>                 | V <sub>DDQEN</sub> = 5.0 V, V <sub>TTEN</sub> = 5.0 V,<br>TGDDQ and BGDDQ Open | -              | -          | 20             | mA         |

| V <sub>CCP</sub> Quiescent Supply Current in S3    | I <sub>VCCP_S3</sub>                 | V <sub>DDQEN</sub> = 5.0 V, V <sub>TTEN</sub> = 0 V,<br>TGDDQ and BGDDQ Open   | -              | -          | 20             | mA         |

| V <sub>CCP</sub> Shutdown Current                  | I <sub>VCCP_SD</sub>                 | V <sub>DDQEN</sub> = 0 V, V <sub>TTEN</sub> = 0 V                              | -              | 1.0        | 2.0            | μΑ         |

| UNDERVOLTAGE MONITOR                               |                                      |                                                                                |                |            | 1              |            |

| V <sub>CCA</sub> UVLO Lower Threshold              | V <sub>CCAUV</sub> -                 | Falling Edge                                                                   | _              | 3.7        | 4.1            | V          |

| V <sub>CCA</sub> UVLO Hysteresis                   | V <sub>CCAUVHYS</sub>                | -                                                                              | _              | 0.35       | -              | V          |

| V <sub>OCDDQ</sub> UVLO Upper Threshold            | V <sub>OCDDQUV+</sub>                | Rising Edge                                                                    | _              | 3.0        | 4.4            | V          |

| V <sub>OCDDQ</sub> UVLO Hysteresis                 | V <sub>OCDDQUVHYS</sub>              | -                                                                              | _              | 0.4        | -              | V          |

| THERMAL SHUTDOWN                                   |                                      |                                                                                |                |            | •              |            |

| Thermal Trip Point                                 | T <sub>SD</sub>                      | (Note 4)                                                                       | -              | 150        | -              | °C         |

| Hysteresis                                         | T <sub>SDHYS</sub>                   | (Note 4)                                                                       | -              | 25         | -              | °C         |

| V <sub>DDQ</sub> SWITCHING REGULATOR               |                                      |                                                                                |                | •          | •              |            |

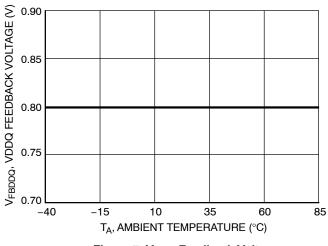

| FBDDQ Feedback Voltage, Control Loop in Regulation | V <sub>FBDDQ</sub>                   | $T_A = 25^{\circ}C$<br>$T_A = -40 \text{ to } 85^{\circ}C$                     | 0.788<br>0.784 | 0.8<br>0.8 | 0.812<br>0.816 | V          |

| Feedback Input Current                             | I <sub>fb</sub>                      | V <sub>FBDDQ</sub> = 0.8 V                                                     | _              | -          | 1.0            | μΑ         |

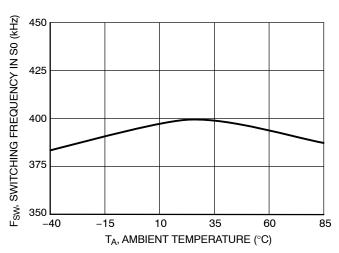

| Oscillator Frequency                               | F <sub>SW</sub>                      | -                                                                              | 340            | 400        | 460            | kHz        |

| Ramp Amplitude Voltage                             | $V_{ramp}$                           | V <sub>IN</sub> = 5.0 V (Note 4)                                               | _              | 1.25       | -              | V          |

| Ramp Amplitude to V <sub>IN</sub> Ratio            | d <sub>VRAMP</sub> /d <sub>VIN</sub> | -                                                                              | _              | 45         | -              | mV/V       |

| OCDDQ Pin Current Sink                             | I <sub>OC</sub>                      | V <sub>OCDDQ</sub> = 4.0 V                                                     | 26             | 31         | 36             | μΑ         |

| OCDDQ Pin Current Sink<br>Temperature Coefficient  | TC <sub>IOC</sub>                    | T <sub>A</sub> = -40 to 85°C                                                   | -              | 3200       | -              | ppm/<br>°C |

| Minimum On Time                                    | t <sub>onmin</sub>                   | -                                                                              | _              | 150        | _              | ns         |

| Maximum Duty Cycle                                 | D <sub>max</sub>                     | V <sub>IN</sub> = 5.0 V                                                        | -              | 90         | _              | %          |

|                                                    |                                      | V <sub>IN</sub> = 15 V<br>V <sub>IN</sub> = 24 V                               | -              | 50<br>32   | _<br>_         |            |

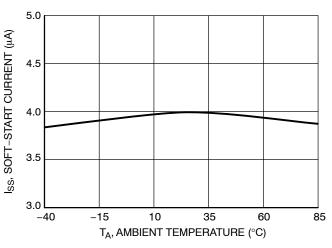

| Soft-Start Current                                 | I <sub>ss</sub>                      | V <sub>DDQEN</sub> = 5.0 V, Vss = 0 V                                          | 2.8            | 4.0        | 5.2            | μΑ         |

| Overvoltage Trip Threshold                         | FBOVP <sub>th</sub>                  | With Respect to Error<br>Comparator Threshold of 0.8 V                         | 115            | 130        | _              | %          |

| Undervoltage Trip Threshold                        | FBUVP <sub>th</sub>                  | With Respect to Error<br>Comparator Threshold of 0.8 V                         | -              | 65         | 75             | %          |

<sup>4.</sup> Guaranteed by design, not tested in production.

**ELECTRICAL CHARACTERISTICS (continued)** ( $V_{IN}$  = 12 V,  $T_A$  = -40 to 85°C,  $V_{CCA}$  =  $V_{CCP}$  =  $V_{BOOST}$  -  $V_{SWDDQ}$  = 5.0 V, L = 1.8 μH,  $C_{OUT1}$  = 150 μF x 2,  $C_{OUT2}$  = 22 μF x 2, RL1 = 5.6 kΩ, R1 = 4.3 kΩ, R2 = 3.3 kΩ, RZ1 = 10 kΩ, RZ2 = 130 Ω, CP1 = 100 pF, CZ1 = 2.2 nF, CZ2 = 4.7 nF, for min/max values unless otherwise noted. Typical values are at  $T_A$  = 25°C.)

| Characteristic                                                 | Symbol                | Test Conditions                                                                                                                                                      | Min      | Тур  | Max     | Unit |

|----------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|---------|------|

| ERROR AMPLIFIER                                                |                       |                                                                                                                                                                      |          | · ·  |         |      |

| DC Gain                                                        | GAIN                  | (Note 5)                                                                                                                                                             | -        | 70   | -       | dB   |

| Unity Gain Bandwidth                                           | Ft                    | COMP_GND = 220 nF,<br>1.0 Ω in Series (Note 5)                                                                                                                       | -        | 2.0  | -       | MHz  |

| Slew Rate                                                      | S <sub>R</sub>        | (Note 5)                                                                                                                                                             | -        | 3.0  | -       | V/μS |

| GATE DRIVERS                                                   |                       |                                                                                                                                                                      |          |      | •       |      |

| TGDDQ Gate Pull-HIGH Resistance                                | R <sub>H_TG</sub>     | $V_{BOOST} - V_{SWDDQ} = 5.0 \text{ V},$<br>$V_{TGDDQ} - V_{SWDDQ} = 4.0 \text{ V}$                                                                                  | -        | 1.8  | 4.0     | Ω    |

| TGDDQ Gate Pull-LOW Resistance                                 | R <sub>L_TG</sub>     | V <sub>BOOST</sub> - V <sub>SWDDQ</sub> = 5.0 V,<br>V <sub>TGDDQ</sub> - V <sub>SWDDQ</sub> = 1.0 V                                                                  | _        | 1.8  | 4.0     | Ω    |

| BGDDQ Gate Pull-HIGH Resistance                                | R <sub>H_BG</sub>     | V <sub>CCP</sub> = 5.0 V, V <sub>BGDDQ</sub> = 4.0 V                                                                                                                 | _        | 1.8  | 4.0     | Ω    |

| BGDDQ Gate Pull-LOW Resistance                                 | R <sub>L_BG</sub>     | V <sub>CCP</sub> = 5.0 V, V <sub>BGDDQ</sub> = 1.0 V                                                                                                                 | -        | 0.9  | 3.0     | Ω    |

| V <sub>TT</sub> ACTIVE TERMINATOR                              | •                     |                                                                                                                                                                      |          |      |         | •    |

| V <sub>TT</sub> with Respect to 1/2V <sub>DDQREF</sub>         | d <sub>VTT0</sub>     | 1/2V <sub>DDQREF</sub> - V <sub>TT</sub> , V <sub>DDQREF</sub> = 2.5 V, I <sub>VTT</sub> = 0 to 2.4 A (Sink Current) I <sub>VTT</sub> = 0 to -2.4 A (Source Current) | -30<br>- |      | -<br>30 | mV   |

|                                                                |                       | 1/2V <sub>DDQREF</sub> - V <sub>TT</sub> , V <sub>DDQREF</sub> = 1.8 V, I <sub>VTT</sub> = 0 to 2.0 A (Sink Current) I <sub>VTT</sub> = 0 to -2.0 A (Source Current) | -30<br>- | -    | -<br>30 | mV   |

| DDQREF Input Resistance                                        | DDQREF_R              | V <sub>DDQREF</sub> = 2.5 V                                                                                                                                          | 40       | 55   | 75      | kΩ   |

| Source Current Limit                                           | I <sub>LIMVTsrc</sub> | _                                                                                                                                                                    | 2.5      | 3.0  | -       | Α    |

| Sink Current Limit                                             | I <sub>LIMVTsnk</sub> | _                                                                                                                                                                    | 2.5      | 3.0  | _       | Α    |

| Soft-Start Source Current Limit                                | I <sub>LIMVTSS</sub>  | -                                                                                                                                                                    | -        | 1.0  | -       | Α    |

| Maximum Soft-Start Time                                        | t <sub>ssvttmax</sub> | -                                                                                                                                                                    | -        | 0.32 | -       | ms   |

| V <sub>TTREF</sub> OUTPUT                                      | 1                     |                                                                                                                                                                      |          | 1    | I       |      |

| V <sub>TTREF</sub> Source Current                              | I <sub>VTTR</sub>     | V <sub>DDQREF</sub> = 1.8 V or 2.5 V                                                                                                                                 | 15       | -    | -       | mA   |

| V <sub>TTREF</sub> Accuracy Referred to 1/2V <sub>DDQREF</sub> | d <sub>VTTR</sub>     | 1/2V <sub>DDQREF</sub> - V <sub>TTR</sub> ,<br>V <sub>DDQREF</sub> = 2.5 V,<br>I <sub>VTTR</sub> = 0 mA to 15 mA                                                     | -25      | -    | 25      | mV   |

|                                                                |                       | 1/2V <sub>DDQREF</sub> - V <sub>TTR</sub> ,<br>V <sub>DDQREF</sub> = 1.8 V,<br>I <sub>VTTR</sub> = 0 mA to 15 mA                                                     | -18      | -    | 18      | mV   |

<sup>5.</sup> Guaranteed by design, not tested in production.

**ELECTRICAL CHARACTERISTICS (continued)** ( $V_{IN}$  = 12 V,  $T_A$  = -40 to 85°C,  $V_{CCA}$  =  $V_{CCP}$  =  $V_{BOOST}$  -  $V_{SWDDQ}$  = 5.0 V, L = 1.8 μH,  $C_{OUT1}$  = 150 μF x 2,  $C_{OUT2}$  = 22 μF x 2, RL1 = 5.6 kΩ, R1 = 4.3 kΩ, R2 = 3.3 kΩ, RZ1 = 10 kΩ, RZ2 = 130 Ω, CP1 = 100 pF, CZ1 = 2.2 nF, CZ2 = 4.7 nF, for min/max values unless otherwise noted. Typical values are at  $T_A$  = 25°C.)

| Characteristic                            | Symbol                      | Test Conditions                                     | Min | Тур | Max | Unit |

|-------------------------------------------|-----------------------------|-----------------------------------------------------|-----|-----|-----|------|

| CONTROL SECTION                           |                             |                                                     |     |     |     |      |

| VDDQEN Pin Threshold High                 | V <sub>DDQEN_H</sub>        | -                                                   | 1.4 | -   | -   | V    |

| VDDQEN Pin Threshold Low                  | V <sub>DDQEN_L</sub>        | -                                                   | -   | -   | 0.5 | V    |

| VDDQEN Pin Input Current                  | I <sub>IN</sub> _<br>VDDQEN | V <sub>DDQEN</sub> = 5.0 V                          | -   | -   | 1.0 | μΑ   |

| VTTEN Pin Threshold High                  | V <sub>TTEN_H</sub>         | -                                                   | 1.4 | -   | -   | V    |

| VTTEN Pin Threshold Low                   | V <sub>TTEN_L</sub>         | -                                                   | -   | -   | 0.5 | V    |

| VTTEN Pin Input Current                   | I <sub>IN_VTTEN</sub>       | V <sub>DDQEN</sub> = V <sub>TTEN</sub> = 5.0 V      | _   | -   | 1.0 | μΑ   |

| FPWM Pin Threshold High                   | FPWM_H                      | -                                                   | 1.4 | -   | -   | V    |

| FPWM Pin Threshold Low                    | FPWM_L                      | -                                                   | -   | -   | 0.5 | V    |

| FPWM Pin Input Current                    | I <sub>IN_FPWM</sub>        | $V_{DDQEN} = V_{TTEN} = \overline{FPWM}$<br>= 5.0 V | -   | -   | 1.0 | μΑ   |

| PGOOD Pin ON Resistance                   | PGOOD_R                     | I_PGOOD = 5.0 mA                                    | -   | 70  | -   | Ω    |

| PGOOD Pin OFF Current                     | PGOOD_LK                    | =                                                   | -   | -   | 1.0 | μΑ   |

| PGOOD LOW-to-HIGH Hold Time, for S5 to S0 | t <sub>hold</sub>           | (Note 6)                                            | -   | -   | 200 | μs   |

<sup>6.</sup> Guaranteed by design, not tested in production.

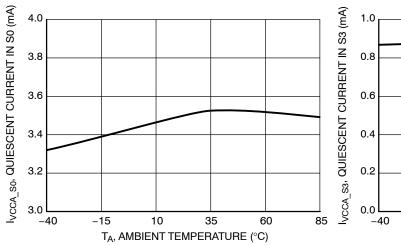

Figure 3. VCCA Quiescent Current in S0 vs. Ambient Temperature

Figure 4. VCCA Quiescent Current in S3 vs. Ambient Temperature

Figure 5. VCCA Shutdown Current vs. Ambient Temperature

Figure 6. Switching Frequency in S0 vs. Ambient Temperature

Figure 7. V<sub>DDQ</sub> Feedback Voltage vs. Ambient Temperature

Figure 8. Soft-Start Current vs. Ambient Temperature

#### TYPICAL OPERATING CHARACTERISTICS

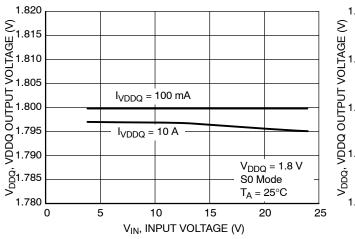

Figure 9. VDDQ Output Voltage vs. Input Voltage

Figure 10. VDDQ Output Voltage vs. VDDQ Output Current

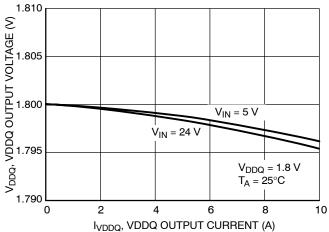

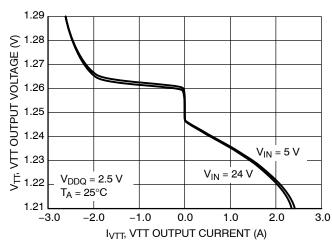

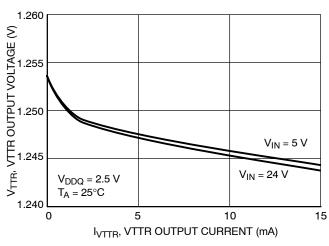

Figure 11. VTT Output Voltage (DDR) vs. VTT Output Current

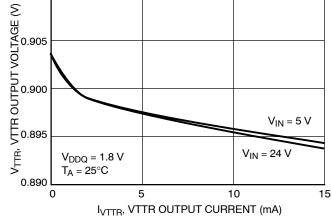

Figure 12. VTT Output Voltage (DDR2) vs. VTT Output Current

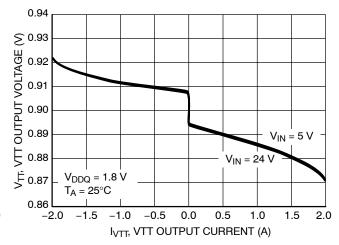

Figure 13. VTTR Output Voltage (DDR) vs. VTTR Output Current

Figure 14. VTTR Output Voltage (DDR2) vs. VTTR Output Current

0.910

#### TYPICAL OPERATING CHARACTERISTICS

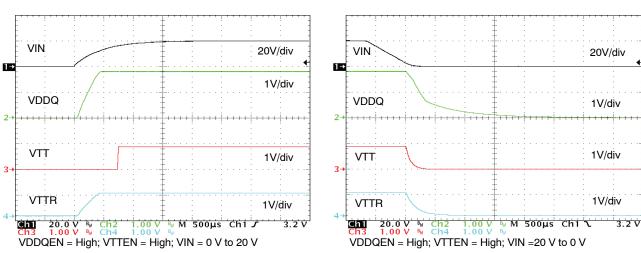

Figure 17. Powerup Waveforms

5V/div 5V/div **VDDQEN VDDQEN** 1⇒ 1→ **VDDQ** 1V/div 1V/div **VDDQ** VTTR VTTR 1V/div 1V/div **PGOOD** 5V/div **PGOOD** 5V/div 1.00 V W M 200µs Ch1 5.00 V W Chi 5.00 V W Ch2 Ch3 1.00 V W Ch4 ∿ M 200μs Ch1 -Chi 5.00 V № Ch2 Ch3 1.00 V № Ch4 VDDQEN = 0 V to 5 V VDDQEN = 5 V to 0 V

Figure 19. V<sub>DDQ</sub>, V<sub>TTR</sub> Startup Waveforms

Figure 20.  $V_{DDQ}$ ,  $V_{TTR}$  Shutdown Waveforms

Figure 18. Powerdown Waveforms

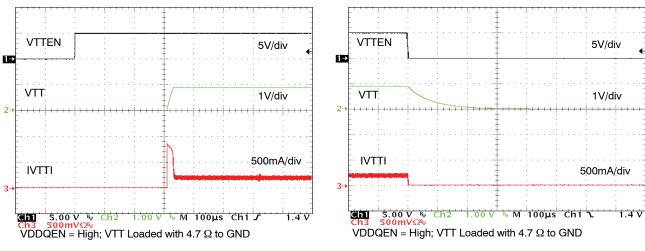

Figure 21. V<sub>TT</sub> Startup Waveforms

Figure 22. V<sub>TT</sub> Shutdown Waveforms

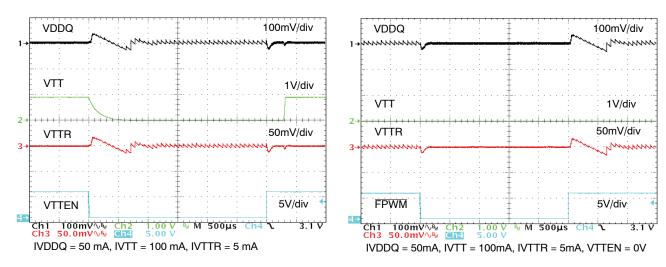

Figure 23. S0-S3-S0 Transition Waveforms

Figure 24. PS-FPWM-PS Transition Waveforms

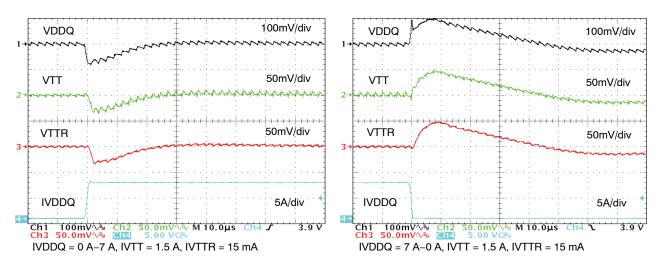

Figure 25. V<sub>DDQ</sub> Load Transient

Figure 26. V<sub>DDQ</sub> Load Transient

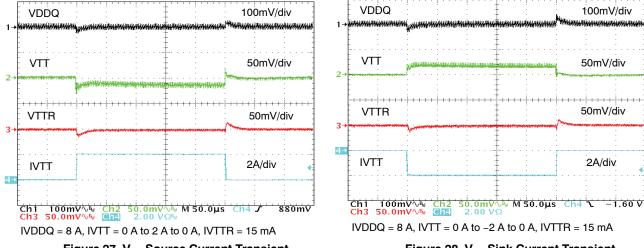

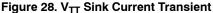

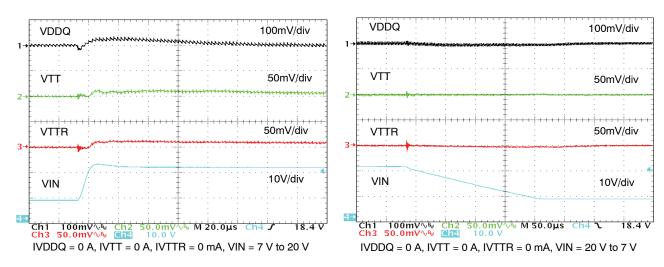

Figure 27. V<sub>TT</sub> Source Current Transient

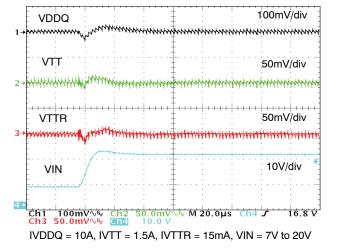

Figure 29. Line Transient 7 V to 20 V at No Load

Figure 30. Line Transient 20 V to 7 V at No Load

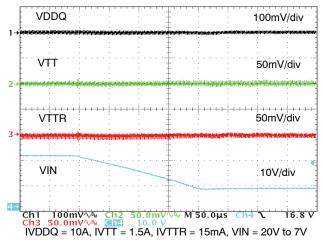

Figure 31. Line Transient 7 V to 20 V at Full Load

Figure 32. Line Transient 20 V to 7 V at Full Load

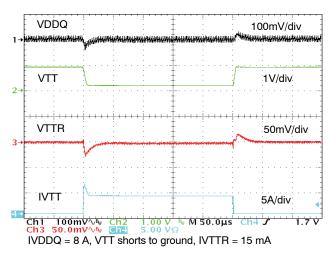

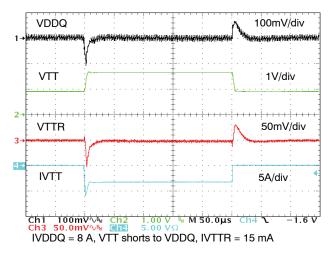

Figure 33. V<sub>TT</sub> Short Circuit to Ground and Recovery

Figure 34. V<sub>TT</sub> Short Circuit to VDDQ and Recovery

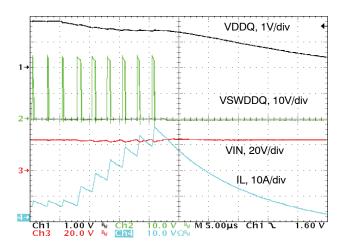

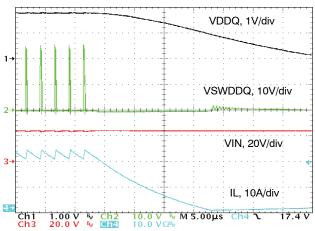

Figure 35. V<sub>DDQ</sub> OCP by Short Circuit to Ground

Figure 36. V<sub>DDQ</sub> OCP by Steady IVDDQ Increase

Figure 37. V<sub>DDQ</sub> OCP by Start into a Short Circuit

#### **DETAILED OPERATING DESCRIPTION**

#### General

The NCP5218 2-in-1 Notebook DDR Power Controller combines the efficiency of a PWM controller for the  $V_{DDQ}$  supply, with the simplicity of using a linear regulator for the  $V_{TT}$  termination voltage power supply. The  $V_{DDQ}$  output can be adjusted through the external potential divider, while the  $V_{TT}$  is internally set to track half  $V_{DDQ}$ .

The inclusion of  $V_{DDQ}$  power good voltage monitor, soft-start,  $V_{DDQ}$  overcurrent protection,  $V_{DDQ}$  overvoltage and undervoltage protections, supply undervoltage monitor, and thermal shutdown makes this device a total power solution for high current DDR memory system. The IC is packaged in DFN22.

### **Control Logic**

The internal control logic is powered by VCCA. The IC is enabled whenever  $V_{DDQEN}$  is high (exceed 1.4 V). An internal bandgap voltage,  $V_{REF}$  is then generated. Once  $V_{REF}$  reaches its regulation voltage, an internal signal  $V_{REFGD}$  will be asserted. This transition wakes up the supply undervoltage monitor blocks, which will assert VCCAGD if VCCA voltage is within certain preset levels.

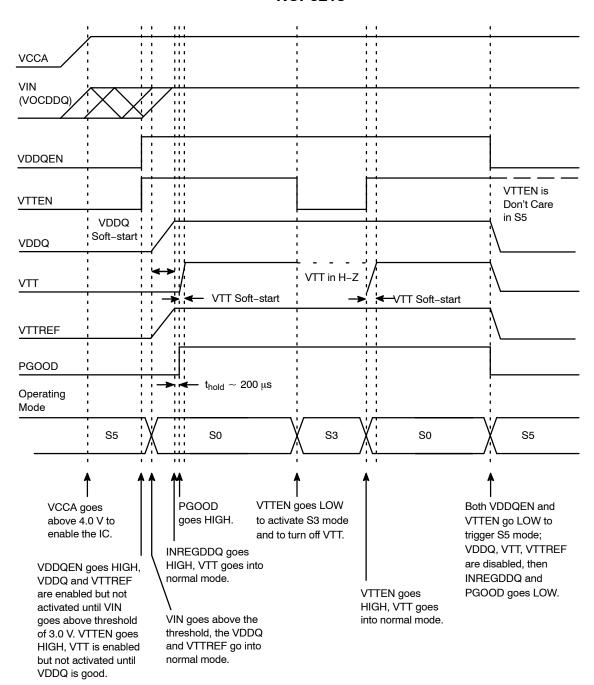

The control logic accepts external signals at VCCA, OCDDQ, VDDQEN, VTTEN, and  $\overline{FPWM}$  pins to control the operating state of the  $V_{DDQ}$  and  $V_{TT}$  regulators in accordance with Table 1. A timing diagram is shown in Figure 38.

#### V<sub>DDQ</sub> Switching Regulator in Normal Mode (S0)

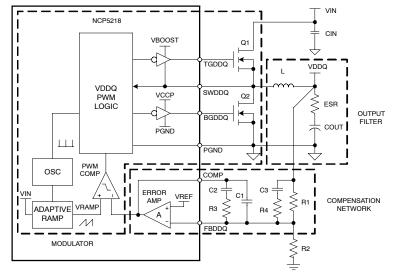

The  $V_{DDQ}$  regulator is a switching synchronous rectification buck controller directly driving two external N-Channel power FETs. An external resistor divider sets the nominal output voltage. The control architecture is voltage mode fixed frequency PWM with external compensation and with switching frequency fixed at  $400 \text{ kHz} \pm 15\%$ . As can be observed from Figure 1, the

V<sub>DDO</sub> output voltage is divided down and fed back to the inverting input of an internal error amplifier through FBDDQ pin to close the loop at  $V_{DDQ} = V_{FBDDQ} \times$ (1 + R1/R2). This amplifier compares the feedback voltage with an internal  $V_{REF}$  (= 0.800 V) to generate an error signal for the PWM comparator. This error signal is further compared with a fixed frequency RAMP waveform derived from the internal oscillator to generate a pulse-width-modulated signal. This PWM signal drives the external N-Channel Power FETs via the TGDDQ and BGDDQ pins. External inductor L and capacitor COUT1 filter the output waveform. The V<sub>DDO</sub> output voltage ramps up at a pre-defined soft-start rate when the IC enters state S0 from S5. When in normal mode, and regulation of V<sub>DDO</sub> is detected, signal IN<sub>REGDDO</sub> will go HIGH to notify the control logic block.

Input voltage feedforward is implemented to the RAMP signal generation to reject the effect of wide input voltage variation. With input voltage feedforward, the amplitude of the RAMP is proportional to the input voltage.

For enhanced efficiency, an active synchronous switch is used to eliminate the conduction loss contributed by the forward voltage of a diode or Schottky diode rectifier. Adaptive nonoverlap timing control of the complementary gate drive output signals is provided to reduce large shoot–through current that degrades efficiency.

#### Tolerance of V<sub>DDQ</sub>

The tolerance of  $V_{FBDDQ}$  and the ratio of external resistor divider R1/R2 both impact the precision of  $V_{DDQ}$ . With the control loop in regulation,  $V_{DDQ} = V_{FBDDQ} \times (1 + R1/R2)$ . With a worst case (for all valid operating conditions)  $V_{FBDDQ}$  tolerance of  $\pm 1.5\%$ , a worst case range of  $\pm 2.5\%$  for  $V_{DDQ} = 1.8$  V will be assured if the ratio R1/R2 is specified as  $1.2500 \pm 1\%$ .

| Table 4 Otata   | O          | 1         | A      | 0         | T-1-1- |

|-----------------|------------|-----------|--------|-----------|--------|

| Table 1. State. | Operation. | indut and | Outbut | Condition | rabie  |

|      |      | Input Conditions |        |       |      |         | Operating Conditions |        |                               | Output Conditions             |       |

|------|------|------------------|--------|-------|------|---------|----------------------|--------|-------------------------------|-------------------------------|-------|

| Mode | VCCA | VOCDDQ           | VDDQEN | VTTEN | FPWM | VDDQ    | VTTREF               | VTT    | TGDDQ                         | BGDDQ                         | PGOOD |

| S5   | Low  | Х                | Х      | Х     | Х    | H–Z     | H–Z                  | H–Z    | Low                           | Low                           | Low   |

| S5   | Х    | Low              | Х      | Х     | Х    | H–Z     | H–Z                  | H–Z    | Low                           | Low                           | Low   |

| S0   | High | High             | High   | High  | Х    | Normal  | Normal               | Normal | Normal                        | Normal                        | H–Z   |

| S3   | High | High             | High   | Low   | High | Standby | Normal               | H-Z    | Standby<br>(Power-<br>saving) | Standby<br>(Power-<br>saving) | H–Z   |

| S3   | High | High             | High   | Low   | Low  | Normal  | Normal               | H–Z    | Normal                        | Normal                        | H-Z   |

| S5   | Х    | Х                | Low    | Х     | Х    | H–Z     | H-Z                  | H-Z    | Low                           | Low                           | Low   |

#### V<sub>DDQ</sub> Regulator in Standby Mode (S3)

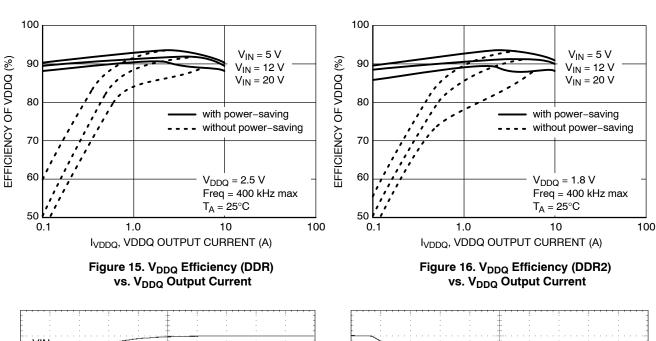

During state S3, a power–saving mode is activated when the FPWM pin is pulled to VCCA. In power–saving mode,

the switching frequency is reduced with the  $V_{DDQ}$  output current and the low-side FET is turned off after the detection of negative inductor current, so as to enhance the

efficiency of the  $V_{DDQ}$  regulator at light loads. The switching frequency can be reduced smoothly until it reaches the minimum frequency at about 15 kHz. Therefore, perceptible audible noise can be avoided at light load condition.

In power–saving mode, the low–side MOSFET is turned off after the detection of negative inductor current and the converter cannot sink current. The power–saving mode can be disabled by pulling the FPWM pin to ground. Then, the converter operates in forced–PWM mode with fixed switching frequency and ability to sink current.

# Fault Protection of $V_{DDQ}$ Regulator

During state S0 and S3, external resistor (RL1) between OCDDQ and  $V_{\rm IN}$  sets the overcurrent trip threshold for the high-side switch. An internal 31  $\mu$ A current sink (IOC) at OCDDQ pin establishes a voltage drop across this resistor and develops a voltage at the non-inverting input of the current limit comparator. The voltage at the non-inverting input is compared to the voltage at SWDDQ pin when the high-side gate drive is high after a fixed period of blanking time (150 ns) to avoid false current limit triggering. When the voltage at SWDDQ is lower than that at the non-inverting input for 4 consecutive internal clock cycles, an overcurrent condition occurs, during which, all outputs will be latched off to protect against a short-to-ground condition on SWDDQ or VDDQ. The IC will be reset once VCCA or VDDQEN is cycled.

#### Feedback Compensation of V<sub>DDQ</sub> Regulator

The compensation network is shown in Figures 2 and 39.

#### V<sub>TT</sub> Active Terminator in Normal Mode (S0)

The V<sub>TT</sub> active terminator is a two-quadrant linear regulator with two internal N-channel power FETs. It is capable of sinking and sourcing at least 1.5 A continuous current and up to 2.4 A transient peak current. It is activated in normal mode in state S0 when the VTTEN pin is HIGH and VDDQ is in regulation. Its input power path is from VDDQ with the internal FETs gate drive power derived from VCCA. The V<sub>TT</sub> internal reference voltage is derived from the DDQREF pin. The VTT output is set to VDDQ/2 when V<sub>TT</sub> output is connecting to the FBVTT pin directly. This regulator is stable with only a minimum 20 µF output capacitor. The V<sub>TT</sub> regulator will have an internal soft-start when it is transited from disable to enable. During the V<sub>TT</sub> soft–start, a current limit is used as a current source to charge up the V<sub>TT</sub> output capacitor. The current limit is initially 1.0 A during V<sub>TT</sub> soft-start. It is then increased to 2.5 A after 128 internal clock cycles which is typically 0.32 ms.

#### V<sub>TT</sub> Active Terminator in Standby Mode (S3)

V<sub>TT</sub> output is high-impedance in S3 mode.

#### Fault Protection of V<sub>TT</sub> Active Terminator

To provide protection for the internal FETs, bidirectional current limit is implemented, preset at the minimum of 2.5 A magnitude.

#### Thermal Consideration of V<sub>TT</sub> Active Terminator

The V<sub>TT</sub> terminator is designed to handle large transient output currents. If large currents are required for very long duration, then care should be taken to ensure the maximum junction temperature is not exceeded. The 5x6 DFN22 has a thermal resistance of 35°C/W (dependent on air flow, grade of copper, and number of vias). In order to take full advantage from this thermal capability of this package, the thermal pad underneath must be soldered directly onto a PCB metal substrate to allow good thermal contact. It is recommended that PCB with 2 oz. copper foil is used and there should have 6 to 8 vias with 0.6 mm hole size underneath the package's thermal pad connecting the top layer metal to the bottom layer metal and the internal layer metal substrates of the PCB.

#### **VTTREF Output**

The  $V_{TTREF}$  output tracks  $V_{DDQREF}/2$  at  $\pm 2\%$  accuracy. It has source current capability of up to 15 mA.  $V_{TTREF}$  should be bypassed to analog ground of the device by 1.0  $\mu F$  ceramic capacitor for stable operation. The  $V_{TTREF}$  is turned on as long as  $V_{DDQREF}$  is pulled high. In S0 mode,  $V_{TTREF}$  soft–starts with  $V_{DDQ}$  and tracks  $V_{DDQREF}/2$ . In S3 mode,  $V_{TTREF}$  is kept on with  $V_{DDQ}$ .  $V_{TTREF}$  is turned off only in S4/S5 like  $V_{DDQ}$  output.

#### **Output Voltages Sensing**

The  $V_{DDQ}$  output voltage is sensed across the FBDDQ and AGND pins. FBDDQ should be connected through a feedback resistor divider to the VDDQ point of regulation which is usually the local  $V_{DDQ}$  bypass capacitor for load. The AGND should be connected directly through a sense trace to the remote ground sense point which is usually the ground of local  $V_{DDO}$  bypass capacitor for load.

The  $V_{TT}$  output voltage is sensed between the FBVTT and VTTGND pins. The FBVTT should be connected to the  $V_{TT}$  regulation point, which is usually the  $V_{TT}$  local bypass capacitor, via a direct sense trace. The VTTGND should be connected via a direct sense trace to the ground of the  $V_{TT}$  local bypass capacitor for load.

#### **Supply Voltage Undervoltage Monitor**

The IC continuously monitors VCCA and  $V_{\rm IN}$  through VCCA pin and OCDDQ pin respectively. VCCAGD is set HIGH if VCCA is higher than its preset threshold (derived from VREF with hysteresis). The IC will enter S5 state if VCCA fails while in S0 and both VDDQEN and VTTEN remain HIGH.

#### **Thermal Shutdown**

When the chip junction temperature exceeds 150°C, the entire IC is shutdown. The IC resumes normal operation only after the junction temperature dropping below 125°C.

#### **Power Good**

The PGOOD is an open-drain output of a window comparator which continuously monitors the VDDQ output voltage. The PGOOD is pulled low when the VDDQ rises 12% above or drops 12% below the nominal regulation point. The PGOOD becomes high impedance when the VDDQ is within  $\pm 12\%$  of the preset nominal regulation voltage. A 100 k $\Omega$  resistor is recommended to connect between PGOOD and VCCA as pull-up resistor for logic level output.

#### **Overvoltage Protection**

When the  $V_{DDQ}$  output is above 106% but below 130% of the nominal regulation output voltage, the controller turns off the high-side MOSFET and turns on the low-side

MOSFET to discharge the excessive output voltage. When the  $V_{DDQ}$  output voltage goes back down to the nominal regulation voltage, normal switching cycles are resumed. When the  $V_{DDQ}$  output exceeds 130% (typ) of the nominal regulation voltage for 4 consecutive internal clock cycles, the controller sets overvoltage fault, the device is latched off by turning off both the high-side and low-side MOSFETs. The overvoltage fault latch can be reset and the controller can be restarted by toggling VDDQEN, VCCA, or VIN.

#### **Undervoltage Protection**

In S3 power–saving mode with reduced switching at lighter loads, when the  $V_{\rm DDQ}$  falls below 94% of the nominal regulation voltage, the reduced switching frequency is raised up back to the maximum switching frequency. When  $V_{\rm DDQ}$  voltage is back to nominal regulation voltage, the normal S3 power–saving operation is resumed. In both S0 and S3 modes, when the  $V_{\rm DDQ}$  falls below 65% (typ) of the nominal regulation voltage for 4 consecutive internal clock cycles, the undervoltage fault is set, the device is latched off by turning off both the high–side and low–side MOSFETs. The output is discharged by the load current. The load current and output capacitance determine the discharge rate. Cycling VDDQEN, VCCA, or  $V_{\rm IN}$  can reset the undervoltage fault latch and restart the controller.

Figure 38. Powerup and Powerdown Timing Diagram

#### APPLICATION INFORMATION

# Input Capacitor Selection for V<sub>DDQ</sub> Buck Regulator

The input capacitor is important for proper regulation operation of the buck regulator. It minimizes the input voltage ripple and current ripple from the power source by providing a local loop for switching current. The input capacitor should be placed close to the drain of the high–side MOSFET and source of the low–side MOSFET with short, wide traces for connection. The input capacitor must have large enough rms ripple current rating to withstand the large current pulses present at the input of the bulk regulator due to the switching current. The required input capacitor rms ripple current rating can be estimated by the following with minimum  $V_{\rm IN}$ :

$$I_{CIN(RMS)} \ge I_{OUT} \sqrt{\frac{V_{OUT}}{V_{IN}} - \left(\frac{V_{OUT}}{V_{IN}}\right)^2}$$

(eq. 1)

Besides, the voltage rating of the input capacitor should be at least 1.25 times of the maximum input voltage. Capacitance of around 20 µF to 50 µF should be sufficient for most DDR applications. Ceramic capacitors are the most suitable choice of input capacitor for notebook applications due to their low ESR, high ripple current, and high voltage rating. POSCAP or OS-CON capacitors can also be used since they have good ESR and ripple current rating, but they are larger in size and more expensive. Aluminum electrolytic capacitors are also a choice for their high voltage rating and low cost, but several aluminum capacitors in parallel should be used for the required ripple current. If ceramic capacitors are used, X5R and X7R types are preferred rather than the Y5V type since the X5R and X7R types are ceramic capacitors and have smaller tolerance and temperature coefficient.

# Output Capacitor Selection for V<sub>DDQ</sub> Buck Regulator

The output filter capacitor plays an important role in steady state output ripple voltage, load transient requirement, and loop compensation stability. The ESR and the capacitance of the output capacitor are the most important parameters needed to be considered. In general, the output capacitor must have small enough ESR for output ripple voltage and load transient requirement. Besides, the capacitance of the output capacitor should be large enough to meet the overshoot and undershoot during load transient. Since steady state output ripple voltage, transient load undershoot and overshoot are the largest at maximum  $V_{\rm IN}$ , the ESR and capacitance of output capacitor should be estimated at the maximum  $V_{\rm IN}$  condition.

For steady output ripple voltage, both ESR and capacitance of the output capacitor are the contributing factors, however, the capacitor ESR is the dominant factor. The output ripple voltage is calculated as follows:

$$V_{ripple} = I_{L(ripple)} \times ESR + \frac{I_{L(ripple)} \times t_{on}}{C_{OUT}}$$

(eq. 2)

$$V_{ripple} = I_{L(ripple)} \times ESR$$

, for small  $t_{On}$  and large  $C_{OUT}$  (eq. 3)

where  $I_{L(ripple)}$  is the inductor ripple current,  $t_{on}$  is on–time, and  $C_{OUT}$  is the output capacitance.

The inductor ripple current can be calculated by the equation:

$$I_{L(ripple)} = \frac{(VIN-VOUT) \times VOUT}{L \times fSW \times VIN}$$

(eq. 4)

where L is the inductance and  $f_{SW}$  is the switching frequency. The output ripple voltage can be reduced by either using the inductor with larger inductance or the output capacitor with smaller ESR. Thus, the ESR needed to meet the ripple voltage requirement can be obtained by:

$$ESR \le \frac{V_{ripple} \times L \times f_{SW} \times V_{IN}}{(V_{IN} - V_{OUT}) \times V_{OUT}}$$

(eq. 5)

The inductor ripple current is typically 30% of the maximum load current and the ripple voltage is typically 2% of the output voltage. Thus, the above inequality can be simplified to:

$$ESR \le \frac{0.02 \times V_{OUT}}{0.3 \times I_{LOAD(max)}}$$

(eq. 6)

For the load transient, the output capacitor contributes to both the load-rise and the load-release responses. The voltage undershoot during step-up load can be calculated by the equation:

$$V_{undershoot} = \Delta I_{LOAD} \times ESR + \frac{\Delta I_{LOAD}}{C_{OUT}} \times \left(\frac{1 - \frac{V_{OUT}}{V_{IN}}}{f_{SW}}\right)$$

(eq. 7)

where  $\Delta I_{LOAD}$  is the change in output current. If the second term is ignored, then it becomes the following inequality:

$$ESR \le \frac{Vundershoot}{\Delta ILOAD}$$

(eq. 8)

The maximum ESR requires to meet voltage undershoot requirement at step-up load transient can be estimated from the above inequality.

Then, the required output capacitor capacitance can be obtained by the following:

$$C_{OUT} \ge \frac{\Delta I_{LOAD}}{V_{undershoot} - \Delta I_{LOAD} \times ESR} \times \left(\frac{1 - \frac{V_{OUT}}{V_{IN}}}{f_{SW}}\right)$$

(eq. 9)

The output voltage overshoot during load-release is because the excessive stored energy in the inductor is absorbed by the output capacitor. The overshoot voltage can be calculated by the following equation:

$$V_{overshoot} = \sqrt{\frac{LI^2STEP(peak) + COUTV^2OUT}{COUT}} - VOUT$$

(eq. 10)

Then the required output capacitor capacitance can be estimated by:

$$\begin{split} C_{OUT} & \geq \frac{L \times I^2 \text{STEP(peak)}}{(\text{Vovershoot} + \text{VOUT})^2 - \text{V}^2 \text{OUT}} \quad \text{(eq. 11)} \\ I_{STEP(peak)} & = \Delta I_{LOAD} + \frac{(\text{VIN-VOUT}) \times \text{VOUT}}{2L \times \text{fSW} \times \text{VIN}} \\ & \text{(eq. 12)} \end{split}$$

where  $I_{STEP(peak)}$  is the load current step plus half of the ripple current at the load release and  $\Delta I_{LOAD}$  is the change in the output load current.

Besides, the ESR and the capacitance of the output filter capacitor also contribute to double pole and ESR zero frequencies of the output filter, and the poles and zeros frequencies of the compensation network for close loop stability. The compensation network will be discussed in more detail in the Loop Compensation section.

Other parameters about output filter capacitor that needed to be considered are the voltage rating and ripple current rating. The voltage rating should be at least 1.25 times the output voltage and the rms ripple current rating should be greater than the inductor ripple current. Thus, the voltage rating and ripple current rating can be obtained by:

$$V_{rating} \ge 1.25 \times V_{OUT}$$

(eq. 13)

$$I_{COUT(RMS)} \ge I_{L(ripple)} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{L \times f_{SW} \times V_{IN}}$$

(eq. 14)

SP-Cap, POSCAP and OS-CON capacitors are suitable for the output capacitor since their ESR is low enough to meet the ripple voltage and load transient requirements. Usually, two or more capacitors of the same type, capacitance and ESR can be used in parallel to achieve the required ESR and capacitance without change the ESR zero position for maintaining the same loop stability. Other than the performance point of view, the physical size and cost are also the concerned factors for output capacitor selection.

### **Inductor Selection**

The inductor should be chosen according to the inductor ripple current, inductance, maximum current rating, transient load release, and DCR.

In general, the inductor ripple current is 20% to 40% of the maximum load current. A ripple current of 30% of the maximum load current can be used as a typical value. The required inductance can be estimated by:

$$L \geq \frac{(VIN-VOUT) \times VOUT}{0.3 \times ILOAD(max) \times VIN \times fSW} \hspace{0.5cm} (eq. 15)$$

where I<sub>LOAD(max)</sub> is the maximum load current.

The DC current rating of the inductor should be about 1.2 times of the peak inductor current at maximum output load current. Therefore, the maximum DC current rating of the inductor can be obtained by:

$$I_{L(rating)} = 1.2 \times I_{L(peak)}$$

(eq. 16)

where  $I_{L(peak)}$  is the peak inductor current at maximum load current which is determined by:

$$\begin{split} I_{L(peak)} &= I_{LOAD(max)} + \frac{I_{L(ripple)}}{2} \\ &= I_{LOAD(max)} + \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times L \times f_{SW} \times V_{IN}} \end{split}$$

Since the excessive energy stored in the inductor contributed to the output voltage overshoot during load release, the following inequality can be used to ensure that the selected inductance value can meet the voltage overshoot requirement at load release:

$$L \leq \frac{\text{COUT} \times \left( (\text{Vovershoot} + \text{VOUT})^2 - \text{V}^2 \text{OUT} \right)}{\text{I}^2 \text{STEP(peak)}}$$

(eq. 18)

In addition, the inductor also needs to have low enough DCR to obtain good conversion efficiency. In general, inductors with about 2.0 m $\Omega$  to 3.0 m $\Omega$  per  $\mu H$  of inductance can be used. Besides, larger inductance value can be selected to achieve higher efficiency as long as it still meets the targeted voltage overshoot at load release and inductor DC current rating. Moreover, it should be noted that using too small inductance value will cause very large inductor ripple current in CCM in S0 mode and extremely large peak inductor current in DCM in power-saving mode during S3 mode. For both cases, output capacitors with smaller ESR and larger capacitance are required to keep the output ripple voltage small. It should also be noted that the peak inductor current under DCM light-load condition in power-saving mode in S3 mode will be larger than the peak inductor current under heavy-load condition in S0 mode when very small inductance value is used. Besides, using smaller inductance will achieve lower efficiency require larger minimum load to maintain nominal voltage regulation in power-saving mode in S3 state. Therefore, it is recommended that the inductance value should be at least 0.56 µH or above to obtain optimum performance.

#### **MOSFET Selection**

External N-channel MOSFETs are used as the switching elements of the buck controller. Both high-side and low-side MOSFETs must be logic-level MOSFETs which can be fully turned on at 5.0 V gate-drive voltage. On-resistance ( $R_{DS(on)}$ ), maximum drain-to-source voltage ( $V_{DSS}$ ), maximum drain current rating, and gate charges ( $Q_G$ ,  $Q_{GD}$ ,  $Q_{GS}$ ) are the key parameters to be considered when choosing the MOSFETs.

For on–resistance, it should be the lower; the better is the performance in terms of efficiency and power dissipation. Check the MOSFET's rated  $R_{DS(on)}$  at  $V_{GS}$  = 4.5 Vwhen selecting the MOSFETs. The low–side MOSFET should have lower  $R_{DS(on)}$  than the high–side MOSFET since the

turn—on time of the low—side MOSFET is much longer than the high—side MOSFET in high  $V_{IN}$  and low  $V_{OUT}$  buck converter. Generally, high—side MOSFET with  $R_{DS(on)}$  about 7.0 m $\Omega$  and low—side MOSFET with  $R_{DS(on)}$  about 5.0 m $\Omega$  can achieve good efficiency.

The maximum drain current rating of the high-side MOSFET and low-side MOSFET must be higher than the peak inductor current at maximum load current. The low-side MOSFET should have larger maximum drain current rating than the high-side MOSFET since the low-side MOSFET have longer turn-on time.

The maximum drain-to-source voltage rating of the MOSFETs used in buck converter should be at least 1.2 times of the maximum input voltage. Generally,  $V_{DSS}$  of 30 V should be sufficient for both high-side MOSFET and low-side MOSFET of the buck converter for notebook application.

As a general rule of thumb, the gate charges are the smaller; the better is the MOSFET while  $R_{DS(on)}$  is still low enough. MOSFETs are susceptible to false turn-on under high dV/dt and high VDS conditions. Under high dV/dt and high VDS condition, current will flow through the  $C_{GD}$  of the capacitor divider formed by  $C_{GD}$  and  $C_{GS}$ , cause the  $C_{GS}$  to charge up and the  $V_{GS}$  to rise. If the  $V_{GS}$  rises above the threshold voltage, the MOSFET will turn on. Therefore, it should be checked that the low-side MOSFET have low  $Q_{GD}$  to  $Q_{GS}$  ratio. This indicates that the low-side MOSFET have better immunity to short moment false turn-on due to high dV/dt during the turn-on of the high-side MOSFET. Such short moment false turn-on will cause minor shoot-through current which will degrade efficiency, especially at high input voltage condition.

#### **Overcurrent Protection of VDDQ Buck Regulator**

The OCP circuit is configured to set the current limit for the current flowing through the high-side FET and inductor during S0 and S3. The overcurrent tripping level is programmed by an external resistor RL1 connected between the OCDDQ pin and drain of the high-side FET. An internal 31 µA current sink (IOC) at pin OCDDQ establishes a voltage drop across the resistor RL1 at a magnitude of RL1xIOC and develops a voltage at the non-inverting input of the current limit comparator. Another voltage drop is established across the high-side MOSFET R<sub>DS(on)</sub> at a magnitude of I<sub>I</sub>xR<sub>DS(on)</sub> and a voltage is developed at SWDDQ when the high-side MOSFET is turned on and the inductor current flows through the R<sub>DS(on)</sub> of the MOSFET. The voltage at the non-inverting input of the current limit comparator is then compared to the voltage at SWDDQ pin when the high-side gate drive is high after a fixed period of blanking time (150 ns) to avoid false current limit triggering. When the voltage at SWDDQ is lower than the voltage at the non-inverting input of the current limit comparator for four consecutive internal clock cycles, an overcurrent condition occurs, during which, all outputs will be latched off to protect against a short-to-ground condition on SWDDQ or  $V_{\mathrm{DDQ}}$ . i.e., the voltage drop across the  $R_{\mathrm{DS(on)}}$  of high-side FET developed by the drain current is larger than the voltage drop across RL1, the OCP is triggered and the device will be latched off.

The overcurrent protection will trip when a peak inductor current hit the I<sub>LIMIT</sub> determined by the equation:

$$I_{LIMIT} = \frac{RL1 \times IOC}{RDS(on)}$$

(eq. 19)

It should be noted that the OCDDQ pin must be pulled high to VIN through a resistor RL1 and this pin cannot be left floating for normal operation. The voltage drop across RL1 must be less than 1.0 V to allow enough headroom for the voltage detection at the OCDDQ pin under low VIN condition. In addition, since the MOSFET  $R_{DS(on)}$  varies with temperature as current flows through the MOSFET increases, the OCP trip point also varies with the MOSFET  $R_{DS(on)}$  temperature variation.

Since the IOC and  $R_{DS(on)}$  have device variations and MOSFET  $R_{DS(on)}$  increase with temperature, to avoid false triggering the overcurrent protection in normal operating output load range, calculate the RL1 value from the previous equation with the following conditions such that minimum value of inductor current limit is set:

- The minimum IOC value from the specification table.

- 2. The maximum R<sub>DS(on)</sub> of the MOSFET used at the highest junction temperature.

- 3. Determine  $I_{LIMIT}$  for  $I_{LIMIT} > I_{LOAD(max)} + I_{L(ripple)/2}$ , where  $I_{LOAD(max)} = I_{VDDQ(max)} + I_{VTT(max)}$  if VTT is powered by VDDQ.

Besides, a decoupling capacitor C<sub>DCPL</sub> should be added closed to the lead of the current limit setting resistor RL1 which connected to the drain of the high-side MOSFET.

#### **Loop Compensation**

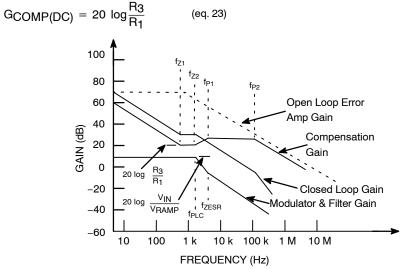

Once the output LC filter components have been determined, the compensation network components can be selected. Since NCP5218 is a voltage mode PWM converter with output LC filter, Type III compensation network is required to obtain the desired close loop bandwidth and phase boost with unconditional stability. The NCP5218 PWM modulator, output LC filter and Type III compensation network are shown in Figure 39. The output LC filter has a double pole and a single zero. The double pole is due to the inductance of the inductor and capacitance of the output capacitor, while the single zero is due to the ESR and capacitance of the output capacitor. The Type III compensation has two RC pole-zero pairs. The two zeros are used to compensate the LC double pole and provide 180° phase boost. The two poles are used to compensate the ESR zero and provide controlled gain roll-off. For an ideally compensated system, the Bode plot should have the close-loop gain roll-off with a slope of -20 dB/decade crossing the 0 dB with the required bandwidth and the phase margin larger than 45° for all frequencies below the 0 dB frequency. The closed loop gain is obtained by adding the modulator and filter gain (in dB) to the compensation gain (in dB). The bandwidth is the frequency at which the gain is 0 dB and the phase margin is the difference between the close loop phase and 180°. The goal of compensation is to achieve a stable close loop system with the highest possible bandwidth, the gain

having -20 dB/decade slope at 0 dB gain crossing, and sufficient phase margin for stability. The bandwidth of close loop gain should be less than 50% of the switching frequency and the compensation gain should be bounded by the error amplifier open loop gain.

Figure 39. Voltage Mode Buck Converter with Modulator, LC filter and Type III Compensation

Modulator DC Gain can be calculated by:

$$G_{MOD(DC)} = 20 log \frac{V_{IN}}{V_{RAMP}}$$

(eq. 20)

LC filter double pole and ESR zero break frequencies are defined by:

$$f_{PLC} = \frac{1}{2\pi \times \sqrt{L \times C_{OUT}}}$$

(eq. 21)

$$f_{ZESR} = \frac{1}{2\pi \times ESR \times COUT}$$

(eq. 22)

Compensation network DC Gain can be calculated by the equation:

Type III compensation poles and zeros break frequencies are defined by the below equations:

$$fZ1 = \frac{1}{2\pi \times R_3 \times C_2}$$

(eq. 24)

$$fp_1 = \frac{1}{2\pi \times R_3 \times \left(\frac{C_1 \times C_2}{C_1 + C_2}\right)}$$

(eq. 25)

$$f_{Z2} = \frac{1}{2\pi \times (R_1 + R_4) \times C_3}$$

(eq. 26)

$$\mathsf{fP2} = \frac{1}{2\pi \times \mathsf{R_4} \times \mathsf{C_3}} \tag{eq. 27}$$

Figure 40. Asymptotic Bode Plot of the Converter Gain

Close loop system bandwidth can be calculated by:

$$BW = \frac{R_3}{R_1} \times \frac{V_{IN}}{V_{RAMP}} \times \frac{1}{2\pi \times \sqrt{L \times C_{OLIT}}} \text{ (eq. 28)}$$

Since the ramp amplitude of the PWM modulator has a voltage feedforward function, the ramp amplitude is a function of  $V_{\text{IN}}$  which can be determined by:

$$V_{RAMP} = 1.25 V + 0.045 \times (V_{IN}-5.0 V)$$

(eq. 29)

Below are some guidelines for setting the compensation components:

- 1. Set a value for  $R_1$  between 2.0  $k\Omega$  and 5.0  $k\Omega$ .

- 2. Set a target for the close loop bandwidth which should be less than 50% and is typically 1/8 to 1/4 of the switching frequency.

- 3. Pick compensation DC gain (R<sub>3</sub>/R<sub>1</sub>) for desired close loop bandwidth.

- 4. Place 1st zero at half filter double pole.

- 5. Place 1st pole at ESR zero.

- 6. Place 2nd zero at filter double pole.

- 7. Place 2nd pole at half the switching frequency.

By using the above equations and guidelines, the compensation components values can be determined by the equations below:

$$R_3 = \frac{2\pi \times BW \times V_{RAMP} \times R_1 \times \sqrt{L \times C_{OUT}}}{V_{IN}} \quad (eq. 30)$$

$$C_2 = \frac{2 \times \sqrt{L \times C_{OUT}}}{R_3}$$

(eq. 31)

$$C_1 = \frac{C_2}{\left(\frac{R_3 \times C_2}{ESR \times COUT}\right) - 1}$$

(eq. 32)

$$R_4 = \frac{R_1}{\pi \times f_{SW} \times \sqrt{L \times C_{OUT}} - 1}$$

(eq. 33)

$$C_3 = \frac{1}{\pi \times R_4 \times f_{SW}}$$

(eq. 34)

The modulator and filter gain, compensation gain, and close loop gain asymptotic Bode plot can be drawn by the calculated results to check the compensation gain and close loop gain obtained. An example of asymptotic Bode plot is shown in Figure 40.

The phase of the output filter can be calculated by:

$$Phase(Filter) = -tan^{-1}(2\pi f \times ESR \times C_{OUT}) - tan^{-1}\left(\frac{2\pi f \times ESR + DCR \times C_{OUT}}{(2\pi f)^2 \times L \times C_{OUT} - 1}\right)$$

(eq. 35)

where the DCR of the inductor can be neglected if the DCR is small.

The phase of the Type III compensation network can be calculated by:

Phase(TypeIII) =

$$-90^{\circ}$$

+  $\tan^{-1}(2\pi f \times R_3 \times C_2)$  -  $\tan^{-1}(2\pi f \times R_3 \times \frac{C_1 \times C_2}{C_1 + C_2})$  +  $\tan^{-1}(2\pi f \times (R_1 + R_4) \times C_3)$  -  $\tan^{-1}(2\pi f \times R_4 \times C_3)$  (eq. 36)

The close loop phase can be calculated by summing the filter phase and compensation phase:

Then the close loop phase margin can be estimated by:

$$Phase(Margin) = Phase(CloseLoop) - (-180^{\circ})$$

(eq. 38)

It should be checked that closed loop gain has a 0 dB gain crossing with -20 dB/decade slope and a phase margin of 45° or greater. The compensation components values may require some adjustment to meet these requirements. Besides, the compensation gain should be checked with the error amplifier open loop gain to make sure that it is bounded by the error amplifier open loop gain.

The poles and zeros locations and hence the compensation network components values may need to be further fine tuned after actual system testing and analysis.

#### **Feedback Resistor Divider**

The output voltage of the buck regulator can be adjusted by the feedback resistor divider formed by  $R_1$  and  $R_2$ . Once the value of  $R_1$  is selected when determining the compensation components, the value of  $R_2$  can be obtained by:

$$R_2 = \frac{0.8 \times R_1}{V_{OUT} - 0.8}$$

(eq. 39)

It is recommended to adjust the value of  $R_2$  to fine—tune the output voltage when it is necessary. The value of  $R_1$  should not be changed since the compensation DC gain and the  $2^{\rm nd}$  zero break frequency of the compensation gain are contributed by  $R_1$ . If the value of  $R_1$  is changed, the compensation, the close loop bandwidth and phase margin, and the system stability will be affected. Besides, it is recommended to use resistors with at least 1% tolerance for  $R_1$  and  $R_2$ .

# Soft-Start of Buck Regulator

A  $V_{DDQ}$  soft-start feature is incorporated in the device to prevent surge current from power supply and output voltage overshoot during power up. When VDDQEN, VCCA, and VOCDDQ rise above their respective upper threshold voltages, the external soft-start capacitor  $C_{SS}$  will be charged up by a constant current source,  $I_{SS}$ . When the soft-start voltage (Vcss) rises above the SS\_EN voltage ( $\sim 50$  mV), the BGDDQ and TGDDQ will start switching and  $V_{DDQ}$  output will ramp up with VFBDDQ following the soft-start voltage. When the soft-start voltage reaches the SS\_OK voltage ( $\sim V_{REF} + 50$  mV), the soft-start of

$V_{DDQ}$  is finished. The  $C_{ss}$  will continue to charge up until it reaches about 2.5 V to 3.0 V.

The soft-start time  $t_{ss}$  can be programmed by the soft-start capacitor according to the following equation:

$$t_{SS} \approx \frac{0.8 \times C_{SS}}{I_{SS}} \tag{eq. 40}$$

Ceramic capacitors with low tolerance and low temperature coefficient, such as B, X5R, X7R ceramic capacitors are recommended to be used as the  $C_{SS}$ . Ceramic capacitors with Y5V temperature characteristic are not recommended.

#### **Soft-Start of VTT Active Terminator**

The VTT source current limit is used as a constant current source to charge up the VTT output capacitor during VTT soft-start. Besides, the VTT source current limit is reduced to about 1.0 A for 128 internal clock cycles to minimize the inrush current during VTT soft-start. Therefore, the VTT soft-start time t<sub>SSVTT</sub> can be estimated by the equation:

$$t_{SSVTT} \approx \frac{C_{OUTVTT} \times VTT}{I_{LIMVTSS}}$$

(eq. 41)

where  $C_{OUTVTT}$  is the capacitance of VTT output capacitor and  $I_{LIMVTSS}$  is the VTT soft–start source current limit.

#### **Boost Supply Diode and Capacitor**

An external diode and capacitor are used to generate the boost voltage for the supply of the high–side gate driver of the bulk regulator. Schottky diode with low forward voltage should be used to ensure higher floating gate drive voltage can be applied across the gate and the source of the high–side MOSFET. A Schottky diode with 30 V reverse voltage and 0.5 A DC current ratings can be used as the boost supply diode for most applications. A 0.1  $\mu F$  to 0.22  $\mu F$  ceramic capacitor should be sufficient as the boost capacitor.

#### VTTI Input Power Supply for VTT and VTTR

Both VTT and VTTR are supplied by VTTI for sourcing current. VTTI is normally connected to the VDDQ output for optimum performance. If VTTI is connected to VDDQ, no bypass capacitor is required to add to VTTI since the bulk capacitor at VDDQ output is sufficiently large. Besides, the maximum load current of VDDQ is the sum of  $I_{\mathrm{VDDQ(max)}}$  and  $I_{\mathrm{VTT(max)}}$  when making electrical design and components selection of the VDDQ buck regulator. VTTI can also be connected to an external voltage source. However, extra power dissipation will be generated from the internal VTT high-side MOSFET and more heatsinking is required if the external voltage is higher than VDDQ. Whereas, the headroom will be limit by the R<sub>DS(on)</sub> of the VTT linear regulator high-side MOSFET, and the maximum VTT output current with VTT within regulation window will also be reduced if the external voltage is lower than VDDQ. Besides, the VTTI pin input must be bypassed

to VTTGND with at least a 10  $\mu$ F capacitor if external voltage source is used.

### **Design Example**

A design example of a  $V_{DDQ}$  bulk converter with the following design parameters is shown below:

DDR2 V<sub>DDQ</sub> bulk converter design parameters:

- 1. Input voltage range: 7.0 V to 20 V.

- 2. Nominal V<sub>OUT</sub>: 1.8 V.

- 3. Static tolerance: 2% ( $\pm 36$  mV).

- 4. Transient tolerance:  $\pm 100$  mV.

- 5. Maximum output current: 10 A (I<sub>VDDQ(max)</sub> = 8.0 A, I<sub>VTT(max)</sub> = 2.0 A).

- 6. Load transient step: 1.0 A to 8.0 A.

- 7. Switching frequency: 400 kHz.

- 8. Bandwidth: 100 kHz.

- 9. Soft-start time: 400 μs.

- a. Calculate input capacitor rms ripple current rating and voltage rating:

$$I_{CIN(RMS)} \ge 10 \text{ A} \times \sqrt{\frac{1.836 \text{ V}}{8.0 \text{ V}} - \left(\frac{1.836 \text{ V}}{8.0 \text{ V}}\right)^2} = 4.2 \text{ A}$$

(eq. 42)

$$VCIN(rating) \ge 20 \times 1.25 V = 25 V$$

(eq. 43)

Therefore, two 10  $\mu F$  25 V ceramic capacitors with 1210 size in parallel are used.

b. Calculate inductance, rated current and DCR of inductor:

First, suppose ripple current is 0.3 times the maximum output current, such that:

$$L \geq \frac{(20 \text{ V} - 1.836 \text{ V}) \times 1.836 \text{ V}}{0.3 \times 10 \text{ A} \times 20 \text{ V} \times 400 \text{ kHz}} = 1.39 \ \mu\text{H} \quad \text{(eq. 44)}$$

Second, the overshoot requirement at load release is then considered and supposes two 220  $\mu F$  capacitors in parallel are used as an initially guess, such that: