Maxim > Design Support > Technical Documents > Application Notes > Wireless and RF > APP 5498

Keywords: PLL, loop filter, VCO, frac mode, integer mode, synthesizer, ADF4350

**APPLICATION NOTE 5498**

# Comparing the Registers and Loop Filter of the MAX2870 and ADF4350 Synthesizers

By: Jun Liu Oct 10, 2012

Abstract: This application note compares the MAX2870 ultra-wideband synthesizer/voltage controller oscillator (VCO) to the Analog Devices ADF4350 synthesizer. Registers and loop filter design are discussed in detail.

The MAX2870 ultra-wideband phase-locked loop (PLL) and voltage control oscillator (VCO) can operate in both integer-N and fractional-N modes, similar to the Analog Devices ADF4350 wideband synthesizer. This application note compares the MAX2870 and ADF4350 registers and loop filter design in detail. Users who already familiar with ADF4350 can use this application note as a quick design reference.

# Wireless Technology Overview

Click here for an overview of the wireless components used in a typical radio transceiver.

#### Contents

Register Table Comparison

Register 0

Register 1

Register 2

Register 3

Register 4

Register 5

New Loop Filter

Notes

## Register Table Comparison

| Bit      | MAX2870                         |                                 | ADF435                  | 0                | Difference                                                                                                       |

|----------|---------------------------------|---------------------------------|-------------------------|------------------|------------------------------------------------------------------------------------------------------------------|

| Position | Osition Bit ID Name/Description |                                 | Bit ID Name/Description |                  | Difference                                                                                                       |

| 31       | INT                             | Int-N or frac-N<br>mode control | _                       | Reserved         | The MAX2870 provides an additional method to switch between int and frac modes (Note 1).                         |

| 30–15    | N[15:0]                         | Integer division<br>value       | N16–<br>N1              | Integer value    | Both are 16-bit resolution, but the MAX2870 offers a wider usable range. See the MAX2870 data sheet for details. |

| 14–3     | FRAC[11:0]                      | Fractional division value       | F12–<br>F1              | Fractional value | N/A                                                                                                              |

| 2-0      | ADDR[2:0]                       | Register address                | C3-<br>C1               | Register address | N/A                                                                                                              |

| Bit      | MAX2870   |                                                                                                                    | ADF4350                 | 0                       | Difference                                                                                                                                                    |  |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------|-------------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Position | Bit ID    | Name/Description                                                                                                   | Bit ID Name/Description |                         | Difference                                                                                                                                                    |  |

| 31       | CPOC      | CP output clamp:<br>set to 1 for int<br>mode; set to 0<br>for frac mode                                            | _                       | Reserved                | The MAX2870 provides programmability on the CP output clamp to achieve better noise performance in int-N mode.                                                |  |

| 30–29    | CPL[1:0]  | CP linearity: set<br>to 00 for int<br>mode; set to 01<br>for frac mode                                             | _                       | Reserved                | The MAX2870 provides programmability for CP linearity to achieve better spurious performance in frac-N mode.                                                  |  |

| 28       | CPT[1]    |                                                                                                                    | _                       | Reserved                | On the ADF4350,                                                                                                                                               |  |

| 27       | CPT[0]    | Charge pump test<br>mode: 00 for<br>normal operation;<br>10 for CP in<br>source mode; 11<br>for CP in sink<br>mode | PR1                     | Prescaler               | users set bit 27 to program the prescaler value. On the MAX2870, the prescaler is automatically set. Users must set only CPT[1:0] to 00 for normal operation. |  |

| 26–15    | P[11:0]   | Phase value                                                                                                        | P12–<br>P1              | Phase value             | N/A                                                                                                                                                           |  |

| 14–3     | M[11:0]   | Modulus value                                                                                                      | M12-<br>M1              | Interpolator<br>modulus | N/A                                                                                                                                                           |  |

| 2-0      | ADDR[2:0] | Register address                                                                                                   | C3-<br>C1               | Register address        | N/A                                                                                                                                                           |  |

| Bit      | MAX2870  |                                                                                               | ADF4350     | 0                           | D."                                                                                                                           |

|----------|----------|-----------------------------------------------------------------------------------------------|-------------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Position | Bit ID   | Name/Description                                                                              | Bit ID      | Name/Description            | Difference                                                                                                                    |

| 31       | LDS      | Lock detect<br>speed                                                                          | _           | Reserved                    | The MAX2870 provides 4ns lock detect precision when PFD frequency is greater than 32MHz (Note 2).                             |

| 30–29    | SDN[1:0] | Frac-N noise mode 00 = low-noise mode 01 = reserved 10 = low-spur mode 1 11 = low-spur mode 2 | w-noise     |                             | The MAX2870 provides two modes of dithering for spur mitigation. Users should choose the one that works best in their system. |

| 28–26    | MUX[2:0] | MUX_OUT configuration                                                                         | M3-<br>M1   | MUXOUT                      | The MAX2870 has the same mux output, plus an extra serial output to be read out of Register 6 (Note 3).                       |

| 25       | DBR      | Reference<br>doubler mode                                                                     | RD2         | Reference<br>doubler        | N/A                                                                                                                           |

| 24       | RDIV2    | Reference Div2<br>mode                                                                        | RD1         | Reference<br>divideby2      | N/A                                                                                                                           |

| 23–14    | R[9:0]   | Reference divider mode                                                                        | R10–<br>R1  | 10-bit R counter            | N/A                                                                                                                           |

| 13       | REG4DB   | Double buffer                                                                                 | D1          | Double buffer               | N/A                                                                                                                           |

| 12–9     | CP[3:0]  | Charge-pump current                                                                           | CP4-<br>CP1 | Charge pump current setting | N/A                                                                                                                           |

| 8        | LDF      | Lock-detect function                                                                          | U6          | LDF                         | N/A                                                                                                                           |

| 7        | LDP      | Lock-detect precision                                                                         | U5          | LDP                         | N/A                                                                                                                           |

| 6        | PDP      | Phase detector polarity                                                                       | U4          | PD POLARITY                 | N/A                                                                                                                           |

| 5        | SHDN     | Power-down mode                                                                               | U3          | Power down                  | N/A                                                                                                                           |

| 4        | TRI      | Charge-pump three-state mode                                                                  | U2          | Cp three state              | N/A                                                                                                                           |

| 3   | RST       | Counter reset    | U1        | Counter reset    | N/A |

|-----|-----------|------------------|-----------|------------------|-----|

| 2–0 | ADDR[2:0] | Register address | C3–<br>C1 | Register address | N/A |

| Bit      | MAX2870    |                                                                       | ADF435     | 0                                      | D'''                                                                                                                               |

|----------|------------|-----------------------------------------------------------------------|------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| Position | Bit ID     | Name/Description                                                      | Bit ID     | Name/Description                       | Difference                                                                                                                         |

| 31–26    | VCO[5:0]   | Manual VCO<br>selection and<br>VCO subband<br>when VAS is<br>disabled | _          | Reserved                               | The MAX2870<br>allows the user to<br>disable VCO<br>autoselection<br>(VAS) machine                                                 |

| 25       | VAS_SHDN   | VAS SHDN:<br>0 = VAS enabled;<br>1 = VAS disabled                     | _          | Reserved                               | and manually<br>select VCO<br>subband. Use this<br>function with a                                                                 |

| 24       | RETUNE     | Sets VAS<br>response to<br>temperature drift                          | _          | Reserved                               | VCO lookup table<br>method to<br>achieve faster<br>PLL lock time.                                                                  |

| 23–19    | _          | Reserved                                                              | _          | Reserved                               | N/A                                                                                                                                |

| 18       | _          | Reserved                                                              | F1         | CSR                                    | Yes                                                                                                                                |

| 17       | _          | Reserved                                                              | _          | Reserved                               | N/A                                                                                                                                |

| 16–15    | CDM[1:0]   | Clock divider<br>mode:<br>10 = phase mode                             | C2-<br>C1  | Clock div mode:<br>10 = resync<br>mode | The MAX2870 only provides a phase change from the current phase, where the ADF4350 allows a phase relative to a sync pulse.        |

| 14–3     | CDIV[11:0] | Clock divider<br>value                                                | D12–<br>D1 | 12-bit clock<br>divider value          | These bits define the low-frequency clock ratio on both parts; depending on operation mode, they have different meanings (Note 4). |

| 2-0      | ADDR[2:0]  | Register address                                                      | C3-<br>C1  | Register address                       | N/A                                                                                                                                |

| Bit      | MAX2870      |                                                                                    | ADF4350     | 0                                           | D''                                                                                                                              |

|----------|--------------|------------------------------------------------------------------------------------|-------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Position | Bit ID       | Name/Description                                                                   | Bit ID      | Name/Description                            | Difference                                                                                                                       |

| 31–26    | _            | Reserved                                                                           | _           | Reserved                                    | Set to 011000<br>on the<br>MAX2870.                                                                                              |

| 25–24    | BS_MSBs[1:0] | Band-select<br>MSBs                                                                | _           | Reserved                                    | Because the MAX2870 allows higher PDF frequency, these additional bits increase the band-select divider range from 8 to 10 bits. |

| 23       | FB           | VCO feedback mode                                                                  | D13         | Feedback select                             | N/A                                                                                                                              |

| 22–20    | DIVA[2:0]    | RFOUT_ output divider mode                                                         | D12-<br>D10 | RF divider select                           | The MAX2870 provides more RFOUT divider ratio options (Note 5).                                                                  |

| 19–12    | BS[7:0]      | Sets band-select<br>clock-divider<br>value. MSBs are<br>located in bits<br><25:24> | BS8–<br>BS1 | 8-bit BAND<br>select clock<br>divider value | Same for the<br>8-bit band-<br>select divider.<br>The MAX2870<br>offers two more<br>MSBs (see<br>BS_MSBs[1:0]).                  |

| 11       | _            | Reserved                                                                           | D9          | VCO power down                              | Yes                                                                                                                              |

| 10       | _            | Reserved                                                                           | D8          | Mute till lock<br>detect                    | Yes                                                                                                                              |

| 9        | BDIV         | RFOUTB output path select                                                          | D7          | AUX out select                              | N/A                                                                                                                              |

| 8        | RFB_EN       | RFOUTB output mode                                                                 | D6          | AUX out enable                              | N/A                                                                                                                              |

| 7–6      | BPWR[1:0]    | RFOUTB output power                                                                | D5–<br>D4   | AUX out power                               | N/A                                                                                                                              |

| 5        | RFA_EN       | RFOUTA output mode                                                                 | D3          | RF out enable                               | N/A                                                                                                                              |

| 4        | APWR[1:0]    | RFOUTA output power                                                                | D2-<br>D1   | Output power                                | N/A                                                                                                                              |

|          |              |                                                                                    | C3-         |                                             |                                                                                                                                  |

| 2–0 | ADDR[2:0] | Register address | C1 | Register address | N/A |

|-----|-----------|------------------|----|------------------|-----|

|-----|-----------|------------------|----|------------------|-----|

| Bit      | MAX2870   |                          | ADF435      | 0                | Difference                                                                            |

|----------|-----------|--------------------------|-------------|------------------|---------------------------------------------------------------------------------------|

| Position | Bit ID    | Name/Description         | Bit ID      | Name/Description | Difference                                                                            |

| 31–25    | _         | Reserved                 | _           | Reserved         | N/A                                                                                   |

| 24       | F01       | F01                      | _           | Reserved         | The MAX2870 provides an additional method to control int/frac mode ( <b>Note 1</b> ). |

| 23–22    | LD[1:0]   | Lock-detect pin function | D15-<br>D14 | LD PIN mode      | N/A                                                                                   |

| 21–19    | _         | Reserved                 | _           | Reserved         | N/A                                                                                   |

| 18       | MUX[3]    | MUX MSB                  | _           | Reserved         | The MAX2870 provides additional serial data output on MUX pin ( <b>Note 3</b> ).      |

| 17       | _         | Reserved                 | _           | Reserved         | N/A                                                                                   |

| 16–3     | _         | Reserved                 | _           | Reserved         | N/A                                                                                   |

| 2–0      | ADDR[2:0] | Register address         | C3–<br>C1   | Register address | N/A                                                                                   |

## Loop Filter

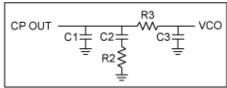

The MAX2870's KVCO (typical 100MHz/V) is different than the ADI4350's (typical 33MHz/V). To keep PLL parameters (e.g., CP current, N divider, Fcomp, loop BW, and phase margin) unchanged, the loop filter components must be recalculated (**Figure 1**). Using ADI4350's loop filter on the MAX2870 without careful evaluation could result in performance degradation or even unstable PLL.

Figure 1. Loop filter component labels.

The following example shows that to maintain the PLL's parameters, a different loop filter needs to be installed, depending on whether the MAX2870 or ADI4350 is being used.

| PLL Condition and Loop Filter | MAX2870 | ADF4350 | Notes                 |

|-------------------------------|---------|---------|-----------------------|

| KVCO (MHz/V)                  | 100     | 33      | Different KVCO        |

| ICP (mA)                      | 2.5     | 2.5     | Same                  |

| Fcomp (MHz)                   | 10      | 10      | Same                  |

| N                             | 400     | 400     | Same                  |

| Loop BW (kHz)                 | 20.2    | 17.6    | Similar loop BW       |

| Phase margin (deg)            | 39      | 37.5    | Similar phase margin  |

| C1 (nF)                       | 10      | 1.5     | Different loop filter |

| C2 (nF)                       | 68      | 22      | Different loop filter |

| R2 (Ω)                        | 220     | 430     | Different loop filter |

| C3 (nF)                       | 1.2     | 0.68    | Different loop filter |

| R3 (Ω)                        | 1000    | 820     | Different loop filter |

### Notes

**Note 1**: Although the MAX2870 and ADF4350 behave identically in the first method for int/frac mode switching, the MAX2870 provides an additional method to allow users to switch between the integer/fractional mode, independent of the FRAC[11:0] setting.

| Int/Frac Mode<br>Switching |                 | MAX2870 |     |                   | ADF4350           |                                            |

|----------------------------|-----------------|---------|-----|-------------------|-------------------|--------------------------------------------|

|                            |                 | F01     | INT | FRAC11-<br>FRAC00 | FRAC11-<br>FRAC00 | Notes                                      |

| Method<br>1                | Integer<br>mode | 1       | X   | All 0s            | All 0s            | N/A                                        |

| '                          | Frac mode       | 1       | Χ   | Not all 0s        | Not all 0s        | N/A                                        |

| Method                     | Integer<br>mode | 0       | 1   | X                 | N/A               | The MAX2870 provides an additional method. |

| 2                          | Frac mode       | 0       | 0   | X                 | N/A               | The MAX2870 provides an additional method. |

**Note 2**: The MAX2870 allows users to set a PDF frequency of up to 105MHz in int mode and 50MHz in frac mode, while the ADF4350's maximum PDF frequency is 32MHz. The table below summarizes the LD pin setting between the MAX2870 and ADF4350 under different PDF frequencies.

| LD Pin        | MAX2870 |     |     |     | ADF4350 |     |     | Notes                                                                                 |

|---------------|---------|-----|-----|-----|---------|-----|-----|---------------------------------------------------------------------------------------|

| Function      | LD[1:0] | LDS | LDP | LDF | D15-D14 | LDP | LDF | Notes                                                                                 |

| Low           | 00      | Χ   | X   | X   | 00      | X   | X   | Same as ADF4350                                                                       |

|               |         | 0   | 0   | 0   |         | 0   | 0   | Same as ADF4350,<br>for PDF frequency <<br>32MHz, frac-N mode,<br>10ns precision      |

|               |         | 0   | 0   | 1   |         | 0   | 1   | Same as ADF4350,<br>for PDF frequency <<br>32MHz, integer mode,<br>10ns precision     |

|               |         | 0   | 1   | 0   |         | 1   | 0   | Same as ADF4350,<br>for PDF frequency <<br>32MHz, frac-N mode,<br>6ns precision       |

| Digital<br>LD | 01      | 0   | 1   | 1   | 01      | 1   | 1   | Same as ADF4350,<br>for PDF frequency <<br>32MHz, integer mode,<br>6ns precision      |

|               |         | 1   | X   | 0   |         | _   | _   | The MAX2870 digital LD function for PDF frequency > 32MHz, frac-N mode, 4ns precision |

|               |         | 1   | Х   | 1   |         | _   | _   | The MAX2870 digital LD function for PDF frequency > 32MHz, int mode, 4ns precision    |

| Analog<br>LD  | 10      | Χ   | Χ   | X   | 10      | X   | Χ   | Same as ADF4350                                                                       |

| High          | 11      | Χ   | Χ   | Χ   | 11      | X   | X   | Same as ADF4350                                                                       |

Note 3: The table below summarizes the MUX pin setting of the MAX2870 and ADF4350.

| MUX Pin                        | MAX2870                                 |         | ADF4350                       |         |                                                                                                                                        |

|--------------------------------|-----------------------------------------|---------|-------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| Function                       | MUX[3] MUX[2:0]<br>REG5[18] REG2[28:26] |         | REG5[18] M3-M1<br>REG2[28:26] |         | Notes                                                                                                                                  |

| Regular<br>MUX pin<br>function | 0                                       | 000–111 | Reserved                      | 000–111 | N/A                                                                                                                                    |

| Serial<br>data<br>output       | 1                                       | 100     | _                             | _       | The MAX2870 configures the MUX_OUT pin as serial data output to read REG 06 (IC status bits). The ADF4350 does not have this function. |

Note 4: Below is a comparison of the CDIV bits function under different modes.

| Operation Mode    | MAX2870                                                                               | ADF4350                                |

|-------------------|---------------------------------------------------------------------------------------|----------------------------------------|

|                   | CDIV[11:0], Reg3[14:3]                                                                | D12-D1, Reg3[14:3]                     |

| Fast lock mode    | CDIV defines the fast lock timeout                                                    | Defines the fast lock timeout          |

| Phase adjust mode | Adjusts the VCO phase relative to the current phase, so no resync period is necessary | D12-D1 define the phase resync period. |

Note 5: The MAX2870 provides more output divider ratio selection, allowing more design flexibility.

| Output-<br>Divider Ratio | MAX2870                | ADF4350              |

|--------------------------|------------------------|----------------------|

|                          | DIVA[2:0], Reg4[22:20] | D12-D10, Reg4[22:20] |

| 1                        | 000                    | 000                  |

| 2                        | 001                    | 001                  |

| 4                        | 010                    | 010                  |

| 8                        | 011                    | 011                  |

| 16                       | 100                    | 100                  |

| 32                       | 101                    | Not available        |

| 64                       | 110                    | Not available        |

| 128                      | 111                    | Not available        |

| Related Parts |                                                         |              |  |

|---------------|---------------------------------------------------------|--------------|--|

| MAX2870       | 23.5MHz to 6000MHz Fractional/Integer-N Synthesizer/VCO | Free Samples |  |

#### **More Information**

For Technical Support: http://www.maximintegrated.com/support

For Samples: http://www.maximintegrated.com/samples

Other Questions and Comments: http://www.maximintegrated.com/contact

Application Note 5498: http://www.maximintegrated.com/an5498

APPLICATION NOTE 5498, AN5498, AN 5498, APP5498, Appnote 5498

Copyright © by Maxim Integrated

Additional Legal Notices: http://www.maximintegrated.com/legal