**DLPA300** DLPS227 - OCTOBER 2021

# **DLPA300 DMD Micromirror Driver**

#### 1 Features

- Generates the micromirror clocking pulses required by the 9-um pixel DMDs

- Generates specialized voltage levels required for micromirror clocking pulse generation

- Designed for the 9-um pixel DMDs

- DLP780NE

- DLP780TE

- DLP800RE

# 2 Applications

- Enterprise projector

- Smart projector

- Laser TV

- Digital signage

# 3 Description

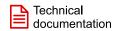

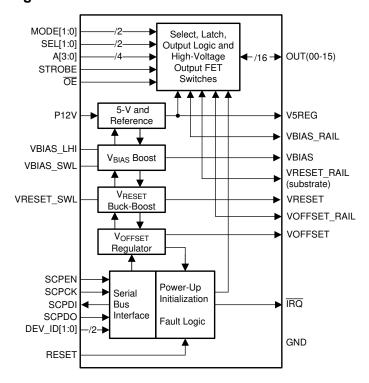

The DLPA300 micromirror driver generates the V<sub>OFFSET</sub> and V<sub>BIAS</sub> voltages. It also switches V<sub>OFFSET</sub>,  $V_{\text{BIAS}}$  and an externally generated  $V_{\text{RESET}}$  to create the micromirror clocking pulses for the 9-um pixel, high efficiency DMDs, that include the DLP780NE, DLP780TE and DLP800RE DMDs. The timing of this waveform is controlled by the display controller, either DLPC430 or DLPC4420. The DLPA300 micromirror driver is part of the TI DLP® Products DLP780NE, DLP780TE and DLP800RE chipsets.

#### **Device Information**

| PART NUMBER <sup>(1)</sup> | PACKAGE    | BODY SIZE           |

|----------------------------|------------|---------------------|

| DLPA300                    | HTQFP (80) | 14.00 mm × 14.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

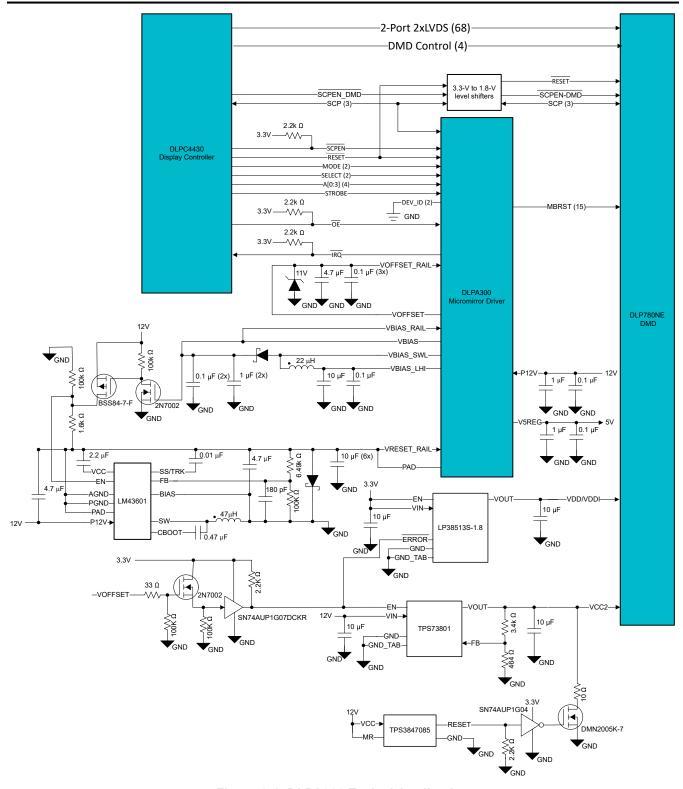

Figure 3-1. Simplified Application

# **Table of Contents**

| 1 Features1                                  | 7.4 Device Functional Modes                          | 15 |

|----------------------------------------------|------------------------------------------------------|----|

| 2 Applications1                              | 8 Application and Implementation                     | 16 |

| 3 Description1                               | 8.1 Application Information                          | 16 |

| 4 Revision History2                          | 8.2 Typical Application                              |    |

| 5 Pin Configuration and Functions3           | 9 Power Supply Recommendations                       | 21 |

| 6 Specifications6                            | 9.1 Power Supply Rail Guidelines                     | 21 |

| 6.1 Absolute Maximum Ratings6                | 10 Layout                                            | 22 |

| 6.2 ESD Ratings6                             | 10.1 Layout Guidelines                               |    |

| 6.3 Recommended Operating Conditions6        | 10.2 Thermal Considerations                          | 22 |

| 6.4 Thermal Information7                     | 11 Device and Documentation Support                  | 23 |

| 6.5 Electrical Characteristics Control Logic | 11.1 Device Support                                  | 23 |

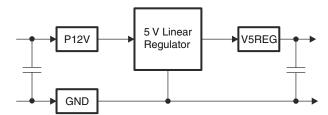

| 6.6 5-V Linear Regulator8                    |                                                      | 23 |

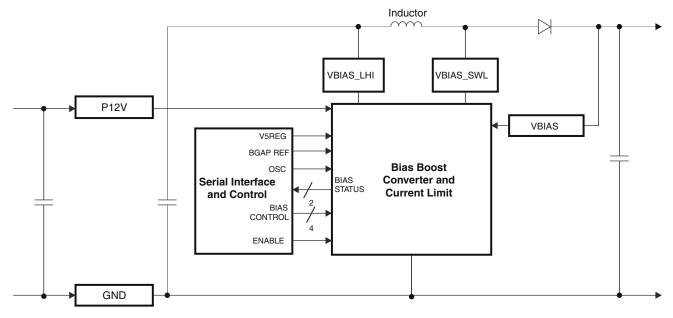

| 6.7 Bias Voltage Boost Converter8            | 11.3 Receiving Notification of Documentation Updates | 23 |

| 6.8 Reset Voltage Buck-Boost Converter9      | 11.4 Support Resources                               | 23 |

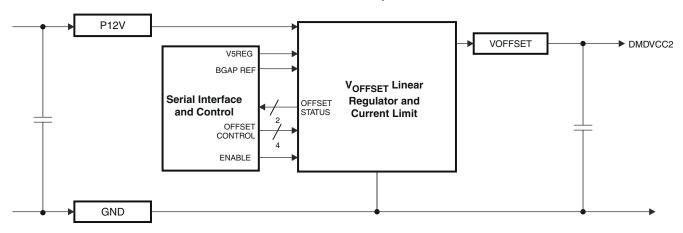

| 6.9 V <sub>OFFSET</sub> Regulator9           | 11.5 Trademarks                                      | 23 |

| 6.10 Switching Characteristics10             | 11.6 Electrostatic Discharge Caution                 | 24 |

| 7 Detailed Description12                     | 11.7 Glossary                                        | 24 |

| 7.1 Overview12                               | 12 Mechanical, Packaging, and Orderable              |    |

| 7.2 Functional Block Diagram12               |                                                      | 24 |

| 7.3 Feature Description13                    |                                                      |    |

|                                              |                                                      |    |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE         | REVISION | NOTES           |

|--------------|----------|-----------------|

| October 2021 | *        | Initial Release |

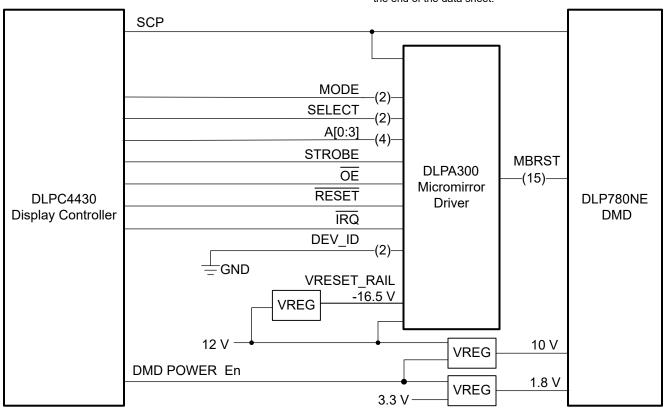

# **5 Pin Configuration and Functions**

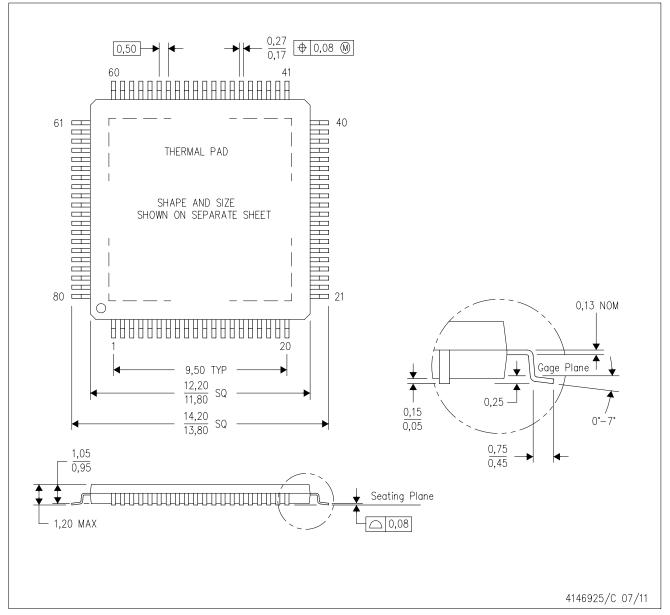

Figure 5-1. PFP Package 80-Pin HTQFP Top View

Table 5-1. Package Pinout

| PIN        |                                      | I/O               | able 5-1. Package Pinout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|------------|--------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME       | NO.                                  | (INPUT            | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|            |                                      | DEFAULT)          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT00      | 22                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT01      | 24                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT02      | 27                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT03      | 29                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT04      | 32                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT05      | 34                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT06      | 37                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT07      | 39                                   | Output            | 16 micromirror clocking waveform outputs (enabled by $\overline{OE} = 0$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| OUT08      | 62                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT09      | 64                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT10      | 67                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT11      | 69                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT12      | 72                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT13      | 74                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT14      | 77                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| OUT15      | 79                                   | Output            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| A0         | 19                                   | Input (pull down) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| A1         | 18                                   | Input (pull down) | Output Address. Used to select which OUTxx pin is active at a given time.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| A2         | 17                                   | Input (pull down) | Supervisuals of the supervisual supervisua |  |  |  |  |

| A3         | 16                                   | Input (pull down) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| MODE0      | 3                                    | Input (pull down) | Mode Select. Used to determine the operating mode of the DLPA300.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| MODE1      | 2                                    | Input (pull down) | who do oblest. Osed to determine the operating mode of the BET/1000.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| SEL0       | 5                                    | Input (pull down) | Output Voltage Select. Used to switch the voltage applied to the addressed OUTxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| SEL1       | 4                                    | Input (pull down) | pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| STROBE     | 15                                   | Input (pull down) | A rising edge on STROBE latches in the control signals after a tri-state delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| ŌĒ         | 6                                    | Input (pull up)   | Asynchronous input controls whether the 16 OUTxx pins are active or are in a in high-impedance state. $\overline{OE} = 0$ : Enabled. $\overline{OE} = 1$ : High Z.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| RESET      | 59                                   | Input (pull up)   | Resets the DLPA300 internal logic. Active low. Asynchronous.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

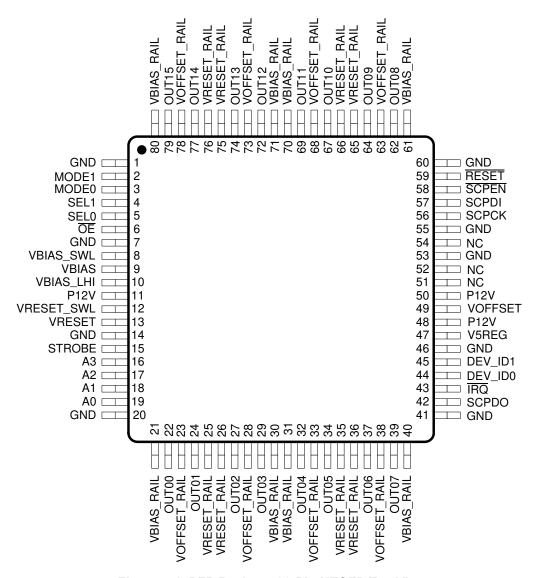

| SCPEN      | 58                                   | Input (pull up)   | Enables serial bus data transfers. Active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| SCPDI      | 57                                   | Input (pull down) | Serial bus data input. Clocked in on the falling edge of SCPCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| SCPCK      | 56                                   | Input (pull down) | Serial bus clock. Provided by chipset Controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| SCPDO      | 42                                   | Output            | Serial bus data output (open drain). Clocked out on the rising edge of SCPCK. A $1k\Omega$ pull up resistor to the Chip-Set Controller $V_{DD}$ supply is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| ĪRQ        | 43                                   | Output            | Interrupt request output to the chipset Controller. Active low. A 1 k $\Omega$ pull up resistor to the Chip-Set Controller V <sub>DD</sub> supply is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |