SWRS083A-SEPTEMBER 2009-REVISED NOVEMBER 2009

# PASSIVE LOW FREQUENCY INTERFACE DEVICE WITH EEPROM AND 134.2 kHz TRANSPONDER INTERFACE

Check for Samples: TMS37157

## FEATURES

- Wide Supply Voltage Range 2 V to 3.6 V

- Ultra Low Power Consumption

- Active Mode Max. 150 μA

- Power Down Mode 60 nA

- 121 Free Bytes User Memory

- Low Frequency Halb Duplex (HDX) Interface

- HDX Transponder Communication Achieving Maximum Perfomance and Highest Noise Immunity

- Special Selective Addressing Mode Allows Anti Collision

- Up to 8 kbit/s LF Uplink Data Rate

- 126 Byte EEPROM:

- 121 Bytes Free Available EEPROM User Memory

- 32 Bit Unique Serial Number

- 8 Bit Selective Address

- High EEPROM Flexibility

- Pages are Irreversible Lockable and Protectable

- Battery Check and Battery Charge Function

- Resonance Frequency: 134.2 kHz

- Integrated Resonance Frequency Trimming

- Downlink Amplitude Shift Keying

- Uplink Frequency Shift Keying

- 3 Wire SPI Interface for Accessing the EEPROM and Exchanging Data With the Microcontroller Through the LF Interface

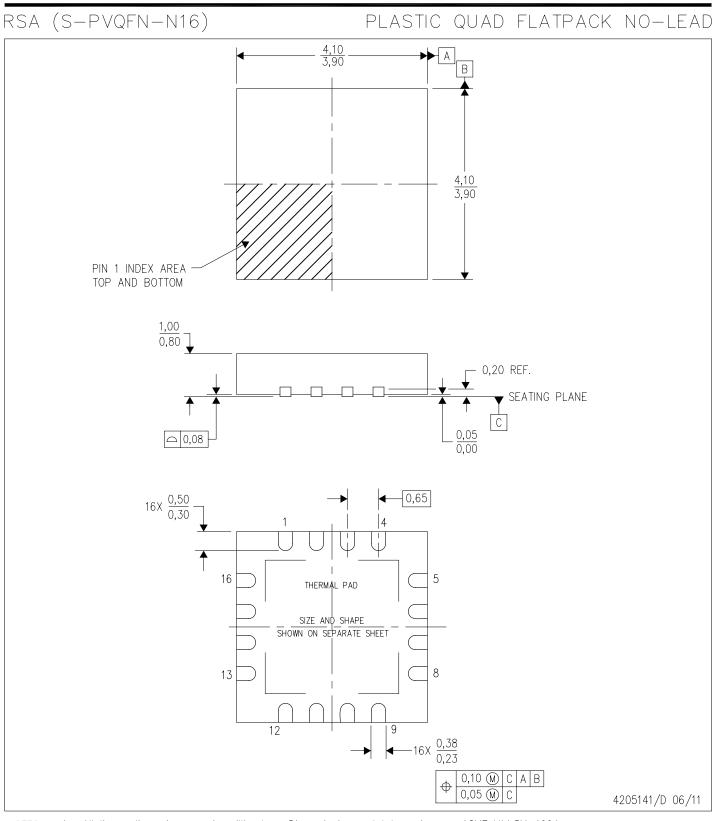

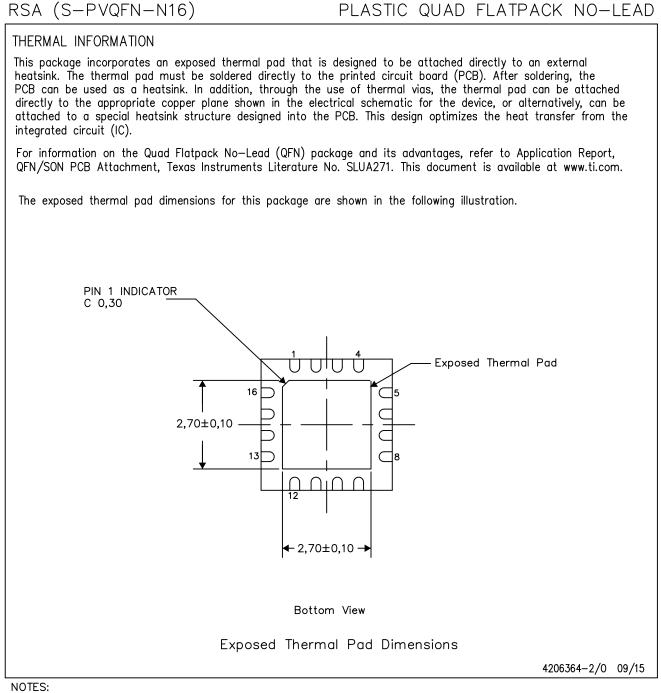

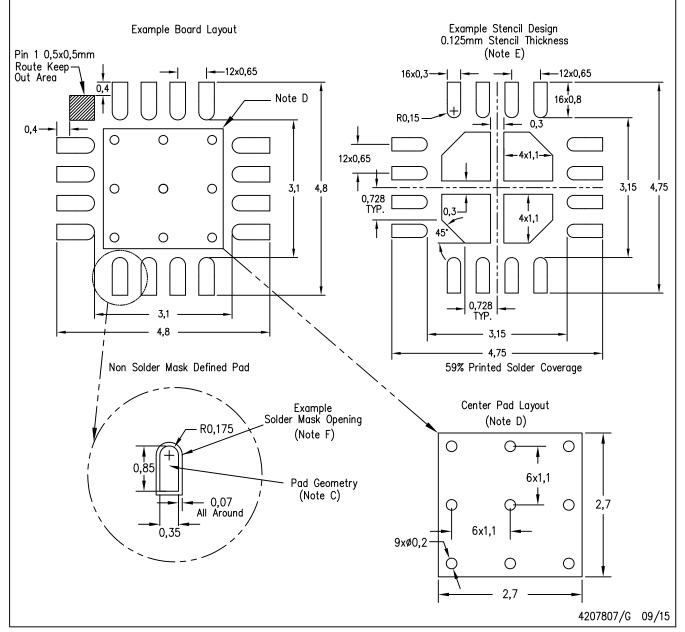

- 0.6mm Pitch, 4mm x 4mm VQFN Package

## APPLICATIONS

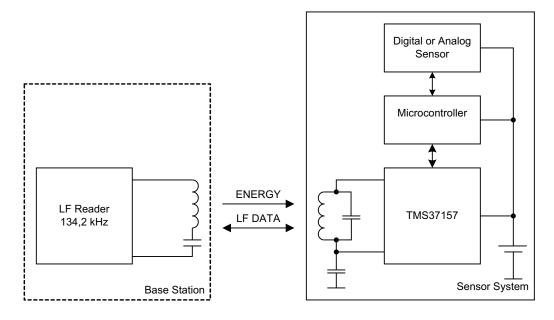

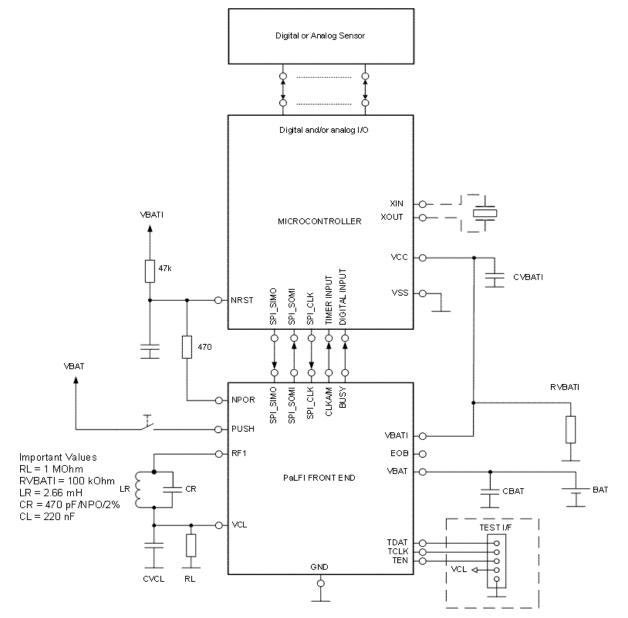

- Wireless Batteryless Sensor Interface using Energy Harvesting

- Microcontroller and Sensor can be Powered Through the LF Link

- Data is Directly Transmitted Over the LF Link From the Base Station via the TMS37157 to the Micrcontroller and Vice Versa.

- Batteryless Configuration Memory

- Memory can be Written Without Battery Support

- Microcontroller can Read the Content of the Memory When It Gets Connected to a Battery and Use It for Configuration

- Microcontroller can Write the Memory, Which can be Read Out Later Through the LF Link

- Ultra Low Power Data Logger Memory (Smart Metering)

- Memory Can Be Written By a Microcontroller

- Memory Can Be Read Through LF Interface Without Battery Support

- Multi Purpose LF Interface to a Microcontroller

- Short Range RF Interface to a Microcontroller Where Other Frequencies are Not an Option

- Ultra Low Power Mode can Result in an Overall Power Consumption of 60 nA

- Remote Control Application

- Combination With an UHF Transmitter or IR Transmitter and a  $\mu$ C

- Power Management of the TMS37157 can Power Down the Microcontroller

- The Push Button Detection Circuit can Power Up a Microcontroller

- Stand Alone LF-Transponder with Memory

- RFID Transponder with Unique ID and 121 Bytes Free Programmable EEPROM User Memory

- Only Few Additional Components Needed

- No Battery Required

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## **DESCRIPTION/ORDERING INFORMATION**

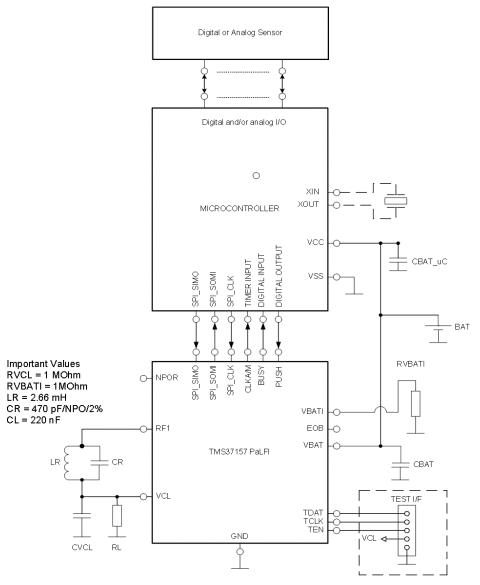

The TMS37157 combines a Low Frequency Transponder Interface with an SPI Interface and Power Management for a connected microcontroller. It is the ideal device for any Configuration, Data Logger-, Sensoror Remote Control Application. The Transponder memory is accessible through SPI and LF and, in the second case, operates without the need for a battery. The use of the Low Frequency Band ensures a communication in a defined direction and harsh environments.

The TMS37157 manages the Transponder communication and push button interaction. During sleep state the devices enters a special low power mode with only 60 nA current consumption.

The EEPROM memory is accessible over the LF interface without support from the battery or through SPI by a microcontroller if a battery is connected. The TMS37157 offers a special battery charge mode.

The external resonance circuit with a LF coil and a resonance capacitor can be trimmed to the correct resonance frequency with the integrated trimming capability achieving an easy way to eliminate part tolerances.

The small RSA 16-pin package together with only a few external components results in a cost efficient design.

#### SWRS083A-SEPTEMBER 2009-REVISED NOVEMBER 2009

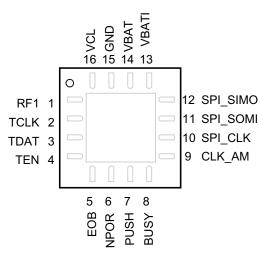

#### **TERMINAL FUNCTIONS**

| TERM     | IINAL | 1/0 | DESCRIPTION                                                                                                                                                                                                      |

|----------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     |       |     | DESCRIPTION                                                                                                                                                                                                      |

| RF1      | 1     | I   | Antenna                                                                                                                                                                                                          |

| TCLK     | 2     | I   | Test interface - clock input. Data is shifted in and out of the TDAT pin on the rising edge of TCLK.                                                                                                             |

| TDAT     | 3     | I/O | Test interface – bidirectional serial data I/O for configuration and trimming.                                                                                                                                   |

| TEN      | 4     | I   | Test interface – enable input.                                                                                                                                                                                   |

| EOB      | 5     | 0   | End of burst detector. This signal is high when the RF signal of the base station is OFF.                                                                                                                        |

| NPOR     | 6     | 0   | Active low power-on-reset (open drain) - can be used to reset the microcontroller.                                                                                                                               |

| PUSH     | 7     | I   | Input of the push button detector - can be used to recognize that a push event has occurred.                                                                                                                     |

| BUSY     | 8     | о   | <ul> <li>Indicates internal control unit activity:</li> <li>During initialization</li> <li>During transponder operation</li> <li>During SPI communication (handshaking)</li> </ul>                               |

| CLKA_M   | 9     | ο   | This output provides clock signals derived from the external antenna resonance circuit to the microcontroller. This function can be activated by an SPI command. Two frequencies are selectable FRES and FRES/4. |

| SPI_CLK  | 10    | I   | SPI clock input                                                                                                                                                                                                  |

| SPI_SOMI | 11    | 0   | SPI data output                                                                                                                                                                                                  |

| SPI_SIMO | 12    | I   | SPI data input                                                                                                                                                                                                   |

| VBATI    | 13    | PWR | Can be used as µC supply voltage                                                                                                                                                                                 |

| VBAT     | 14    | PWR | Battery supply                                                                                                                                                                                                   |

| GND      | 15    | PWR | Ground                                                                                                                                                                                                           |

| VCL      | 16    | PWR | Charge capacitor                                                                                                                                                                                                 |

### **ORDERING INFORMATION**

| T <sub>A</sub> | PACKA      | GE <sup>(1) (2)</sup> | ORDERABLE PART NUMBER | TOPSIDE MARKING |

|----------------|------------|-----------------------|-----------------------|-----------------|

| –40°C to 85°C  | VQFN – RSA | Reel of 3000          | TMS37157IRSARG4       | 371571          |

(1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

www.ti.com

## **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

over operating free-air temperature range (unless otherwise noted)

|                 |                                    | MIN  | MAX | UNIT |

|-----------------|------------------------------------|------|-----|------|

| T <sub>A</sub>  | Operating free air temperature     | -40  | 85  | °C   |

| Ts              | Storage temperature <sup>(2)</sup> | -40  | 125 | °C   |

| $V_{BAT}$       | Battery voltage                    | -0.3 | 3.6 | V    |

| V <sub>CL</sub> | V <sub>CL</sub> input voltage      |      | 7   | V    |

| I <sub>RF</sub> | Input current <sup>(3)</sup>       |      | 10  | mA   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) One cycle up to 1000h

(3) Continuous

## OPERATING CONDITIONS

|                  | PARAMETER                       |   | TYP | MAX  | UNIT |

|------------------|---------------------------------|---|-----|------|------|

| Q <sub>op</sub>  | Operating system quality factor |   | ≥30 |      |      |

| V <sub>BAT</sub> | Battery voltage                 | 2 | 3   | 3.55 | V    |

## IC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE

## SUPPLY AND REFERENCE CURRENTS

|                     | PARAMETER                                    |                                                     |  | TYP | MAX | UNIT |

|---------------------|----------------------------------------------|-----------------------------------------------------|--|-----|-----|------|

| IVBATI              | Current out of V <sub>BATI</sub>             | V <sub>BAT</sub> = 2.0 V                            |  |     | 16  | mA   |

| dVsw2               | Voltage drop at SW2 ( $V_{BAT} - V_{BATI}$ ) | $I_{BATI} = 16 \text{ mA}, V_{BAT} = 2.0 \text{ V}$ |  |     | 100 | mV   |

| I <sub>quiet</sub>  | Quiescent current                            | TMS37157 idle                                       |  | 60  | 300 | nA   |

| I <sub>active</sub> | Operating current                            | TMS37157 active                                     |  |     | 150 | μA   |

| I <sub>charge</sub> | Battery charge current                       |                                                     |  |     | 2   | mA   |

## **MODULATION CAPACITOR**

| PARAMETER |                      | MIN         | NOM | MAX | UNIT |    |

|-----------|----------------------|-------------|-----|-----|------|----|

| СМ        | Modulation capacitor | L = 2.66 mH |     | 110 |      | pF |

## FRONT END CONTROL

|                    | PARAMETER                         |                            |  | NOM                | MAX | UNIT |

|--------------------|-----------------------------------|----------------------------|--|--------------------|-----|------|

| t <sub>reset</sub> | TMS37157 front-end reset time     |                            |  |                    | 14  | ms   |

| t <sub>Hdet</sub>  | High bit detection threshold time | f <sub>TX</sub> = 134.2kHz |  | 64/f <sub>TX</sub> |     | us   |

## CHARACTERISTICS OF TRANSPONDER SECTION

|                     | PARAMETER                   |                           |  | NOM   | MAX | UNIT |

|---------------------|-----------------------------|---------------------------|--|-------|-----|------|

| t <sub>prebit</sub> | Prebit time                 | $f_L = 134.7 kHz$         |  | 1.9   |     | ms   |

| t <sub>trans</sub>  | High bit transition time of | start byte 0x7E           |  | 2     |     | ms   |

| t <sub>high</sub>   | High bit time               | f <sub>H</sub> = 123.7kHz |  | 0.129 |     | ms   |

| t <sub>low</sub>    | Low bit time                | $f_L = 134.7 kHz$         |  | 0.118 |     | ms   |

| T <sub>resp</sub>   | Response time               |                           |  | 12    |     | ms   |

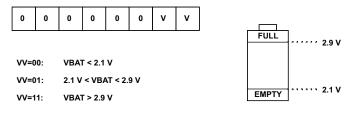

## **VCL/VBAT CHECKER**

|            | PARAMETER                                  |  |  | NOM | MAX | UNIT |

|------------|--------------------------------------------|--|--|-----|-----|------|

| High Level | V <sub>BAT</sub> checker threshold voltage |  |  | 2.9 |     | V    |

| Low Level  | $V_{\text{BAT}}$ checker threshold voltage |  |  | 2.1 |     | V    |

#### SWRS083A-SEPTEMBER 2009-REVISED NOVEMBER 2009

## VCL/VBAT CHECKER (continued)

|                     | PARAMETER                                 | MIN | NOM | MAX | UNIT |

|---------------------|-------------------------------------------|-----|-----|-----|------|

| V <sub>charge</sub> | V <sub>BAT</sub> charge voltage           |     | 3.4 |     | V    |

| Vch                 | V <sub>CL</sub> checker threshold voltage |     | 3.1 |     | V    |

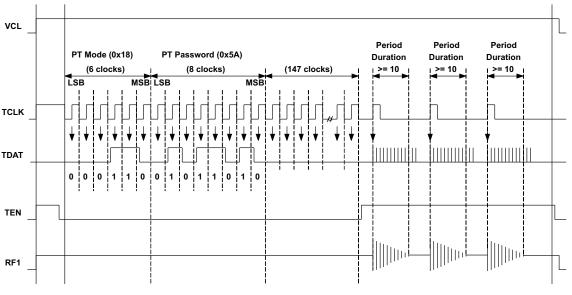

## TRIMMING CAPACITORS AND SWITCHES

|                   | PARAMETER                                         | MIN  | NOM  | MAX  | UNIT |

|-------------------|---------------------------------------------------|------|------|------|------|

| T <sub>step</sub> | Trimming steps                                    |      | 128  |      |      |

| C <sub>Tmin</sub> | Minimum trimming capacitor                        |      | 0    |      | pF   |

| C <sub>T1</sub>   | Trimming capacitor 1                              |      | 0.6  |      | pF   |

| C <sub>T2</sub>   | Trimming capacitor 2                              |      | 1.2  |      | pF   |

| C <sub>T3</sub>   | Trimming capacitor 3                              |      | 2.4  |      | pF   |

| C <sub>T4</sub>   | Trimming capacitor 4                              |      | 4.7  |      | pF   |

| C <sub>T5</sub>   | Trimming capacitor 5                              |      | 9.4  |      | pF   |

| C <sub>T6</sub>   | Trimming capacitor 6                              |      | 18.8 |      | pF   |

| C <sub>T7</sub>   | Trimming capacitor 7                              |      | 37.6 |      | pF   |

| CT                | Maximum trimming capacitor (CT = CT1+ CT2+ + CT7) | 63.5 | 74.4 | 85.9 | pF   |

## **RF LIMITER**

|                    | PARAMETER                       |                                                                                            | MIN  | NOM | MAX | UNIT |

|--------------------|---------------------------------|--------------------------------------------------------------------------------------------|------|-----|-----|------|

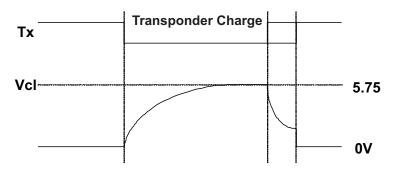

| V <sub>RFlim</sub> | RF limiter voltage              |                                                                                            | 10.5 | 12  | 14  | V    |

| V <sub>CLlim</sub> | Limited V <sub>CL</sub> voltage | Limited V <sub>CL</sub> voltage is the result of the RF limiter in the application circuit | 5.75 | 5.9 | 6.5 | V    |

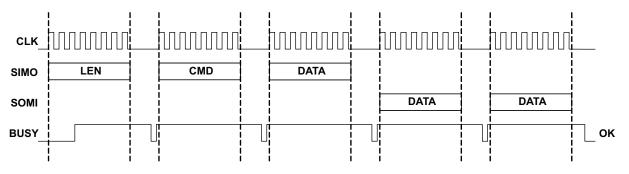

## **CONTROL AND SPI INTERFACE**

|                | PARAMETER     | MIN | NOM   | MAX | UNIT |

|----------------|---------------|-----|-------|-----|------|

| Busy low time  | See SPI Comm. |     | 30-70 |     | μs   |

| Busy high time | See SPI Comm. |     | 10-30 |     | ms   |

|                 | PARAMETEI                                    | R                                            | MIN            | NOM            | MAX            | UNIT |

|-----------------|----------------------------------------------|----------------------------------------------|----------------|----------------|----------------|------|

| V <sub>OL</sub> | Low level output voltage, SPI_SOMI,<br>BUSY  | $V_{BAT}$ = 2.03.6V, R <sub>L</sub> = 100 kΩ |                | 0.05 ×<br>VBAT | 0.07 ×<br>VBAT | V    |

| V <sub>OH</sub> | High level output voltage,<br>SPI_SOMI, BUSY | $V_{BAT}$ = 2.03.6V, R <sub>L</sub> = 100 kΩ | 0.93 ×<br>VBAT | 0.95 ×<br>VBAT |                | V    |

| V <sub>IL</sub> | Low level input voltage, SPI_SIMO, SPI_CLK   | $V_{BAT}$ = 2.03.6V, R <sub>L</sub> = 100 kΩ |                |                | 0.1 ×<br>VBAT  | V    |

| V <sub>IH</sub> | High level input voltage, SPI_SIMO, SPI_CLK  | $V_{BAT}$ = 2.03.6V, R <sub>L</sub> = 100 kΩ | 0.9 ×<br>VBAT  |                | VBAT           | V    |

## **ACTIVATION LIMIT OF TMS37157**

|      | PARAMETER                                 |                               | MIN  | NOM | MAX | UNIT |

|------|-------------------------------------------|-------------------------------|------|-----|-----|------|

| Vact | Activation level for transponder response | $f = 134.2 \text{ kHz}^{(1)}$ | 5.75 | 5.9 | 6.5 | V    |

(1) At beginning of the response the voltage V<sub>CL</sub> must be just limited. Only in this case the function is guaranteed if components and I<sub>C</sub> parameters are at the limit, see Figure 1. The voltage is measured at V<sub>CL</sub> just before the Transponder starts with the response protocol. The longest in the application used downlink telegram with maximum number of high bits should be used. The low and high bit response frequency should be at the lowest value which occurs in the application. In case of an additional power phase (Programming) the level has to be after that additional power phase.

www.ti.com

## Figure 1. Activation limit of TMS37157

### MEMORY

|                   | PARAMETE             | R                     | MIN | TYP    | MAX | UNIT   |

|-------------------|----------------------|-----------------------|-----|--------|-----|--------|

| P/E-C             | Program/erase cycles | 25°C                  |     | 200000 |     | Cycles |

| X <sub>DRET</sub> | Data retention       | T <sub>s</sub> = 25°C |     | 10     |     | Years  |

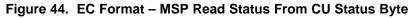

## TEST INTERFACE

|                   | PARAMETE                        | R                                        | MIN  | TYP | MAX  | UNIT |

|-------------------|---------------------------------|------------------------------------------|------|-----|------|------|

| R <sub>TCLK</sub> | Pull-down resistor, TCLK        |                                          | 7    | 10  | 25   | kΩ   |

| R <sub>TDAT</sub> | Pull-down resistor, TDAT        |                                          | 20   | 150 | 375  | kΩ   |

| R <sub>TEN</sub>  | Pull-down resistor, TEN         |                                          | 5    | 10  | 25   | kΩ   |

| V <sub>OL</sub>   | Low level output voltage, TDAT  | $V_{CL} = 5V, R_L = 2.5 \text{ k}\Omega$ |      |     | 0.25 | V    |

| V <sub>OH</sub>   | High level output voltage, TDAT | $V_{CL}$ = 5V, $R_L$ = 2.5 k $\Omega$    | 4.75 |     |      | V    |

## TRANSPONDER MODE

## TRANSPONDER TIMING USING PPM

|                      | PARAMETER                                                          | MIN | TYP | MAX  | UNIT |

|----------------------|--------------------------------------------------------------------|-----|-----|------|------|

| PPM - Pu             | ulse Position Modulation                                           | ·   |     |      |      |

| t <sub>offtrp</sub>  | Write pulse pause (PPM) <sup>(1)</sup>                             |     | 170 |      | μs   |

| t <sub>ontrpL</sub>  | Write pulse activation/ low bit (PPM) <sup>(1)</sup>               |     | 230 |      | μs   |

| t <sub>ontrpH</sub>  | Write pulse activation/ high bit (PPM) <sup>(1)</sup>              |     | 350 |      | μs   |

| t <sub>bittrpL</sub> | Write low bit period <sup>(1)</sup>                                |     | 400 |      | μs   |

| t <sub>bittrpH</sub> | Write high bit period <sup>(1)</sup> <sup>(2)</sup> <sup>(3)</sup> | 510 | 520 | 1730 | μs   |

(1) This timing is measured at the transponder using a pickup coil. This timing is with Low Bit Frequency = 134.7kHz and is influenced by various factors e.g. detuning and coupling to the reader antenna and. Out of this timing the low and high bit are detected by the transponder logic.

(2) Except the last bit this limitation of the duration is valid for all downlink bits.

(3) To detect a High bit the absolute minimum of  $t_{bittrpH} = 510 \ \mu s$  must be met.

## **READER RECOMMENDATIONS**

|                    | PARAMETER                       | MIN    | TYP   | MAX    | UNIT |

|--------------------|---------------------------------|--------|-------|--------|------|

| QTX,<br>QRX        | Reader operating quality factor |        |       | 10     |      |

| f <sub>TX</sub>    | Transmitter frequency           | 134.16 | 134.2 | 134.24 | kHz  |

| t <sub>TX</sub>    | Charge time                     | 20     | 25    |        | ms   |

| t <sub>TXoff</sub> | Transmitter off time            | 3      |       |        | ms   |

| t <sub>prog</sub>  | Programming time                | 15     |       |        | ms   |

| t <sub>RD</sub>    | Read time                       | 14.9   | 15    |        | ms   |

#### SWRS083A-SEPTEMBER 2009-REVISED NOVEMBER 2009

## READER TIMINGS USING PPM

|                   | PARAMETER                              | MIN | TYP | MAX  | UNIT |

|-------------------|----------------------------------------|-----|-----|------|------|

| PPM - F           | Pulse Position Modulation              |     |     |      |      |

| t <sub>off</sub>  | Off time (PPM) <sup>(1)</sup>          |     | 170 |      | μs   |

| t <sub>onL</sub>  | Low bit on time (PPM) <sup>(1)</sup>   |     | 230 |      | μs   |

| t <sub>bitL</sub> | Low bit duration (PPM) <sup>(1)</sup>  |     | 400 |      | μs   |

| t <sub>onH</sub>  | High bit on time <sup>(1)</sup>        |     | 350 |      | μs   |

| t <sub>bitH</sub> | High bit duration (PPM) <sup>(1)</sup> |     | 520 | 1730 | μs   |

(1) Timing recommendation is only valid for a Reader Operating Quality Factor  $QTX = QRX \le 10$ .

## ANTENNA CURRENTS FOR EQUIVALENT FIELD STRENGTH LEVELS

|                                   | PARAMETER                                   | MIN               | ТҮР | MAX | UNIT |

|-----------------------------------|---------------------------------------------|-------------------|-----|-----|------|

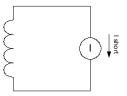

| I <sub>short</sub> <sup>(1)</sup> | Equivalent current for operation (True RMS) | I <sub>prog</sub> |     | 4.3 | mA   |

(1) The circuit below is used to determine equivalent short circuit current at the position of the TMS37157 transponder coil. The measured value must be equal or above the specified value in the table above. The operating Q factor Qop depends on used components (L, C) and the application environment.

|                   | PARAMETER                                            |                          | Ishort                      | Ishort                      | UNIT |

|-------------------|------------------------------------------------------|--------------------------|-----------------------------|-----------------------------|------|

|                   |                                                      |                          | T <sub>charge</sub> = 20 ms | T <sub>charge</sub> = 25 ms |      |

| I <sub>prog</sub> | Equivalent for programming activation field strength | Qop ≥ 60<br>–40 to 85 °C | 0.32                        | 0.23                        | mA   |

| I <sub>prog</sub> | Equivalent for programming activation field strength | Qop ≥ 30<br>–40 to 85 °C | 0.64                        | 0.46                        | mA   |

Figure 2. Short Circuit Current

## **RECOMMENDED EXTERNAL COMPONENTS**

#### ANTENNA

|                      | PARAMETER                                    | TEST CONDITIONS                       | MIN   | NOM  | MAX   | UNIT  |

|----------------------|----------------------------------------------|---------------------------------------|-------|------|-------|-------|

| LR                   | Inductance of antenna $(d_{LR} = \pm 2.8\%)$ | 25°C CR = 470 pF, ±2% f= 134.2<br>kHz | 2.586 | 2.66 | 2.734 | mH    |

| d <sub>LR/LRdT</sub> | Temperature coefficient of LR                | –40 to 85°C                           |       |      | 250   | ppm/K |

| QLR <sup>(1)</sup>   | Quality factor of LR                         | 25°C* Qop > 30 <sup>(2) (1)</sup>     |       | 60   |       |       |

(1) Qop is Q factor measured when device is assembled on PCB.

(2) Due to tester limitations currently only the value given in brackets can be guaranteed.

## **RESONANCE CIRCUIT CAPACITOR**

|     | PARAMETER           | TEST CONDITIONS                      | MIN   | NOM | MAX   | UNIT |

|-----|---------------------|--------------------------------------|-------|-----|-------|------|

| CR  | Resonance capacitor | LR = 2.66 mH ± 2.8%                  | 460.6 | 470 | 479.4 | pF   |

|     | Dielectric          | $dLR/LRdt \le 250 \text{ ppm}^{(1)}$ |       | NP0 |       |      |

| QCR | Quality factor      |                                      | 2000  |     |       |      |

| RF  | Operating voltage   |                                      | 20    | 50  |       | Vpp  |

(1) This type is recommended, if no temperature compensation is required for LR

www.ti.com

## **CHARGE CAPACITOR**

| PARAMETER          |                              | TEST CONDITIONS                   | MIN | TYP | MAX | UNIT |

|--------------------|------------------------------|-----------------------------------|-----|-----|-----|------|

| CL                 | Charge capacitor             | 25°C<br>f <sub>meas</sub> = 1 kHz | 198 | 220 | 242 | nF   |

| C <sub>Ldiel</sub> | Dielectric of C <sub>L</sub> |                                   |     | X7R |     |      |

| V <sub>CL</sub>    | Operating voltage            |                                   | 16  |     |     | Vdc  |

## **OTHER COMPONENTS**

| PARAMETER         |                                 | TEST CONDITIONS                | MIN | NOM | MAX | UNIT |

|-------------------|---------------------------------|--------------------------------|-----|-----|-----|------|

| R <sub>VCL</sub>  | V <sub>CL</sub> resistor        | Depends on application circuit |     | 1   |     | MΩ   |

| R <sub>load</sub> | V <sub>BATI</sub> load resistor | Depends on application circuit |     | 100 |     | kΩ   |

| C <sub>BAT</sub>  | Battery capacitor               |                                |     | 100 |     | nF   |

| C <sub>BATI</sub> | BATI capacitor                  |                                |     | 100 |     | nF   |

## **RECOMMENDED TEST INTERFACE PARAMETERS**

|                                 | PAI                                       | RAMETER        | MIN                   | NOM | MAX                   | UNIT |

|---------------------------------|-------------------------------------------|----------------|-----------------------|-----|-----------------------|------|

| V <sub>CL</sub>                 | Supply voltage for trim/test              |                |                       | 5   |                       | V    |

| V <sub>IH</sub>                 | High level input voltage, TD              | AT, TCLK & TEN | 0.9 × V <sub>CL</sub> |     | 1.1 × V <sub>CL</sub> | V    |

| V <sub>IL</sub>                 | Low level input voltage, TDAT, TCLK & TEN |                | 0                     |     | $0.1 \times V_{CL}$   | V    |

| f <sub>Tclk</sub>               | Clock frequency                           | TCLK           |                       | 134 |                       | kHz  |

| t <sub>r</sub> , t <sub>f</sub> | Rise and fall time, TDAT, TO              |                | 50                    |     | ns                    |      |

| t <sub>Tclkl</sub>              | Test clock low time                       |                |                       | 3.7 |                       | μs   |

| t <sub>Tclkh</sub>              | Test clock high time                      |                |                       | 3.7 |                       | μs   |

| t <sub>Tres</sub>               | Test reset time                           |                |                       | 14  |                       | ms   |

| t <sub>Trc</sub>                | Test reset to clock time                  |                |                       | 1   |                       | μs   |

| t <sub>Tds</sub>                | Test data setup time                      |                |                       | 1   |                       | μs   |

| t <sub>Tdh</sub>                | Test data hold time                       |                |                       | 1   |                       | μs   |

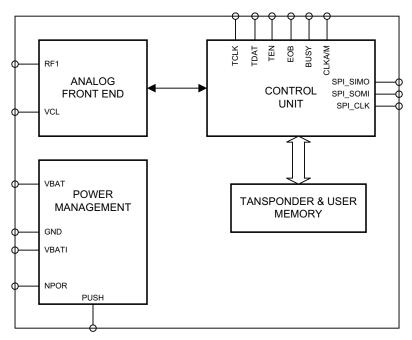

## TMS37157 BLOCK DIAGRAM

www.ti.com

## **BLOCK DESCRIPTION**

## Analog Front End

The Analog Front End implements all of the analog functions needed to support the TMS37157 transponder functions. It enables reception and transmission of LF signals when the transponder is active, and rectifies incoming LF energy and stores it in an external charge capacitor, to power the device.

The Analog Front End also contains the capacitor array used to trim the transponder's resonance circuit and a clock regenerator function, which is able to recover the clock from an incoming signal so it can be used by the transponder functions.

## **Control Unit**

#### **DST Transponder**

The transponder implemented in the TMS37157 is compatible with Texas Instruments' DST ("Digital Signature Transponder") transponder. In addition the TMS37157 provides additional Memory for customer use.

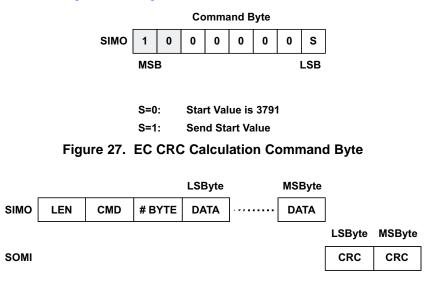

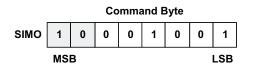

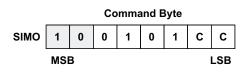

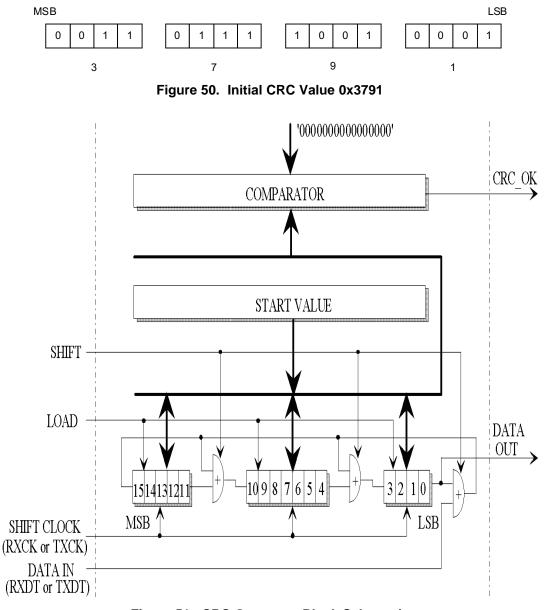

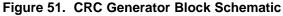

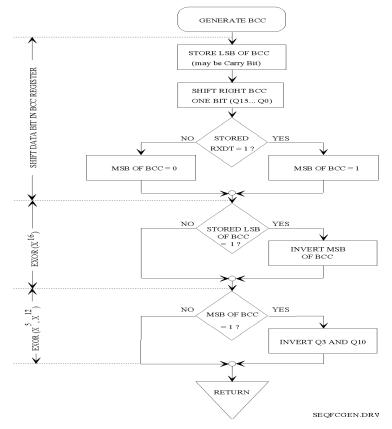

#### **CRC** Calculation

A hardware cyclic redudancy check calculation engine is implemented in the Control Unit to provide error detection.

#### Memory Access

The Control Unit interfaces to the on-chip EEPROM. During power-up, the Control Unit reads the configuration parameters stored in the EEPROM and initializes the TMS37157 circuitry accordingly, and at various times during device operation it can read EEPROM data and provide it, for example, to a microcontroller.

#### SPI Interface

The Control Unit provides an SPI interface that allows it to communicate with a microcontroller. Via this interface, for example, the microcontroller is able to access the contents of the TMS37157 EEPROM.

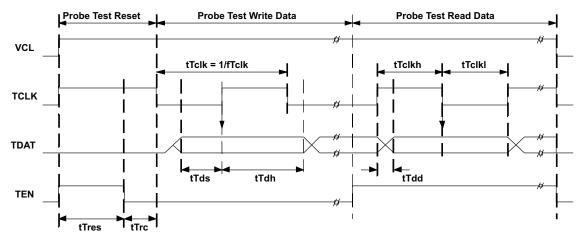

#### Test Interface

The Control Unit provides a test interface that allows customers to trim the LF antenna's resonance circuit.

#### **Transponder and User Memory**

The Transponder Memory comprises a total of 126 bytes, organized in pages. Memory space is apportioned as follows:

- User Data 121 bytes

- Serial Number + Manufactorer Code 4 bytes

- Selective Address 1 byte

Texas Instruments

www.ti.com

|                       | MSB             |                  |      |                | LSB     |

|-----------------------|-----------------|------------------|------|----------------|---------|

| SELECT. ADDRESS       | e.g<br>PASSWORD |                  |      |                | PAGE 1  |

| USER DATA             | DATA            |                  |      |                | PAGE 2  |

| UNIQUE IDENTIFICATION | LOCK            | SERIAL<br>NUMBER |      | MANUF.<br>CODE | PAGE 3  |

| USER DATA             | LOCK            |                  | DATA |                | PAGE 8  |

| USER DATA             | LOCK            |                  | DATA |                | PAGE 9  |

| USER DATA             | LOCK            |                  | DATA |                | PAGE 10 |

| USER DATA             | LOCK            |                  | DATA |                | PAGE 11 |

| USER DATA             | LOCK            |                  | DATA |                | PAGE 12 |

| USER DATA             | LOCK            |                  | DATA |                | PAGE 13 |

| USER DATA             | LOCK            |                  | DATA |                | PAGE 14 |

| USER DATA             | LOCK            |                  | DATA |                | PAGE 15 |

# TMS37157

SWRS083A-SEPTEMBER 2009-REVISED NOVEMBER 2009

|           | l     |   |     |    |    |                   |       |

|-----------|-------|---|-----|----|----|-------------------|-------|

|           | 1 MSB | 8 | 16  | 24 | 32 | <sub>40</sub> LSB |       |

| USER DATA | LOCK  |   | DAT | Ā  |    | PA                | GE 40 |

| USER DATA | LOCK  |   | DAT | Ā  |    | PA                | GE 41 |

| USER DATA | LOCK  |   | DAT | A  |    | PA                | GE 42 |

| USER DATA | LOCK  |   | DAT | Ā  |    | PA                | GE 43 |

| USER DATA | LOCK  |   | DAT | Ā  |    | PA                | GE 44 |

| USER DATA | LOCK  |   | DAT | Ā  |    | PA                | GE 45 |

| USER DATA | LOCK  |   | DAT | Ā  |    | PA                | GE 46 |

| USER DATA | LOCK  |   | DAT | Ā  |    | PA                | GE 47 |

| USER DATA | LOCK  |   | DAT | Ā  |    | PA                | GE 48 |

| USER DATA | LOCK  |   | DA  | TA |    | PA                | GE 49 |

| USER DATA | LOCK  |   | DA  | TA |    | PA                | GE 50 |

| USER DATA | LOCK  |   | DA  | TA |    | PA                | GE 51 |

| USER DATA | LOCK  |   | DAT | Ā  |    | PA                | GE 52 |

| USER DATA | LOCK  |   | DA  | ТА |    | PA                | GE 53 |

| USER DATA | LOCK  |   | DA  | ТА |    | PA                | GE 54 |

| USER DATA | LOCK  |   | DA  | TA |    | PA                | GE 55 |

#### Selective Address

Page 1 of the transponder memory contains a Selective Address (password) and lock bit. The Selective Address is used for selective programming, selective locking, selective protecting and selective reading.

The Selective Address may be programmed by the user via the program page 1 command (as long as the Selective Address lock bit is not set). The lock bit can be set by the user via the lock page 1 command. Once set, the lock bit cannot be reset.

To activate the selective addressing feature, the user must write a value other than 0xFF into page 1. If the Selective Address is not 0xFF, it is compared with the Selective Address received from the base station during a command write phase. If the Selective Address is 0xFF (the factory default), no such comparison is performed and selective addressing is disabled.

Copyright © 2009, Texas Instruments Incorporated

## TEXAS INSTRUMENTS

www.ti.com

www.ti.com

Whenever pages 1, 2 or 3 are accessed, the Selective Address (from page 1) is returned in the corresponding read phase, together with page 2 and the Manufacturer Code and Serial Number (from page 3). The status of the page 1 lock bit (1=locked) is only returned when page 1 is accessed.

### Page 2

Page 2 of the transponder memory contains 8 bits of user data and lock bit.

Page 2 is typically used for numbering keys in an application (e.g. the key number), it can also be used so save the value of the trim capacitor array or for anything else. It may be programmed by the user using the program page 2 command (as long as the lock bit is not set). The lock bit can be set by the user via the lock page 2 command. Once set, the lock bit cannot be reset.

Whenever pages 1, 2 or 3 are accessed, page 2 is returned in the corresponding read phase, together with the Selective Address (from page 1) and the Manufacturer Code and Serial Number (from page 3). The status of the page 2 lock bit (1=locked) is only returned when page 2 is accessed.

#### Unique Identification

Page 3 of the transponder memory contains an 8-bit Manufacturer Code and a 24-bit Serial Number. The Manufacturer Code and Serial Number are programmed and locked during manufacture and cannot be changed.

The Manufacturer Code is used to distinguish between different devices, the Manufacturer Code of the TMS37157 is 0x0E. The Serial Number is unique for every single TMS37157 device.

Whenever pages 1, 2 or 3 are accessed, the Manufacturer Code and Serial Number (from page 3) are returned in the corresponding read phase, together with the Selective Address (from page 1) and page 2. The status of the page 3 lock bit (1=locked) is only returned when page 3 is accessed.

#### User Data

The Transponder Memory provides the Pages 2, 8 to 15 and 40 to 55 for data storage. This memory is available to store any data defined by the user or application.

www.ti.com

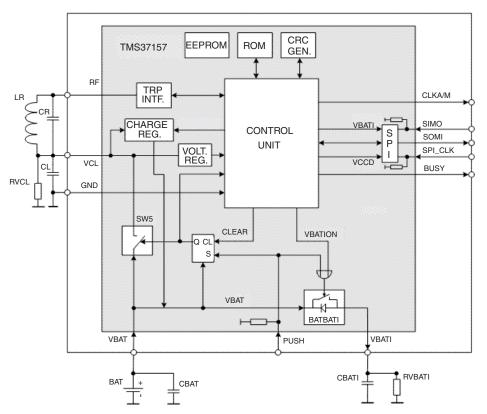

### POWER MANAGEMENT

The Power Management block is responsible for the master control of all power supplies plus several additional tasks, such as responding when a push button is pressed, generating reset signals and receiving LF transponder commands.

A block diagram of the power management function is shown in Figure 3. Activation of a push signal is detected by an ultra low-power detection circuit. While waiting for a high signal at PUSH, the only active component in theTMS73157 is a flip-flop, whose output is set when PUSH is set high. When this happens, SW5 is closed and the Control Unit is powered up and initialized. Also VBAT is switched to VBATI to power up a connected microcontroller. The Microcontroller can, after performing its desired actions, send a Power Down Command to the TMS37157, bringing the TMS37157 in the ultra low power mode (the Flip Flip is cleared and VBATI is disconnected waiting for a PUSH High signal to appear.

When the Transponder Interface receives an MSP Access Command the Control Unit is powered up and initialized and sets the VBATI ON signal, which switches on the uC. The Control Unit waits for  $\mu$ C to fetch the data, process it and send the processed data back to the Control Unit. The TMS37157 switches VBATI off and waits for the RF to switch. If it detects a loss of the RF is transmitts the MSP Access data back. Then the TMS37157 goes into the ultra low power sleep mode again. Throughout the whole MSP Access process the RF of the reader has to stay on, because the TMS37157 Control Unit is powered out of the RF - field.

Figure 3. TMS37157 Power Management

www.ti.com

## ADRESSING OF THE TRANSPONDER

The addressing mode of the TMS37157 is defined by the content of page 1.

General Addressing Page 1 = 0xFF

Selective Addressing Page 1 <> 0xFF

Standard configuration is General Addressing. Selective Addressing is activated by programming a value other than 0xFF into page 1 of the TMS37157 EEPROM. Selective Addressing affects the Lock Page, Protect Page (not available for Page 1-3) and Program Page commands for page 1 to page 15 and page 40 to page 55. Here the selective address has to be added to the Command. A Read Page of page 1 – 3 always gives back the selective address.

A General Read is still possible on all pages. For page 1 - 3 a selective read be can done.

To switch off Selective Addressing a selective program page 1 Command with User Data 0xFF has to be send to the TMS37157.

## USE OF THE LOCK BIT

All pages can be locked by setting the corresponding lock bit. Locked pages can not be reprogrammed anymore. The Lock is irreversible.

## **USE OF THE PROTECTION BIT**

Pages 8-15 and 40-55 can be protected by setting the corresponding Protection Bit. Protected pages can only be repgrammed via SPI. The TMS37157 will not answer to a program command on a protected page. General and Selective Read commands are still possible on protected pages. The protection is irreversible.

www.ti.com

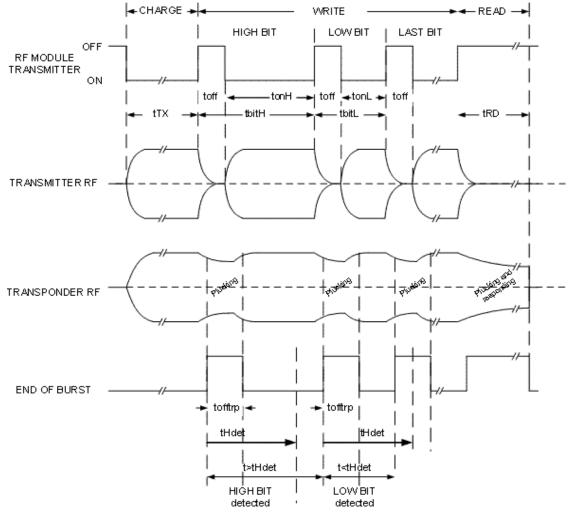

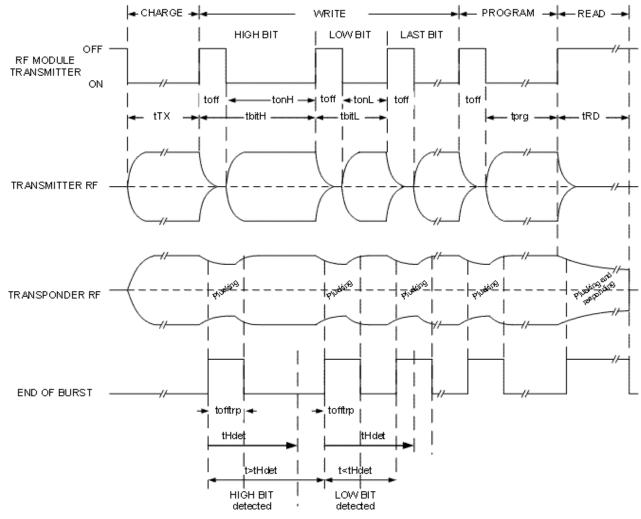

### PULSE POSITION MODULATION

With Pulse Position Modulation the information is carried in the period duration of a bit ( $t_{bitL}$ ,  $t_{bitH}$ ). A bit consists of a pulse pause ( $t_{off}$ ) and a pulse activation ( $t_{onL}$ ,  $t_{onH}$ ).

The difference of period durations at the reader must be selected in way that in case of a low bit the duration at the transponder location is lower than the High Bit Threshold Detection Time ( $t_{Hdet}$ ). For a high bit, the bit duration must at the transponder location must be higher that the High Bit Threshold Detection Time ( $t_{Hdet}$ ).

#### PPM in Case of General Read

Figure 4. PPM in Case of General Read

If the Pause between to positive transitions of EOB is at least as long as tHdet the Transponder writes a one. Is the Pause shorter it writes a 0.

www.ti.com

Figure 5. PPM in Case of Programming

For a program, lock or protect command a RF burst from the transmitter is needed after transmitting the program, lock or protect command, the length has to be at least tprg.

www.ti.com

### TMS37157 COMMANDS

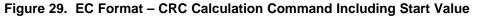

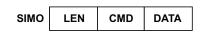

This chapter describes the commands and data that can be transferred to and from the TMS37157 via its contact less LF interface, SPI and Test interfaces.

When communicating with the transponder following naming conventions are used:

- Data Transmission from the base station to the transponder is called "write" and "write data are transferred".

- Data Transmission from the transponder to the base station is called "read" and "read data re transferred".

This is applied independently from the command that is executes whether it is a read, write, program or authentication function.

#### Write Formats

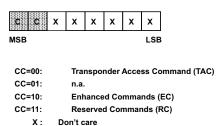

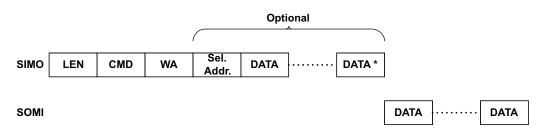

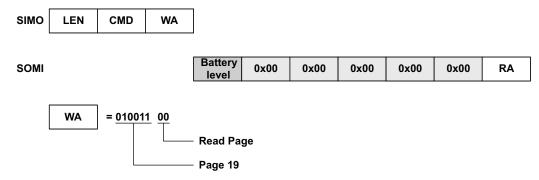

In order to send commands to the TMS37157 LF interface, the user sends a Write Address byte comprising a 2-bit Command field and a 6-bit Page field. The Command field, which is transmitted first, determines the function to be executed and whether command comprises additional data bytes that must also be sent. The Page field specifies the target of the command.

Table 1 shows which additional data bytes must be included with each command type. The elements for each command are sent from left to the right of this table.

|                                  |               | •          |           |                  |           |  |

|----------------------------------|---------------|------------|-----------|------------------|-----------|--|

| FUNCTION                         | WRITE AD      | DRESS      | SELECTIVE |                  | FRAME BCC |  |

| FUNCTION                         | COMMAND FIELD | PAGE FIELD | ADDRESS   | WRITE DATA       | FRAME BCC |  |

|                                  | MSB LSB       |            |           |                  |           |  |

| General read page, battery check | 00            | Х          |           |                  |           |  |

| Selective read page              | 11            | Х          | Х         |                  | Х         |  |

| Program page; MSP access         | 01            | Х          |           | X <sup>(1)</sup> | Х         |  |

| Selective program page           | 01            | Х          | Х         | X <sup>(1)</sup> | Х         |  |

| Lock page                        | 10            | Х          |           |                  | Х         |  |

| Selective lock page              | 10            | Х          | Х         |                  | Х         |  |

| Protect page                     | 11            | Х          |           |                  | Х         |  |

| Selective protect page           | 11            | Х          | Х         |                  | Х         |  |

#### Table 1. Data Bytes for different command types

(1) Length of Wrtite Data is 5 bytes for a program page command and 6 bytes for an MSP Access command.

The summary for the available write address via the LF interface are shown in Table 2. It shows the valid Command and Page field combinations supported by the TMS37157.

#### Table 2. Valid Command and Page Field Combinations (Command)

|        | WRITE A                                    | DDRESS                                         |              |                                  |

|--------|--------------------------------------------|------------------------------------------------|--------------|----------------------------------|

|        | MSB<br>PPPPP<br> <br>PAGE FIELD<br>MSB LSB | LSB<br>C C<br> <br>COMMAND<br>FIELD<br>MSB LSB | HEX<br>VALUE |                                  |

| Page 1 | 000001                                     | 00                                             | 04h          | General Read Page 1              |

|        | 000001                                     | 01                                             | 05h          | Program/Selective Program Page 1 |

|        | 000001                                     | 10                                             | 06h          | Lock/Selective Lock Page 1       |

|        | 000001                                     | 11                                             | 07h          | Selective Read Page 1            |

| Page 2 | 000010                                     | 00                                             | 08h          | General Read Page 2              |

|        | 000010                                     | 01                                             | 09h          | Program/Selective Program Page 2 |

|        | 000010                                     | 10                                             | 0Ah          | Lock/Selective Lock Page 2       |

|        | 000010                                     | 11                                             | 0Bh          | Selective Read Page 2            |

Copyright © 2009, Texas Instruments Incorporated

| Page 3  | 000011 | 00 | 0Ch | General Read Page 3                                         |

|---------|--------|----|-----|-------------------------------------------------------------|

|         | 000011 | 01 | 0Dh | Program/Selective Program Page 3                            |

|         | 000011 | 10 | 0Eh | Lock/Selective Lock Page 3                                  |

|         | 000011 | 11 | 0Fh | Selective Read Page 3                                       |

| Page 8  | 001000 | 00 | 20h | General Read Page 8                                         |

|         | 001000 | 01 | 21h | Program/Selective Program Page 8                            |

|         | 001000 | 10 | 22h | Lock/Selective Lock Page 8                                  |

|         | 001000 | 11 | 23h | Set Protection Bit/ Selective Set Protection Bit of Page 8  |

| Page 9  | 001001 | 00 | 24h | General Read Page 9                                         |

|         | 001001 | 01 | 25h | Program/Selective Program Page 9                            |

|         | 001001 | 10 | 26h | Lock/Selective Lock Page 9                                  |

|         | 001001 | 11 | 27h | Set Protection Bit/ Selective Set Protection Bit of Page 9  |

| Page 10 | 001010 | 00 | 28h | General Read Page 10                                        |

| 0       | 001010 | 01 | 29h | Program/Selective Program Page 10                           |

|         | 001010 | 10 | 2Ah | Lock/Selective Lock Page 10                                 |

|         | 001010 | 11 | 2Bh | Set Protection Bit/ Selective Set Protection Bit of Page 10 |

| Page 11 | 001011 | 00 | 2Ch | General Read Page 11                                        |

|         | 001011 | 01 | 2Dh | Program/Selective Program Page 11                           |

|         | 001011 | 10 | 2Eh | Lock/Selective Lock Page 11                                 |

|         | 001011 | 10 | 2Fh | Set Protection Bit/ Selective Set Protection Bit of Page 11 |

| Page 12 | 001100 | 00 | 30h | General Read Page 12                                        |

| Tuge T2 | 001100 | 01 | 31h | Program/ Selective Program Page 12                          |

|         | 001100 | 10 | 32h | Lock/ Selective Lock Page 12                                |

|         | 001100 | 10 | 32h | Set Protection Bit/ Selective Set Protection Bit of Page 12 |

| Da 40   |        |    |     |                                                             |

| Page 13 | 001101 | 00 | 34h | General Read Page 13                                        |

|         | 001101 | 01 | 35h | Program/ Selective Program Page 13                          |

|         | 001101 | 10 | 36h | Lock/ Selective Lock Page 13                                |

|         | 001101 | 11 | 37h | Set Protection Bit/ Selective Set Protection Bit of Page 13 |

| Page 14 | 001110 | 00 | 28h | General Read Page 14                                        |

|         | 001110 | 01 | 39h | Program/ Selective Program Page 14                          |

|         | 001110 | 10 | 3Ah | Lock/ Selective Lock Page 14                                |

|         | 001110 | 11 | 3Bh | Set Protection Bit/ Selective Set Protection Bit of Page 14 |

| Page 15 | 001111 | 00 | 3Ch | General Read Page 15                                        |

|         | 001111 | 01 | 3Dh | Program/ Selective Page 15                                  |

|         | 001111 | 11 | 3Eh | Lock/ Selective Lock Page 15                                |

|         | 001111 | 11 | 3Fh | Set Protection Bit/ Selective Set Protection Bit of Page 15 |

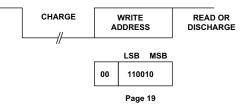

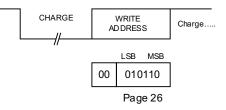

| Page 19 | 010011 | 00 | 4Ch | Battery Check                                               |

| Page 26 | 011010 | 00 | 68h | Battery Charge <sup>(1)</sup>                               |

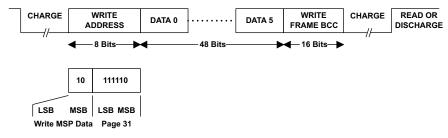

| Page 31 | 011111 | 01 | 7Dh | MSP Access (Program Page 31)                                |

| Page 40 | 101000 | 00 | A0h | General Read Page 40                                        |

|         | 101000 | 01 | A1h | Program/ Selective Program Page 40                          |

|         |        |    |     |                                                             |

(1) The TMS37157 will not respond to a Battery Charge Command. The RF has to stay on after transmitting the Write Address. To end the battery charge command any other command can be performed.

www.ti.com

# TMS37157

www.ti.com

SWRS083A-SEPTEMBER 2009-REVISED NOVEMBER 2009

## Table 2. Valid Command and Page Field Combinations (Command) (continued)

WRITE ADDRESS

|         | WRITE A | ADDRESS |     |                                                             |

|---------|---------|---------|-----|-------------------------------------------------------------|

|         | 101000  | 10      | A2h | Lock/ Selective Lock Page 40                                |

|         | 101000  | 11      | A3h | Set Protection Bit/ Selective Set Protection Bit of Page 44 |

| Page 41 | 101001  | 00      | A4h | General Read Page 41                                        |

|         | 101001  | 01      | A5h | Program/ Selective Program Page 41                          |

|         | 101001  | 10      | A6h | Lock/ Selective Lock Page 41                                |

|         | 101001  | 11      | A7h | Set Protection Bit/ Selective Set Protection Bit of Page 41 |

| Page 42 | 101010  | 00      | A8h | General Read Page 42                                        |

|         | 101010  | 01      | A0h | Program/ Selective Program Page 42                          |

|         | 101010  | 10      | AAh | Lock/ Selective Lock Page 42                                |

|         | 101010  | 11      | ABh | Set Protection Bit/ Selective Set Protection Bit of Page 42 |

| Page 43 | 101011  | 00      | ACh | General Read Page 43                                        |

|         | 101011  | 01      | ADh | Program/ Selective Program Page 43                          |

|         | 101011  | 10      | AEh | Lock/ Selective Lock Page 43                                |

|         | 101011  | 11      | AFh | Set Protection Bit/ Selective Set Protection Bit of Page 43 |

| Page 44 | 101100  | 00      | B0h | General Read Page 44                                        |

|         | 101100  | 01      | B1h | Program/ Selective Program Page 44                          |

|         | 101100  | 10      | B2h | Lock/ Selective Lock Page 44                                |

|         | 101100  | 11      | B3h | Set Protection Bit/ Selective Set Protection Bit of Page 44 |

| Page 45 | 101101  | 00      | B4h | General Read Page 45                                        |

|         | 101101  | 01      | B5h | Program/ Selective Program Page 45                          |

|         | 101101  | 10      | B6h | Lock/ Selective Lock Page 45                                |

|         | 101101  | 11      | B7h | Set Protection Bit/ Selective Set Protection Bit of Page 45 |

| Page 46 | 101110  | 00      | B8h | General Read Page 46                                        |

|         | 101110  | 01      | B9h | Program/ Selective Program Page 46                          |

|         | 101110  | 10      | BAh | Lock/ Selective Lock Page 46                                |

|         | 101110  | 11      | BBh | Set Protection Bit/ Selective Set Protection Bit of Page 46 |

| Page 47 | 101111  | 00      | BCh | General Read Page 47                                        |

|         | 101111  | 01      | BDh | Program/ Selective Program Page 47                          |

|         | 101111  | 10      | BEh | Lock/ Selective Lock Page 47                                |

|         | 101111  | 11      | BFh | Set Protection Bit/ Selective Set Protection Bit of Page 47 |

| Page 48 | 110000  | 00      | C0h | General Read Page 48                                        |

|         | 110000  | 01      | C1h | Program/ Selective Program Page 48                          |

|         | 110000  | 10      | C2h | Lock/ Selective Lock Page 48                                |

|         | 110000  | 11      | C3h | Set Protection Bit/ Selective Set Protection Bit of Page 48 |

| Page 49 | 110001  | 00      | C4h | General Read Page 49                                        |

|         | 110001  | 01      | C5h | Program/ Selective Program Page 49                          |

|         | 110001  | 10      | C6h | Lock/ Selective Lock Page 49                                |

|         | 110001  | 11      | C7h | Set Protection Bit/ Selective Set Protection Bit of Page 49 |

| Page 50 | 110010  | 00      | C8h | General Read Page 50                                        |

|         | 110010  | 01      | C9h | Program/ Selective Program Page 50                          |

|         | 110010  | 10      | CAh | Lock/ Selective Lock Page 50                                |

|         | 110010  | 11      | CBh | Set Protection Bit/ Selective Set Protection Bit of Page 50 |

| Page 51 | 110011  | 00      | CCh | General Read Page 51                                        |

|         |         |         |     |                                                             |

www.ti.com

## Table 2. Valid Command and Page Field Combinations (Command) (continued)

|         | WRITE AI | DDRESS |     |                                                             |

|---------|----------|--------|-----|-------------------------------------------------------------|

|         | 110011   | 01     | CDh | Program/ Selective Program Page 51                          |

|         | 110011   | 10     | CEh | Lock/ Selective Lock Page 51                                |

|         | 110011   | 11     | CFh | Set Protection Bit/ Selective Set Protection Bit of Page 51 |

| Page 52 | 110100   | 00     | D0h | General Read Page 52                                        |

|         | 110100   | 01     | D1h | Program/ Selective Program Page 52                          |

|         | 110100   | 10     | D2h | Lock/ Selective Lock Page 52                                |

|         | 110100   | 11     | D3h | Set Protection Bit/ Selective Set Protection Bit of Page 52 |

| Page 53 | 110101   | 00     | D4h | General Read Page 53                                        |

|         | 110101   | 01     | D5h | Program/ Selective Program Page 53                          |

|         | 110101   | 10     | D6h | Lock/ Selective Lock Page 53                                |

|         | 110101   | 11     | D7h | Set Protection Bit/ Selective Set Protection Bit of Page 53 |

| Page 54 | 110110   | 00     | D8h | Lock/ Selective Lock Page 54                                |

|         | 110110   | 01     | D9h | Program/Selective Page 54                                   |

|         | 110110   | 10     | DAh | Lock/Selective Lock Page 54                                 |

|         | 110110   | 11     | DBh | Set Protection Bit/ Selective Set Protection Bit of Page 54 |

| Page 55 | 110111   | 00     | DCh | General Read Page 55                                        |

|         | 110111   | 01     | DDh | Program/Selective Page 55                                   |

|         | 110111   | 10     | DEh | Lock/Selective Lock Page 55                                 |

|         | 110111   | 11     | DFh | Set Protection Bit/ Selective Set Protection Bit of Page 55 |

## **Read Formats**

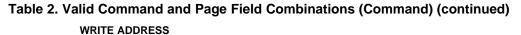

The Read phase starts with each deactivation of the transmitter, which is detected by the transponder, because the transponder resonance circuit RF amplitude drops. The transponder starts with transmission of 16 Pre-bits. During this phase the resonance circuit resonates with the low bit transmit frequency ( $f_L$ ). During transmission of the read data or response, the resonance circuit frequency is shifted between the low bit transmit frequency ( $f_L$ ) and the high bit transmit frequency ( $f_H$ ).

The typical data low bit frequency is 134.7 kHz; the typical data high bit frequency is 123.7 kHz. The low and high bits have different durations, because each bit takes 16 RF cycles to transmit.

Figure 6 shows the FM principle used. Regardless of the number of low and high bits, the transponder response duration is always less than 15 ms.

Data encoding is done in NRZ mode (Non Return to Zero). The clock is derived from the RF carrier by a divide-by-16 function.

After a charge phase only, having no write phase, the transponder discharges its capacitor at the end of the pre-bit phase, which results in no response. If a valid function was detected during the write phase, the complete read data format is transmitted. The content of the read data format depends on the previously executed function.

When the last bit has been sent, the capacitor is discharged. During discharge no charge-up is possible.

A sufficiently long read time  $(t_{RD})$  must be provided to ensure that the complete read data format can be received.

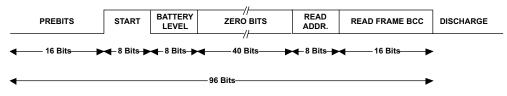

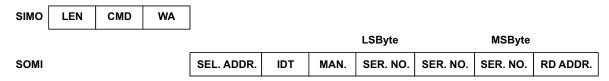

During the response (read) phase, the transponder transmits 96 bits of data, formatted as described below. The content of the response depends on which page was addressed.

All read data starts with a 16-bit preamble followed by an 8-bit start byte (7Eh), and ends with the 8-bit Read Address and 16-bit Read Frame BCC. All parts of the read data are transmitted LSB first.

The Read Address byte comprises a 2-bit Status field, which is transmitted first and contains status information, and a 6-bit Page field, which contains page and additional status information. The contents of the Status field depend on which page is being addressed.

|      | READ DATA FORMAT BYTE |            |           |            |            |            |  |  |  |  |

|------|-----------------------|------------|-----------|------------|------------|------------|--|--|--|--|

| Page | 4                     | 5          | 6         | 7          | 8          | 9          |  |  |  |  |

| 1    | Sel. Address          | Page 2     | Man. Code | Serial No. | Serial No. | Serial No. |  |  |  |  |

| 2    | Sel. Address          | Page 2     | Man. Code | Serial No. | Serial No. | Serial No. |  |  |  |  |

| 3    | Sel. Address          | Page 2     | Man. Code | Serial No. | Serial No. | Serial No. |  |  |  |  |

| 8    | Page 2                | Page 8     | Page 8    | Page 8     | Page 8     | Page 8     |  |  |  |  |

| 9    | Page 2                | Page 9     | Page 9    | Page 9     | Page 9     | Page 9     |  |  |  |  |

| 10   | Page 2                | Page 10    | Page 10   | Page 10    | Page 10    | Page 10    |  |  |  |  |

| 11   | Page 2                | Page 11    | Page 11   | Page 11    | Page 11    | Page 11    |  |  |  |  |

| 12   | Page 2                | Page 12    | Page 12   | Page 12    | Page 12    | Page 12    |  |  |  |  |

| 13   | Page 2                | Page 13    | Page 13   | Page 13    | Page 13    | Page 13    |  |  |  |  |

| 14   | Page 2                | Page 14    | Page 14   | Page 14    | Page 14    | Page 14    |  |  |  |  |

| 15   | Page 2                | Page 15    | Page 14   | Page 14    | Page 14    | Page 14    |  |  |  |  |

| 19   | Battery level         | '00000000' | '0000000' | '0000000'  | '0000000'  | '00000000' |  |  |  |  |

| 31   | MSP Data              | MSP Data   | MSP Data  | MSP Data   | MSP Data   | MSP Data   |  |  |  |  |

| 40   | Page 2                | Page 40    | Page 40   | Page 40    | Page 40    | Page 40    |  |  |  |  |

| 41   | Page 2                | Page 41    | Page 41   | Page 41    | Page 41    | Page 41    |  |  |  |  |

| 42   | Page 2                | Page 42    | Page 42   | Page 42    | Page 42    | Page 42    |  |  |  |  |

| 43   | Page 2                | Page 43    | Page 43   | Page 43    | Page 43    | Page 43    |  |  |  |  |

| 44   | Page 2                | Page 44    | Page 44   | Page 44    | Page 44    | Page 44    |  |  |  |  |

| 45   | Page 2                | Page 45    | Page 45   | Page 45    | Page 45    | Page 45    |  |  |  |  |

| 46   | Page 2                | Page 46    | Page 46   | Page 46    | Page 46    | Page 46    |  |  |  |  |

| 47   | Page 2                | Page 47    | Page 47   | Page 47    | Page 47    | Page 47    |  |  |  |  |

| 48   | Page 2                | Page 48    | Page 48   | Page 48    | Page 48    | Page 48    |  |  |  |  |

| 49   | Page 2                | Page 49    | Page 49   | Page 49    | Page 49    | Page 49    |  |  |  |  |

| 50   | Page 2                | Page 50    | Page 50   | Page 50    | Page 50    | Page 50    |  |  |  |  |

| 51   | Page 2                | Page 51    | Page 51   | Page 51    | Page 51    | Page 51    |  |  |  |  |

| 52   | Page 2                | Page 52    | Page 52   | Page 52    | Page 52    | Page 52    |  |  |  |  |

| 53   | Page 2                | Page 53    | Page 53   | Page 53    | Page 53    | Page 53    |  |  |  |  |

| 54   | Page 2                | Page 54    | Page 54   | Page 54    | Page 54    | Page 54    |  |  |  |  |

| 55   | Page 2                | Page 55    | Page 55   | Page 55    | Page 55    | Page 55    |  |  |  |  |

#### Table 3. Overview of Read Data Format Content

Table 4 to Table 5 show the valid Status and Page field combinations supported by the TMS37157.

| READ                       | ER        |       | TRANSPONDER  |    |                                                                          |  |

|----------------------------|-----------|-------|--------------|----|--------------------------------------------------------------------------|--|

| Write Function             | Write Add | dress | Read Address |    | Valid Responses                                                          |  |

| General Read Page 1 to 3   | 000001    | 00    | 000001       | 00 | Read unlocked Page 13                                                    |  |

|                            | 000011    |       | 000011       | 10 | Read locked Page 13                                                      |  |

| Selective Read Page 1 to 3 | 000001    | 11    | 000001       | 00 | Read unlocked Page 13                                                    |  |

|                            | 000011    |       | 000011       | 10 | Read locked Page 13                                                      |  |

| Program/Selective Program  | 000001    | 01    | 000001       | 01 | Programming done on Page 13                                              |  |

| Page 1 to 3                | 000011    |       |              | 10 | Read locked Page 13 programming not executed                             |  |

|                            | 000011    |       | 000011       | 00 | Read unlocked Page 13, programming not executed (field strength too low) |  |

|                            |           |       | 000000       | 01 | Programming Page 13 done, but possibly not reliable                      |  |

| Lock / Selective Lock      | 000001    | 10    | 000001       | 10 | Read locked Page 13                                                      |  |

| Page 1 to 3                | 000011    |       | 000011       | 00 | Read unlocked Page 13, locking not execute (field strength too low)      |  |

|                            |           |       | 000000       | 00 | Read unlocked Page 13, locking not correctly executed                    |  |

|                            |           |       |              | 10 | Read locked Page 13, but locking possibly not reliable                   |  |

## Table 4. Valid Responses, If Page 1 to 3 is Addressed

## Table 5. Valid Responses, if Page 8 to 15 is Addressed

| READER                                         |               |        | TRANSPONDER  |                                                                             |                                                                           |  |

|------------------------------------------------|---------------|--------|--------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------|--|

|                                                |               |        | Read Address |                                                                             | Dessible Despenses                                                        |  |

| Write Function                                 | Write Address |        | Read Address |                                                                             | Possible Responses                                                        |  |

| General Read Page 815                          | 001000        | 00     | 001000       | 00                                                                          | Read unlocked Page 815                                                    |  |

|                                                | 001111        |        | 001111       | 10                                                                          | Read locked Page 815                                                      |  |

| Program/ Sel. Program                          | 001000        | 01     | 001000       | 01                                                                          | Page 815 is locked, programming not executed                              |  |

| Page 815                                       |               |        |              | 10                                                                          | Page 4055 is locked, programming not executed                             |  |

|                                                | 001111        |        | 001111       | 00                                                                          | Page 815 is unlocked, programming not executed (field strength too low)   |  |

|                                                |               |        | 0000000      | 01                                                                          | Programming Page 815 done, but possibly not reliable                      |  |

| Lock/ Selective Lock                           | 001000        | 10     | 001000       | 10                                                                          | Read locked Page 815                                                      |  |

| Page 815                                       | 001111        |        | 001111       | 00                                                                          | Read unlocked Page 815, locking not executed (field strength too low)     |  |

|                                                |               |        | 0000000      | 00                                                                          | Read unlocked Page 815, locking not correctly executed                    |  |

|                                                |               |        |              | 10                                                                          | Read locked Page 815, but locking possibly not reliable                   |  |

| Set/ Selective Set Protection 001000 11<br>Bit |               | 001000 | 00           | Read unlocked Page 815, Protection bit was not set (field strength too low) |                                                                           |  |

| Page 8…15                                      | 001111        |        | 001111       | 10                                                                          | Read locked Page 815, Protection bit was not set (field strength too low) |  |

|                                                |               |        |              | 11                                                                          | Protection Bit of Page 815 was set                                        |  |

|                                                |               |        | 0000000      | 11                                                                          | Setting of Protection bit was executed, but possibly not reliable         |  |

www.ti.com

Table 6. Valid Responses, If Battery Check (Page 19) is Addressed

| REA                             |           | TRANSPONDER |              |    |                       |

|---------------------------------|-----------|-------------|--------------|----|-----------------------|

| Write Function                  | Write Add | ress        | Read Address |    | Valid Responses       |

| Read Page 19<br>(Battery Check) | 010011    | 00          | 010011       | 00 | Read unlocked Page 19 |

#### Table 7. Valid Responses if MSP Access (Page 31) is Addressed

| READER          |               |    | TRANSPONDER  |    |                             |

|-----------------|---------------|----|--------------|----|-----------------------------|

| Write Function  | Write Address |    | Read Address |    | Possible Responses          |

|                 | 011111        | 01 | 011111       | 01 | MSP Access execution O.K.   |

| Program Page 31 |               |    |              | 00 | SPI Programming failed      |

| (MSP Access)    |               |    | 000000       | 00 | MSP Access execution failed |

|                 |               |    |              | 01 | MSP Access execution failed |

#### Table 8. Valid Responses, if Page 40 to 55 is Addressed

| READER                               |                      |    | TRANSPONDER  |    |                                                                              |  |

|--------------------------------------|----------------------|----|--------------|----|------------------------------------------------------------------------------|--|

| Write Function                       | Write Address        |    | Read Address |    | Possible Responses                                                           |  |

| General Read Page                    | 101000               | 00 | 101000       | 00 | Read / unlocked Page 4055                                                    |  |

| 4055                                 | 110110               |    | 110110       | 10 | Read / locked Page 4055                                                      |  |

| Program/ Sel. Program                | 101000               | 01 | 101000       | 01 | Programming done on Page 4055                                                |  |

| Page 4055                            |                      |    |              | 10 | Page 4055 is locked, programming not executed                                |  |

|                                      |                      |    |              | 00 | Page 4055 is unlocked, programming not executed (field strength too low)     |  |

|                                      |                      |    | 0            | 01 | Programming Page 4055 done, but possibly not reliable                        |  |

| Lock/ Selective Lock<br>Page 4055    | 101000<br><br>110110 | 10 | 101000       | 10 | Read locked Page 4055                                                        |  |

|                                      |                      |    | 110110       | 00 | Read unlocked Page 4055, locking not executed (field strength too low)       |  |

|                                      |                      |    | 0000000      | 00 | Read unlocked Page 4055, locking not correctly executed                      |  |

|                                      |                      |    |              | 10 | Read locked Page 4055, but locking possibly not reliable                     |  |

| Set/ Selective Set<br>Protection Bit | 101000               | 11 | 101000       | 00 | Read unlocked Page 4055, Protection bit was not set (field strength too low) |  |

| Page 4055                            | 110110               |    | 110110       | 10 | Read locked Page 4055, Protection bit was not set (field strength too low)   |  |

|                                      |                      |    |              | 11 | Protection Bit of Page 4055 was set                                          |  |

|                                      |                      |    | 000000       | 11 | Setting of Protection bit was executed, but possibly not reliable            |  |

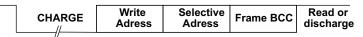

# LF TELEGRAMS – MEMORY ACCESS

Following sections show the structure of the Write - and Read Formats for the Memory Access through the Low Frequency Interface.

# Write to Transponder

## **Read Commands**

The write format of the General Read command is shown in Figure 7.

|   | CHARGE | Write<br>Adress | Read or<br>discharge |

|---|--------|-----------------|----------------------|

| _ | //     |                 | -                    |

## Figure 7. General Read/Get Status Command

The write format of the Selective Read command is shown in Figure 8.

Figure 8. Selective Read

## **Program Commands**

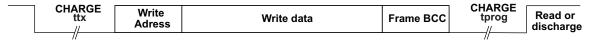

The write format of the general program command is shown in Figure 9.

Figure 9. General Program Command

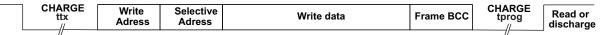

The write format of the selective program command is shown in Figure 10.

## Figure 10. Selective Program Command

## Lock and Protect Commands

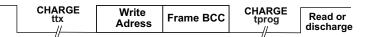

The write format of the Lock/Protect command is shown in Figure 11.

Figure 11. General Lock/Protect

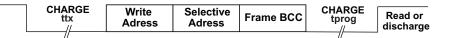

The write format of the Selective Lock/Protect command is shown in Figure 12.

Figure 12. Selective Lock/Protect

Lock and Protect commands share the same write format.

#### www.ti.com

#### Read From Transponder (Response)

The write format of the General Read command is shown in Figure 7.

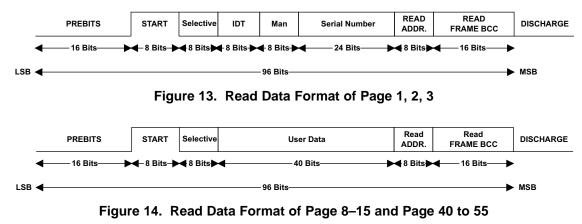

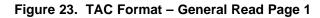

Transponder Response Format of the General Read command is shown in Figure 13 and Figure 14. The Response Format is the same for Read, Program and Lock Commands.

# LF TELEGRAMS – SPECIAL FUNCTION

## **MSP** Access

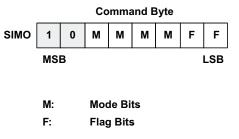

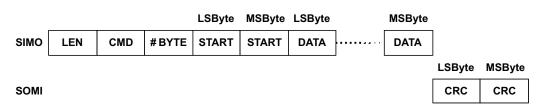

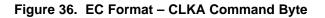

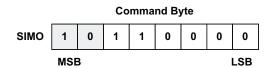

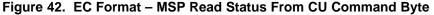

The MSP Access command allows transfer of LF data to and from the MSP 430 microcontroller via the TMS37157 Analog Front End. The microcontroller handles data transfers using the following SPI commands:

- MSP Read Data From PCU (Data In)

- MSP Write Data To PCU (Data Out)

## Write Data Format

The write format of the MSP Access command is shown in Figure 15.

Figure 15. LF Write Format – MSP Access Command

### **Read Data Format**

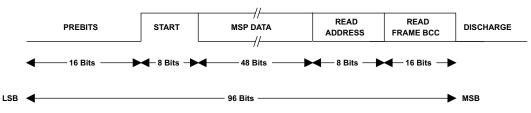

The read format of the MSP Access command is shown in .

## Flow of MSP Access Data Handling

The following sequence is needed to implement an MSP Access command:

- The TMS37157 detects that an MSP Access command has been received and wakes the Microcontroller (e.g. MSP430).