**TPS51363**

SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

# 22-V Input, 8-A or 10-A Converter

With Integrated FET

Check for Samples: TPS51363

## FEATURES

www.ti.com

- Input Voltage Range: 3 V to 22 V

- Output Voltage Range: 0.6 V to 2 V

- 8-A or 10-A Integrated FET Converter (see Table 1)

- Fewest External Components

- Soft-Start Time Programmable by External Capacitor

- Switching Frequency: 400 kHz and 800 kHz

- D-CAP2<sup>™</sup> Architecture to Enable POSCAP and All MLCC Output Capacitor Usage

- Integrated and Temperature Compensated Low-Side On-Resistance Sensing for Accurate OCL Protection

- Powergood Output OCL, OVP, UVP and UVLO Protections

- Thermal Shutdown (non-latch)

- Output Discharge Function

- Integrated Boost MOSFET Switch

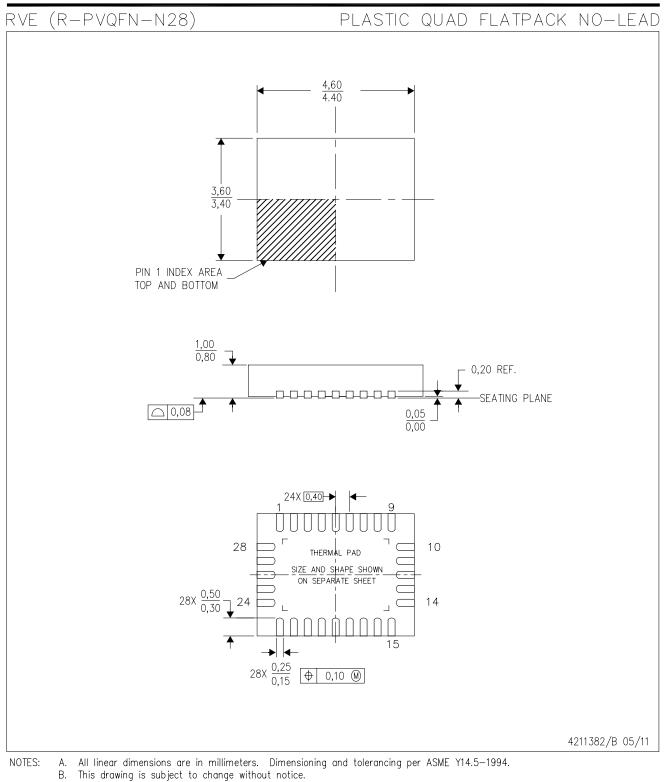

- 28-Pin, 3.5-mm × 4.5-mm, RVE, QFN Package with 0.4-mm Pitch and 1-mm Height

# APPLICATIONS

- Notebook Computers (VCCIO)

- Memory Rails (DDR VDDQ)

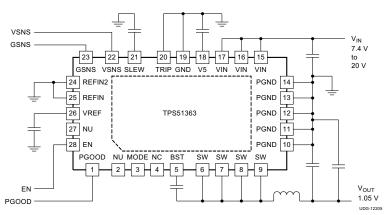

## SIMPLIFIED APPLICATION

## DESCRIPTION

The TPS51363 is a high-voltage input, synchronous converter with integrated FET, based on D-CAP2<sup>™</sup> control topology, which enables fast transient response and supports both POSCAP and all MLCC output capacitors. TI proprietary FET technology combined with TI leading-edge package technology provides the highest density solution for single-output power rail such as VCCIO and VDDQ for DDR notebook memory, or any point-of-load (POL) in wide application.

The feature set includes switching frequency of 400 kHz and 800 kHz. Programmable soft-start time with an external capacitor. auto skip, pre-bias startup, integrated bootstrap switch, power good, enable and a full suite of fault protection schemes, including OCL, UVP, OVP, 5-V UVLO and thermal shutdown.

It is packaged in 3.5 mm × 4.5 mm, 0.4-mm pitch, 28pin QFN (RVE), and specified from -10°C to 85°C.

#### Table 1. Current Ratings

| FREQUENCY SETTING | MAX I <sub>DC</sub> |

|-------------------|---------------------|

| 800 kHz           | 8 A                 |

| 400 kHz           | 10 A                |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. D-CAP2 is a trademark of Texas Instruments.

# TPS51363

#### SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

Texas Instruments

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**<sup>(1)</sup> <sup>(2)</sup>

| T <sub>A</sub> | PACKAGE                      | ORDERABLE DEVICE<br>NUMBER | PINS | TRANSPORT MEDIA     | MINIMUM<br>ORDER<br>QUANTITY |

|----------------|------------------------------|----------------------------|------|---------------------|------------------------------|

| –10°C to 85°C  | Plastic Quad Flat Pack (QEN) | TPS51363RVET               | 20   | Small tape-and-reel | 250                          |

| -10°C 10 85°C  | Plastic Quad Flat Pack (QFN) | TPS51363RVER               | 28   | Large tape-and-reel | 3000                         |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or visit the TI website at www.ti.com.

(2) Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                                                                                  |                                            |                                                  | VALU  | E    | UNIT |

|----------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------|-------|------|------|

|                                                                                  |                                            |                                                  | MIN   | MAX  |      |

|                                                                                  | VIN                                        |                                                  | -0.3  | 30   |      |

|                                                                                  |                                            |                                                  |       | 36   |      |

|                                                                                  | BST                                        | transient <10 ns                                 |       | 38   |      |

|                                                                                  |                                            | w/r/t SW                                         |       | 6    |      |

| Input voltage range <sup>(2)</sup>                                               | SW                                         |                                                  |       | 30   | V    |

|                                                                                  | EN, TRI                                    | P, NU, MODE, V5                                  | -0.3  | 6    |      |

|                                                                                  | SLEW, VSNS, REFIN, REFIN2                  |                                                  | -0.3  | 3.6  |      |

|                                                                                  | GSNS                                       |                                                  | -0.35 | 0.35 |      |

|                                                                                  | PGND                                       |                                                  | -0.3  | 0.3  |      |

|                                                                                  | PGOOD                                      |                                                  | -0.3  | 6    |      |

| Output voltage range <sup>(2)</sup>                                              | VREF                                       |                                                  | -0.3  | 3.6  | V    |

|                                                                                  | NC                                         |                                                  | -5    | 36   |      |

| Electrostatio discharge                                                          | Human b                                    | oody model (HBM) QSS 009-105 (JESD22-A114A)      |       | 2000 | V    |

| Electrostatic discharge Charged device model (CDM) QSS 009-147 (JESD22-C101B.01) |                                            | device model (CDM) QSS 009-147 (JESD22-C101B.01) |       | 500  |      |

| Junction temperature rar                                                         | Junction temperature range, T <sub>J</sub> |                                                  |       | 150  | °C   |

| Storage temperature ran                                                          | ge, T <sub>stg</sub>                       |                                                  | -55   | 150  |      |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to the network ground terminal unless otherwise noted.

#### **THERMAL INFORMATION**

|                    |                                              | TPS51363               |       |

|--------------------|----------------------------------------------|------------------------|-------|

|                    | THERMAL METRIC <sup>(1)</sup>                | QFN (RVE)<br>(28 PINS) | UNITS |

| θ <sub>JA</sub>    | Junction-to-ambient thermal resistance       | 40.2                   |       |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance    | 22.8                   |       |

| θ <sub>JB</sub>    | Junction-to-board thermal resistance         | 20.1                   | °C/W  |

| Ψ <sub>JT</sub>    | Junction-to-top characterization parameter   | 1.6                    | °C/vv |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter | 19.4                   |       |

| θ <sub>JCbot</sub> | Junction-to-case (bottom) thermal resistance | 2.2                    |       |

# (1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953. **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                                                |                           | MIN  | MAX  | UNIT |

|------------------------------------------------|---------------------------|------|------|------|

|                                                | VIN                       | 3    | 22   |      |

| Supply voltage range                           | V5                        | 4.6  | 5.5  |      |

|                                                | BST                       | -0.1 | 33.5 |      |

|                                                | SW                        | -3   | 27   |      |

| Innut voltage renge                            | EN, TRIP, NU, MODE        | -0.1 | 5.5  | V    |

| Input voltage range                            | SLEW, VSNS, REFIN, REFIN2 | -0.1 | 3.5  | V    |

|                                                | GSNS                      | -0.1 | 0.3  |      |

|                                                | PGND                      | -0.1 | 0.1  |      |

|                                                | PGOOD                     | -0.1 | 5.5  |      |

| Output voltage range                           | VREF, SLEW                | -0.1 | 3.5  |      |

| Operating free-air temperature, T <sub>A</sub> |                           | -10  | 85   | °C   |

Texas

www.ti.com

## **ELECTRICAL CHARACTERISTICS**

| over operating free-air temperature range, | $V_{\rm IN} = 12 \text{ V}, V_{\rm V5} = 5 \text{ V}.$                 | $MODE = GND$ , $V_{EN} = 3.3$ | V (unless otherwise noted) |

|--------------------------------------------|------------------------------------------------------------------------|-------------------------------|----------------------------|

| erer eperaang nee an temperature range,    | $, \cdot   _{N}  \cdot = \cdot, \cdot \cdot v_{D}  \circ \cdot \cdot,$ |                               |                            |

|                        | PARAMETER                | TEST CONDITION                                                        | MIN   | TYP  | MAX  | UNIT |

|------------------------|--------------------------|-----------------------------------------------------------------------|-------|------|------|------|

| SUPPLY C               | URRENT                   |                                                                       |       |      |      |      |

| I <sub>V5</sub>        | V5 supply current        | $T_A=25^{\circ}C$ , No load, $V_{EN}=5 V$                             |       | 560  |      | μA   |

| I <sub>V5SDN</sub>     | V5 shutdown current      | T <sub>A</sub> =25°C, No load, V <sub>EN</sub> = 0 V                  |       | 1    |      | μA   |

| VREF OUT               | PUT                      |                                                                       | I     |      |      |      |

| . ,                    |                          | I <sub>VREF</sub> = 30 μA, w.r.t. GSNS                                |       | 2    |      | V    |

| V <sub>VREF</sub>      | Reference voltage        | 0 μA ≤ I <sub>VREF</sub> ≤ 300 μA, -10°C ≤ T <sub>A</sub> ≤ 85°C      | -1.0% |      | 1.0% | -    |

| IVREF(OCL)             | Current limit            | (V <sub>VREF</sub> –V <sub>GSNS</sub> ) = 1.7 V                       | 0.4   | 1    |      | mA   |

| 1 1                    | AMPLIFIER                |                                                                       | L.    |      | 1    | -    |

| I <sub>VSNS</sub>      | VSNS input current       | V <sub>VSNS</sub> = 1 V                                               | -1    |      | 1    | μA   |

| I <sub>VSNS(DIS)</sub> | VSNS discharge current   | V <sub>EN</sub> = 0 V, V <sub>VSNS</sub> = 0.5 V                      |       | 12   |      | mA   |

| SWITCH TI              | IMING                    |                                                                       | 1     |      |      |      |

| t <sub>OFF(min)</sub>  | Minimum off-time         |                                                                       |       | 320  |      | ns   |

| t <sub>DEAD1</sub>     | Deadtime1 <sup>(1)</sup> | SW rising to falling                                                  |       | 35   |      | ns   |

| t <sub>DEAD2</sub>     | Deadtime2 <sup>(1)</sup> | SW falling to rising                                                  |       | 10   |      | ns   |

| INTERNAL               | BOOT STRAP SW            |                                                                       |       |      |      |      |

| V <sub>FBST</sub>      | Forward foltage          | $V_{V5}$ - $B_{ST}$ , $T_A$ = 25°C, $I_F$ = 10 mA                     |       | 0.1  | 0.2  | V    |

| I <sub>BST</sub>       | BST leakage current      | T <sub>A</sub> = 25°C, V <sub>BST</sub> = 14 V, V <sub>SW</sub> = 7 V |       | 0.01 | 1.5  | μA   |

|                        | N-RESISTANCE             |                                                                       |       |      |      |      |

| R <sub>DS(on)H</sub>   | High-side on-resistance  | $T_A = 25^{\circ}C, V_{V5} = 5 V$                                     |       |      | 20   | mΩ   |

| R <sub>DS(on)L</sub>   | Low-side on-resistance   | $T_A = 25^{\circ}C, V_{V5} = 5 V$                                     |       |      | 10   | mΩ   |

| LOGIC TH               | RESHOLD                  |                                                                       |       |      |      |      |

| V <sub>MODE(TH)</sub>  | MODE threshold voltage   | MODE = Float                                                          |       | 2.5  |      | V    |

| V <sub>LL</sub>        | EN low-level voltage     |                                                                       |       |      | 0.35 | V    |

| V <sub>LH</sub>        | EN high-level voltage    |                                                                       | 0.9   |      |      | V    |

| V <sub>L(HYST)</sub>   | EN hysteresis voltage    |                                                                       |       | 0.25 |      | V    |

| V <sub>L(LK)</sub>     | EN input leakage current |                                                                       | -1    | 0    | 1    | μA   |

| SOFT-STA               | RT                       |                                                                       |       |      |      |      |

| I <sub>SS</sub>        | Soft-Start current       | Soft-start current source                                             |       | 10   |      | μA   |

| PGOOD CO               | OMPARATOR                |                                                                       |       |      | L    |      |

| V <sub>PGTH</sub>      | PGOOD threshold          | PGOOD in from lower (startup)                                         |       | 92%  |      |      |

| I <sub>PG</sub>        | PGOOD sink current       | V <sub>PGOOD</sub> = 0.5V                                             |       | 6    |      | mA   |

| t <sub>PG(CMPSS)</sub> | PGOOD start-up delay     | PGOOD comparator startup delay                                        |       | 1.5  |      | ms   |

| I <sub>PG(LK)</sub>    | PGOOD leakage current    |                                                                       | -1    | 0    | 1    | μA   |

(1) Ensured by design.

#### SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

## **ELECTRICAL CHARACTERISTICS (continued)**

over operating free-air temperature range,  $V_{IN}$  = 12 V,  $V_{V5}$  = 5 V, MODE = GND,  $V_{EN}$  = 3.3 V (unless otherwise noted)

|                                | PARAMETER                                          | TEST CONDITION                                                    | MIN    | TYP  | MAX    | UNIT |

|--------------------------------|----------------------------------------------------|-------------------------------------------------------------------|--------|------|--------|------|

| OVERCUP                        | RENT LIMIT LEVEL                                   |                                                                   |        |      |        |      |

|                                | Current limit threshold                            | $V_{TRIP} = 0 V$ , valley current set point, $T_A=25^{\circ}C$    | 7      | 7 8  | 9      | •    |

| I <sub>OCL</sub>               | Current limit threshold                            | $V_{TRIP} = 5 V$ , valley current set point, T <sub>A</sub> =25°C | 10.5   | 12   | 13.5   | A    |

| V <sub>ZC</sub> <sup>(2)</sup> | Zero cross detection offset                        |                                                                   |        | 0    |        | mV   |

| PROTECT                        | IONS                                               |                                                                   |        |      |        |      |

| V <sub>POR</sub>               | V5 POR threshold voltage <sup>(2)</sup>            | Reset OVP fault                                                   |        | 1.7  |        | V    |

| V <sub>PORHYS</sub>            | V5 POR threshold voltage hysteresis <sup>(2)</sup> | Reset OVP fault hysteresis                                        |        | 85   |        | mV   |

| 17                             | V5 UVLO threshold voltage                          | Wake-up                                                           | 4.3    | 4.4  | 4.6    | V    |

| V <sub>UVLO</sub>              |                                                    | Shutdown                                                          | 3.8    | 4    | 4.2    |      |

| V <sub>OVP</sub>               | OVP threshold voltage                              | OVP detect voltage                                                | 118%   | 120% | 123%   |      |

| t <sub>OVPDLY</sub>            | OVP propagation delay                              | With 100 mV overdrive                                             |        | 430  |        | ns   |

| V <sub>OOB</sub>               | OOB threshold voltage                              |                                                                   | 105.5% |      | 109.5% |      |

| V <sub>UVP</sub>               | UVP threshold voltage                              | UVP detect voltage                                                | 63%    | 66%  | 69%    |      |

| t <sub>UVPDLY</sub>            | UVP delay                                          |                                                                   |        | 1    |        | ms   |

| THERMAL                        | SHUTDOWN                                           |                                                                   |        |      |        |      |

| <b>-</b>                       | The sum of a busideness threads and (2)            | Shutdown temperature                                              |        | 140  |        | •••  |

| T <sub>SDN</sub>               | Thermal shutdown threshold <sup>(2)</sup>          | Hysteresis                                                        |        | 10   |        | °C   |

(2) Ensured by design.

TEXAS INSTRUMENTS

SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

www.ti.com

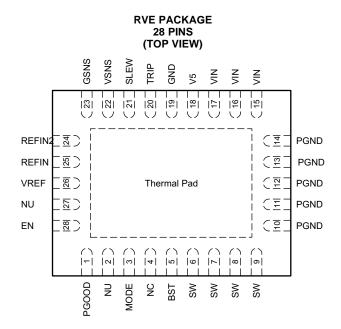

## **DEVICE INFORMATION**

Texas

NSTRUMENTS

#### SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

| NAME         | NO.   | I/O/P | DESCRIPTION                                                                                                   |

|--------------|-------|-------|---------------------------------------------------------------------------------------------------------------|

| BST          | 5     | I     | Power supply for internal high side MOSFET. Connect a 0.1-µF bootstrap capacitor between this pin and SW pin. |

| EN           | 28    | I     | Enable signal, 1.05-V logic compatible.                                                                       |

| GND          | 19    | _     | General device ground.                                                                                        |

| GSNS         | 23    | 0     | GND sense input. Connect GSNS to general/system ground or GND sensing point at the output return.             |

| MODE         | 3     | I     | Frequency (400 kHz or 800 kHz) programmable input (see Table 3).                                              |

| NC           | 4     | _     | Not connected.                                                                                                |

| NU           | 2, 27 | _     | Not used for external applications.                                                                           |

|              | 10    |       |                                                                                                               |

|              | 11    |       |                                                                                                               |

| PGND         | 12    | _     | Power ground. Connect to the system ground.                                                                   |

|              | 13    |       |                                                                                                               |

|              | 14    |       |                                                                                                               |

| PGOOD        | 1     | 0     | PGOOD output. Connect a pull-up resistor with a value of 100 k $\Omega$ to this pin.                          |

| Power<br>PAD | 29    | _     | Connect to system ground by multiple vias.                                                                    |

| REFIN        | 25    | I     | Target output voltage input pin. 0.6 V to 2 V, 1.05 V/1.2 V built-in (GND and Open) (see Table 2).            |

| REFIN2       | 24    | I     | Tie to GND or float. This input is used to determine the fixed voltage setpoint (see Table 2).                |

| SLEW         | 21    | 0     | Connect a capacitor between this pin and GND for soft start and integrator functions.                         |

|              | 6     |       |                                                                                                               |

| SW           | 7     | 0     | Switching roads sutput. Connect suternal industor                                                             |

| 500          | 8     | 0     | Switching node output. Connect external inductor.                                                             |

|              | 9     |       |                                                                                                               |

| TRIP         | 20    | I     | OCL programmable input (see Table 4).                                                                         |

| V5           | 18    | I     | 5-V power supply for analog circuits and gate driver.                                                         |

|              | 15    | I     |                                                                                                               |

| VIN          | 16    | I     | Power supply input pin. Apply 3-V to 22-V of supply voltage.                                                  |

|              | 17    | I     |                                                                                                               |

| VREF         | 26    | 0     | 2-V reference output. Connect A 0.22-µF ceramic capacitor between this pin and the GNDS pin.                  |

| VSNS         | 22    | I     | Output voltage sense input.                                                                                   |

www.ti.com

INSTRUMENTS

Texas

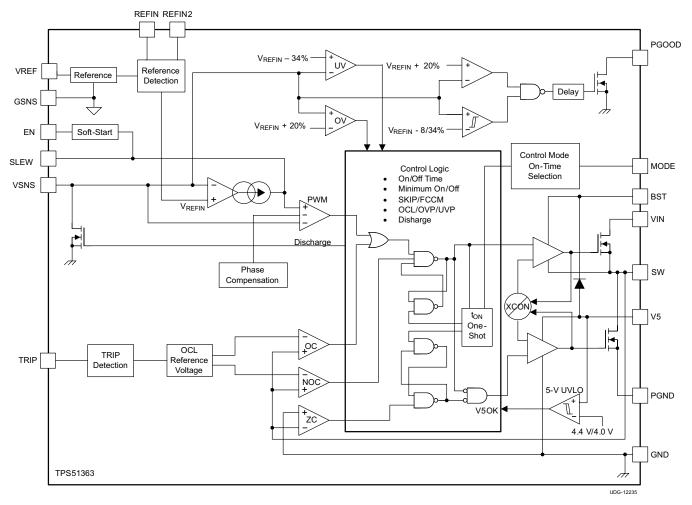

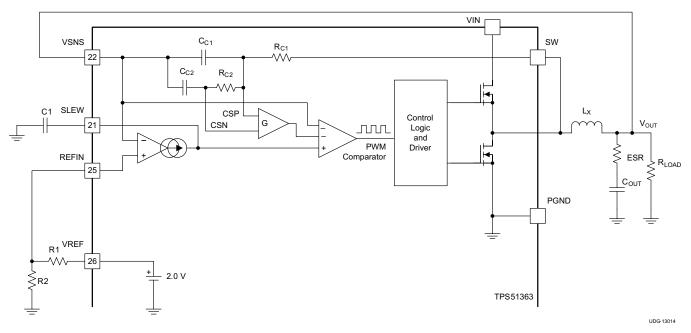

## FUNCTIONAL BLOCK DIAGRAM

#### SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

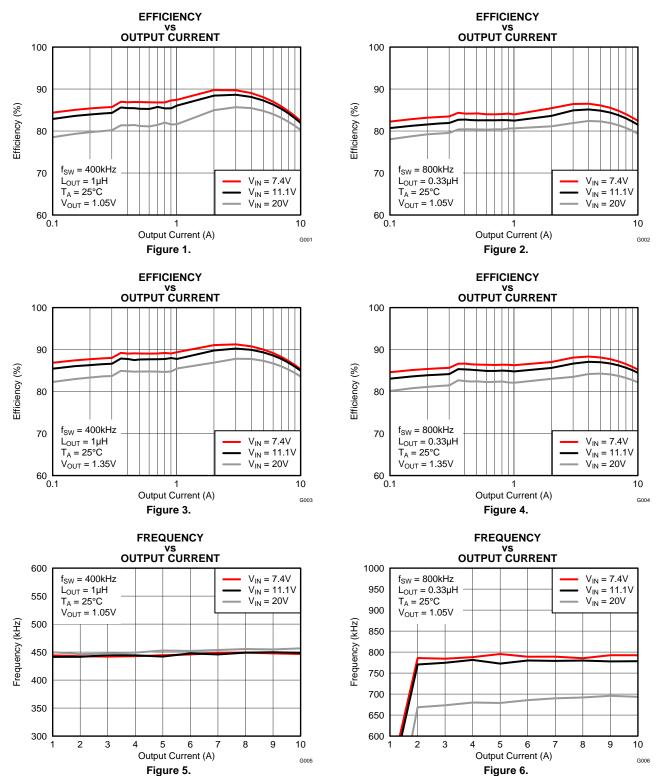

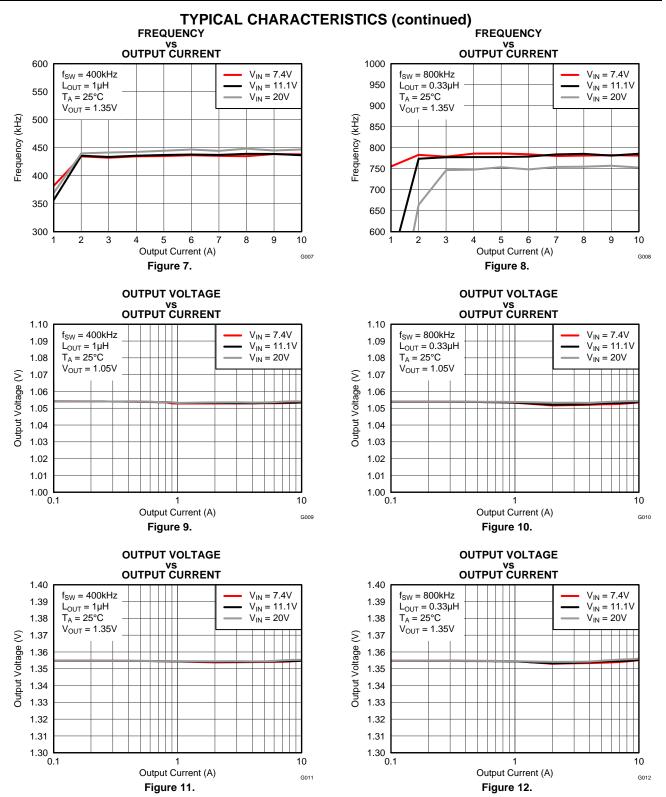

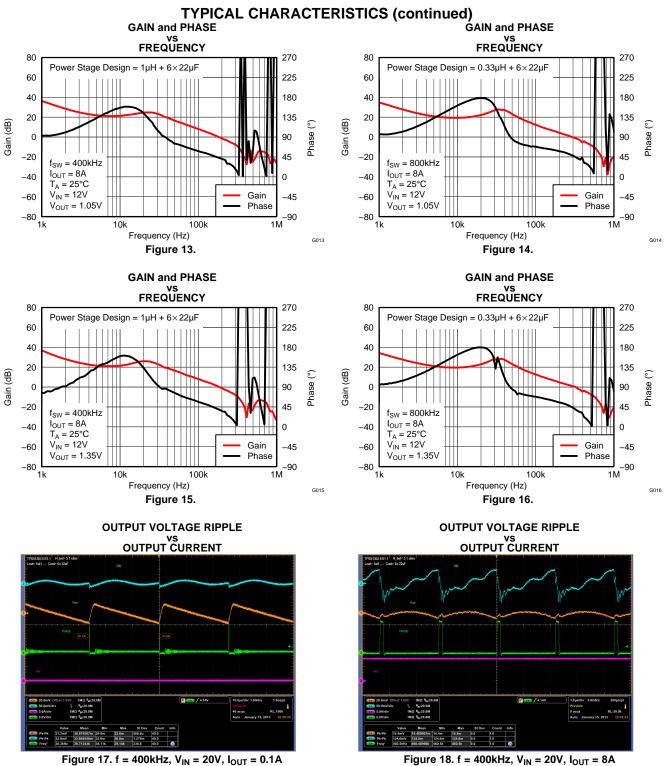

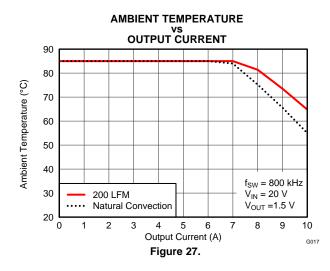

## **TYPICAL CHARACTERISTICS**

Texas

Instruments

www.ti.com

SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

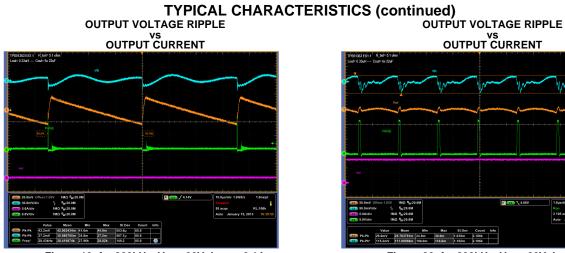

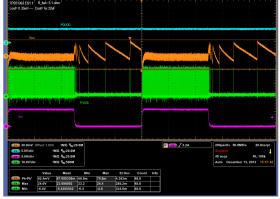

Figure 18. f = 400kHz, V<sub>IN</sub> = 20V, I<sub>OUT</sub> = 8A

www.ti.com

Figure 19. f = 800kHz,  $V_{IN}$  = 20V,  $I_{OUT}$  = 0.1A

Figure 21. f = 400kHz,  $V_{IN}$  = 20V,  $I_{OUT}$  = 0–5A

Figure 23. f = 400kHz, V<sub>IN</sub> = 20V, I<sub>OUT</sub> = 8A

Figure 20. f = 800kHz, V<sub>IN</sub> = 20V, I<sub>OUT</sub> = 8A

TRANSIENT PERFORMANCE SWITCHING FREQUENCY

Figure 22. f = 800kHz, V<sub>IN</sub> = 20V, I<sub>OUT</sub> = 0–6A

Figure 24. f = 800kHz, V<sub>IN</sub> = 20V, I<sub>OUT</sub> = 0A

www.ti.com

## **TYPICAL CHARACTERISTICS (continued)**

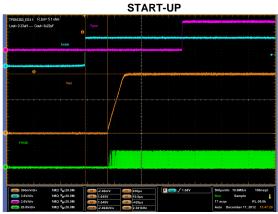

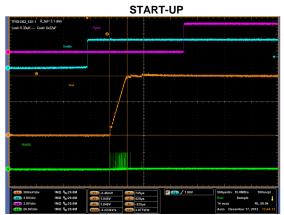

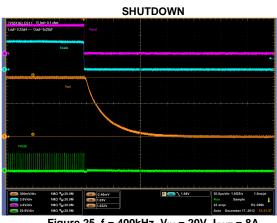

Figure 25. f = 400kHz,  $V_{IN}$  = 20V,  $I_{OUT}$  = 8A

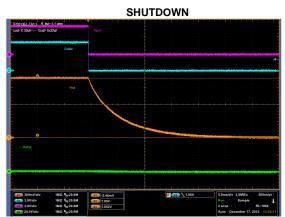

Figure 26. f = 800kHz,  $V_{IN}$  = 20V,  $I_{OUT}$  = 0A

TPS51363

SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

www.ti.com

### **APPLICATION INFORMATION**

#### **Functional Overview**

The TPS51363 is an 8-A or 10-A (see Table 1), integrated FET synchronous step-down converter with differential voltage feedback support.

It uses adaptive on-time D-CAP2 for compensation-less stable loop operation in POSCAP, POSCAP/MLCCs and all MLCCs output capacitor configurations.

TPS51363 automatically operates in discontinuous mode to optimize light-load efficiency. A configurable 400-kHz or 800-kHz switching frequency enables optimization of the power train for cost, size and efficiency performance of the design.

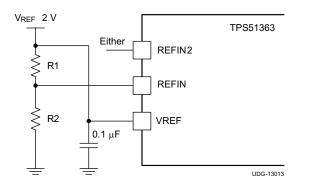

#### VREF, REFIN, REFIN2 and Output Voltage

This device provides a 2.0-V, accurate voltage reference from the VREF pin. This output has a 300-uA sourcing current capability to drive voltage setpoint reference through a voltage divider circuit as shown in Figure 28. To ensure higher overall system voltage accuracy, the sum of the total resistance from VREF to GND should be designed to be more than 67kohm. A MLCC capacitor with a value of 0.1uF or larger should be attached close to the VREF pin. The voltage setpoint range supported by this device is between 0.6 V and 2.0 V.

This device also supports resistor-less fixed voltage operation by the use of both REFIN and REFIN2 pins. Table 2 lists all the possible fixed voltage configurations by the REFIN and REFIN2 pin. The TPS51363 detects the state of both REFIN and REFIN2 during the initial startup and decides the output voltage setpoint for the operation.

| VOLTA                              | GE (V)                               |                                        |

|------------------------------------|--------------------------------------|----------------------------------------|

| REFIN PIN<br>(V <sub>REFIN</sub> ) | REFIN2 PIN<br>(V <sub>REFIN2</sub> ) | V <sub>OUT</sub> OUTPUT<br>VOLTAGE (V) |

| GND                                | GND                                  | 1.05                                   |

| Float                              | GND                                  | 1.2                                    |

| GND                                | Float                                | 1.5                                    |

| Float                              | Float                                | 1.35                                   |

| Resistor dividers                  | Either GND or<br>Float               | Adjustable from 0.6 to 2.0             |

#### Table 2. REFIN and REFIN2 Pin Settings

Figure 28. Setting the Output Voltage

#### **PWM Operation**

www.ti.com

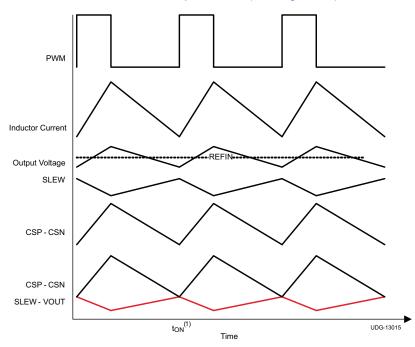

TPS51363 employs DCAP2 mode operation. It uses an internal phase compensation network ( $R_{C1}$ ,  $R_{C2}$ ,  $C_{C1}$ ,  $C_{C2}$  and gain) to work with very low ESR output capacitors such as multi-layer ceramic capacitor (MLCC). The role of such network is to sense and scale the current ripple component of the output inductor current information and then use it in conjunction with the voltage feedback signal to achieve loop stability of the converter.

The transconductance  $(g_M)$  amplifier and SLEW capacitor (C1) forms an integrator. The output ripple voltage generated is inversed and averaged by this integrator. The AC information is superimposed onto otherwise DC information and forms a reference voltage at the input of the PWM comparator. As long as the integrator time constant is much larger than the inverse of the loop crossover frequency, the AC component is negligible.

$$\frac{gM}{(2\pi \times C1)} \leq \frac{f_0}{10}$$

where

- g<sub>M</sub> is 60 μS

- f<sub>0</sub> is 1/3 or 1/4 of the switching frequency (f<sub>SW</sub>)

(1)

The voltage difference ( $V_{SLEW} - V_{VSNS}$ ) is then compared to the Gx(CSP-CSN) (see Figure 30) voltage at the PWM comparator inputs. The PWM comparator creates a SET signal to turn on the high-side MOSFET during each cycle when the current level falls below the loop demand (see Figure 29).

Figure 29. On-Time Waveforms <sup>(1)</sup>

(1) ON time is initiated by (VOUT-SLEW) and (CSP-CSN) crossover

(2)

#### SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

The device operates at two distinct switching frequencies, 400 kHz and 800 kHz. The switching frequency is configured by MODE pin for this converter operation (see Table 3). For stable operation of the buck converter, it is generally recommended to have a unity gain crossover ( $f_0$ ) of 1/4 or 1/3 or the switching frequency. (see Table 3).

| Tuble 6. Mode and Recommended Frequency Cettings |                             |     |                              |  |

|--------------------------------------------------|-----------------------------|-----|------------------------------|--|

|                                                  | FREQUENCY (kHz)             |     |                              |  |

| MODE                                             | CROSSOVER (f <sub>0</sub> ) |     | SWITCHING (f <sub>sw</sub> ) |  |

|                                                  | MIN                         | MAX | SWITCHING (I <sub>SW</sub> ) |  |

| GND                                              | 100                         | 133 | 400                          |  |

| FLOAT                                            | 200                         | 267 | 800                          |  |

#### Table 3. Mode and Recommended Frequency Settings

Given the range of the recommended unity gain frequency, the power stage design is flexible, as long as the following equation is satisfied.

$$f_{LC} = \frac{1}{2\pi \times \sqrt{L_{OUT} \times C_{OUT}}} \le \frac{1}{10} \times f_0$$

Operating in D-CAP2 mode, the overall loop response is dominated by the internal phase compensation network. The compensation network is designed to have two identical zeros at 4 kHz (400-kHz operation) and 8 kHz (800-kHz operation) in the frequency domain, which serves the purpose of splitting the LC double pole into one low frequency pole (same as the L-C double pole) and one high-frequency pole (greater than the unity gain crossover frequency).

Figure 30. Simplified Architecture Illustrating DCAP2 Mode

## Light-Load Operation

The mandatory light load operation for TPS51363 is referred to as auto skip. In auto-skip mode, the control logic automatically reduces its switching frequency to improve light load efficiency. To achieve this intelligence, a zero crossing detection comparator is used to prevent negative inductor current by turning off the low side FET when the SW crossing zero is detected. The equation below shows the boundary load condition of this skip mode and continuous conduction operation.

$$I_{LOAD(LL)} = \frac{(V_{IN} - V_{OUT})}{2 \times L_X} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}}$$

(3)

#### Power Sequences: Soft-Start and Power Good

Prior to asserting EN high, the power stage conversion voltage and V5IN voltage should be up and running. When EN is asserted high, TPS51363 provides soft start operation to suppress in-rush current during startup. The soft start action is achieved by an internal SLEW current of 10  $\mu$ A (typ) sourcing into a small external MLCC capacitor connected from SLEW pin to GND.

Use Equation 4 to determine the soft-start timing.

$$t_{SS} = C_{SLEW} \times \frac{V_{OUT}}{I_{SLEW}}$$

where

- C<sub>SLEW</sub> is the soft-start capacitance

- V<sub>OUT</sub> is the output voltage

- I<sub>SLEW</sub> is the internal, 10-µA current source

(4)

The TPS51363 includes a PGOOD open drain output. During the startup, once the output voltage is slewing up within -8% of the final setpoint target, the PGOOD becomes asserted after 1.5 ms of delay from the end of the soft-start period. During the operation, if the output voltage rises beyond 120% (typ) of the setpoint, the PGOOD pin becomes immediately de-asserted without hysteresis. Re-asserting the PGOOD pin requires either resetting either the V5IN pin or the EN pin. If the output voltage falls below 68% (typ) of the setpoint, the PGOOD pin becomes immediately de-asserted without hysteresis. Re-asserting the PGOOD pin requires resetting either the V5IN pin or the EN pin.

## **Fault Protection**

#### **Overcurrent Limit**

TPS51363 integrates both high side and low side FETs to support a maximum DC current of 8-A or 10-A operation. The current sensing method employed for over current limit is to monitor the SW node during the "ON" state of the low side FET for each switching cycle. TRIP pin is used to program one of the two current limits for TPS51363 operation (see Table 4). When the overcurrent limit is detected, the converter does not allow the next "ON" cycle for the high side FET until the overcurrent limit is no longer reached. This ensures the safe operation of the converter. And when the overcurrent limit condition persists, the current to the load exceeds the current to the output capacitors, the output voltage tends to fall. When the output voltage falls below the undervoltage protection threshold, the converter latch shut down.

| TRIP | TYPICAL OCL<br>LIMIT I <sub>OCL</sub> (A) |

|------|-------------------------------------------|

| GND  | 8                                         |

| 5V   | 12                                        |

Table 4. TRIP Pin Settings

#### Negative Overcurrent Limit

TPS51363 is also protected by the negative over current limit. Both positive and negative current limit is programmed by the TRIP pin. Negative current limit level is the same as that of positive current limit level (see Table 4). During the normal converter operation, negative current is not allowed due to the mandatory light load operation for this device (Auto Skip). It is during the OOB or OVP operation, negative overcurrent might be engaged.

SLUSBB5A -FEBRUARY 2013-REVISED JUNE 2013

#### **Out-of-Bounds Operation (OOB)**

When the output voltage rises to 8% above the target value, the out-of-bound operation starts. During the OOB operation, the controller operates in forced PWM-only mode by turning on low side FET. Turning on the low side FET beyond the zero inductor current can quickly discharge the output capacitor thus causing  $V_{OUT}$  to fall quickly towards setpoint. During the operation, the cycle by cycle negative current limit is also activated to ensure the safe operation of the internal FETs.

#### **Overvoltage Profection (OVP) and Undervoltage Protection (UVP)**

When the output voltage rises to a level 20% (typ) higher than the setpoint voltage, an overvoltage condition is present. When a 0-V event is detected, the converter turns off the high side FET and turns on the low side FET. The operation continues until the cycle by cycle negative current limit is reached and low side FET is turned off and high side FET is turned on, for a minimum on-time. After the minimum on-time expires, the high side FET is driven off and low side FET is driven on again until negative current limit is reached or  $V_{OUT}$  is discharged to 0 V. When the  $V_{OUT}$  is discharged to 0 V, both high-side and low-side FETs are latched off. An OVP fault requires the V5IN voltage to fall below POR threshold or EN reset to clear.

#### Undervoltage Protection (UVP)

The undervoltage protection (UVP) is set when the  $V_{OUT}$  voltage falls below 68% (typ) of the setpoint voltage for 1msec or longer. In this fault condition, the converter turns off both high-side and low-side FETs. The UVP function is enabled after 1.4 ms of soft start completion. An UVP fault requires 5-V UVLO or EN reset.

#### V5IN Undervoltage Lockout (UVLO) Protection

TPS51363 has a 5-V supply undervoltage lockout protection (UVLO) threshold. When the V5IN voltage is lower than UVLO threshold voltage, Vout is shut off. This is a non-latch protection.

#### Power-On-Reset (POR)

To prevent single rail supply voltage brown-out due to output OV condition, when the output voltage is shut down due to OVP fault, Power-on-Reset (POR) on V5IN is implemented. To reset OVP fault, V5IN voltage must fall below POR threshold voltage of 1.7 V (typ) or EN reset to clear.

#### Thermal Shutdown

TPS51363 includes an internal temperature monitor. If the die temperature exceeds the threshold (published in the EC table of this datasheet), the converter will be shutdown. This is a non-latch protection and the operation is restarted with soft-start sequence when the device temperature is reduced by the hysteresis.

## DESIGN PROCEDURE

## Introduction

The simplified design procedure is done for a VCCIO rail for Intel platform application using TPS51363.

#### Step One: Determine the system specifications.

The VCCIO rail requirements provide the following key parameters:

- V<sub>OUT</sub> = 1.05 V

- $I_{CC(max)} = 6 A$

- $I_{\text{DYN(max)}} = 4 \text{ A}$

#### Step Two: Determine the power supply design specifications.

The input voltage range and operating frequency are of primary interest. For this example:

- 7.4 V ≤ V<sub>IN</sub> ≤ 19.5 V

- f<sub>SW</sub> = 800 kHz

#### Step Three: Set the output voltage.

TPS51363 supports resistor-less fixed voltage operation by the use of both REFIN and REFIN2 pins (see Table 2). Grounding both REFIN and REFIN2 pins provides a 1.05-V fixed output setpoint.

#### Step Four: Determine inductance value and choose inductor.

Smaller values of inductor have better transient performance and smaller physical size but higher ripple and lower efficiency. Higher values have the opposite characteristics. It is common practice to limit the ripple current to 25% to 50% of the maximum current. For this example, use 30% as a starting point.  $I_{L(P-P)}$ = 6 A × 0.30 = 1.8 A. For a switching frequency of 800 kHz, maximum 19.5-V input and 1.05-V output.

$$L = \frac{V \times dT}{I_{P-P}} = \frac{(V_{IN} - V_{OUT}) \times \left(\frac{V_{OUT}}{f_{SW} \times V_{IN}}\right)}{I_{P-P}} = \frac{(19.5 V - 1.05 V) \times \left(\frac{1.05 V}{800 \text{ kHz} \times 19.5 V}\right)}{1.8 \text{ A}} = 0.68 \,\mu\text{H}$$

(5)

For this application, a 0.68- $\mu$ H, 6.8-mm × 7.3-mm × 3.0-mm inductor with typical DCR of 4.8 m $\Omega$  and heating current of 16 A is chosen. The Cyntec part number of the inductor is PIMB063T.

#### Step Five: Calculate SLEW capacitance.

The SLEW pin is used to program the soft-start time. During soft-start operation, the current source used to program the SLEW rate is 10  $\mu$ A (typ). In this design example, the soft-start timing should be target to be in the range of 500  $\mu$ s to 2 ms. The proper slew rate design minimizes large inductor current perturbation during the startup, thus reducing the possibility of acoustic noise in the system.

$$C_{SLEW} = I_{SLEW} \times \frac{dt}{\Delta V_{OUT}} = 10 \text{ nF}$$

• I<sub>SLEW</sub> = 10 μA,

• dt = t<sub>SS</sub> = 1 ms

• ΔV<sub>OUT</sub> = 1.05 V

#### Step Six: Select the proper OCL.

There are two options for the over current limit (see Table 4). For this application example, because  $I_{CC(max)} = 6$  A, the proper OCL level should be set at least 30% over the  $I_{CC(max)}$  level, which makes the 8-A OCL appropriate for this design. Grounding the TRIP pin achieves this effect.

#### Step Seven: Determine the output capacitance.

The amount of the output capacitance needed for this design is both a function of loop stability and of transient requirement.

Copyright © 2013, Texas Instruments Incorporated

### Stability considerations

Texas Instruments

www.ti.com

The switching frequency of the design example is 800 kHz (which is set by the MODE pin, see Table 4). For D-CAP2 mode operation, it is generally recommended to have a unity gain crossover (f0) of less than 1/4 or 1/3 of the switching frequency, which is approximately between 200 kHz and 266 kHz. In this design example, use 1/4.

$$f_0 = \frac{f_{SW}}{4} = 200 \text{ kHz}$$

(7)

Given the range of the recommended unity gain crossover frequency, the power stage design is flexible, as long as the L-C double pole frequency is less than 10% of  $f_0$ .

When the above criterion is met, the internal compensation network provides sufficient phase boost at the unity gain crossover frequency such that the converter is stable with sufficient phase margin (greater than 60°).

When the ESR frequency of the output bulk capacitor is in the vicinity of the unity gain crossover frequency of the loop, additional phase boost can be achieved. This applies to higher ESR output bulk capacitor, POSCAP and SPCAP.

When the ESR frequency of the output capacitor is beyond the unity gain crossover frequency of the control loop, no additional phase boost is achieved. This applies to low or ultra low ESR output capacitor, such as MLCCs.

For this application example, consider only all MLCCs for output capacitors. Based on Equation 3 and Equation 7, the minimum capacitance for stable operation is calculated to be 110  $\mu$ F.

#### Transient considerations

- $I_{\text{DYN(max)}} = 4 \text{ A}$

- di/dt = 2.5 A/µs

- V<sub>OUT</sub> deviation = ±3% for the given transient

Use Equation 8 and Equation 9 to estimate the amount of capacitance needed for a given dynamic load/release.

$$C_{OUT(min\_under)} = \frac{L \times \left(\Delta I_{LOAD(max)}\right)^{2} \times \left(\frac{V_{OUT} \times t_{SW}}{V_{IN(min)}} + t_{MIN(off)}\right)}{2 \times \Delta V_{LOAD(insert)} \times \left(\left(\frac{V_{IN(min)} - V_{OUT}}{V_{IN(min)}}\right) \times t_{SW} - t_{MIN(off)}\right) \times V_{OUT}}$$

$$C_{OUT(min\_over)} = \frac{L_{OUT} \times \left(\Delta I_{LOAD(max)}\right)^{2}}{2 \times \Delta V_{LOAD(release)} \times V_{OUT}}$$

(8)

(9)

Based on these calculation, to meet the transient requirement, the minimum amount of capacitance in this design is 164  $\mu$ F.

Considering both stability and transient, the minimum capacitance is 164  $\mu$ F. The design example uses 8, 22- $\mu$ F capacitors with minor consideration of the MLCC derating for both DC and AC effect.

#### Step Eight: Select decoupling and peripheral components

For the TPS51363, peripheral capacitors use the following minimum values of ceramic capacitance. X5R or better temperature coefficient is recommended. Tighter tolerance and higher voltage rating are always appropriate.

- V5IN decoupling  $\geq$  2.2 µF,  $\geq$  10 V

- VREF decoupling 0.1  $\mu$ F to 1  $\mu$ F,  $\geq$  4 V

- Bootstrap capacitor ≥ 0.1 µF, ≥ 10 V

- Pull-up resistors on PGOOD, 100 kΩ

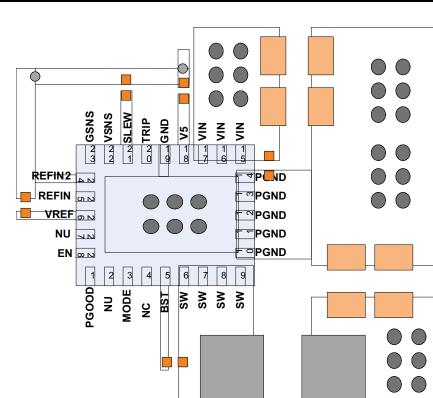

#### Step Nine: Layout guidelines

Figure 31 applies to the layer where device is situated. Additional reinforcement of VIN, PGND, and VOUT through vias are always recommended.

Figure 31. TPS51363 Design Layout

Input capacitors, output capacitors, and the output inductor are the power components and should be placed on one side of the PCB. Small signal components can be placed on the same side of the PCB with proper ground isolation or the opposite side with at least one inner ground plane in between, depending on the system/motherboard design requirement.

All sensitive analog traces and components such as VSNS, GSNS, SLEW, VREF, REFIN and REFIN2 should be placed away from the high voltage switching node, such as SW and BST to avoid switching noise coupling. Use internal layer(s) as ground plane(s) and shield feedback traces from power traces.

VSNS can be connected directly to the output voltage sense point at the load device or the bulk capacitor at the converter side. Connect GSNS to ground return at the general ground plane/layer. VSNS and GSNS can be used for the purpose of remote sensing across the load device, however, ensure to minimize the routing trace length to prevent excess noise injection into the sense lines.

In order to effectively remove heat from the package, prepare the thermal land and solder to the package thermal pad. Wide trace of the component-side copper, connected to this thermal land, helps to dissipate the heat. Numerous vias (at least 6) with a 0.3-mm diameter connected from the thermal land to the internal/solder side ground plane(s) should be used to help dissipation.

www.ti.com

NSTRUMENTS

**EXAS**

## **REFERENCE DESIGNS**

This section describes two typical application circuits using the TPS51363.

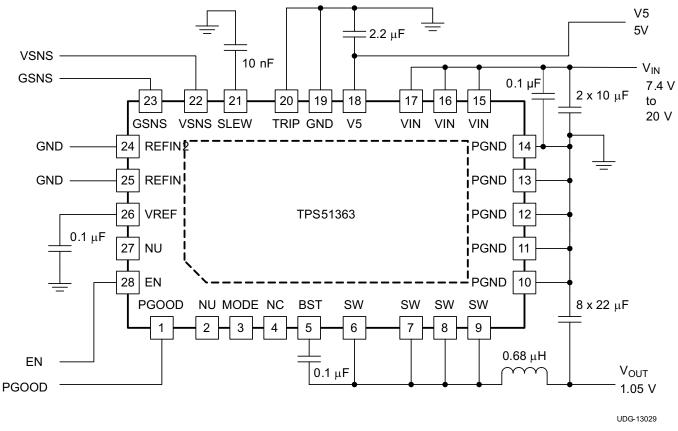

### Design 1

This design is a VCCIO application with an output voltage of 1.05 V, maximum processor current ( $I_{CC(max)}$ ) of 6 A, an OCL of 8 A and a switching frequency of 800 kHz.

Figure 32. Design 1: Application Schematic

| Table | 5. | Design | 1 | : | List | of | Materials |

|-------|----|--------|---|---|------|----|-----------|

|-------|----|--------|---|---|------|----|-----------|

| REFERENCE<br>DESIGNATOR | QTY | SPECIFICATION   | MANUFACTURER | PART NUMBER       |  |  |

|-------------------------|-----|-----------------|--------------|-------------------|--|--|

| C <sub>IN</sub>         | 2   | 10 µF, 25 V     | Taiyo Yuden  | TMK325BJ106MM     |  |  |

| C <sub>OUT</sub>        | 8   | 22 µF, 6.3 V    | Murata       | GRM21BB30J226ME38 |  |  |

| L <sub>OUT</sub>        | 1   | 0.68 μH, 4.8 mΩ | Cyntec       | PIMB063T-R68MS-63 |  |  |

TPS51363

#### www.ti.com

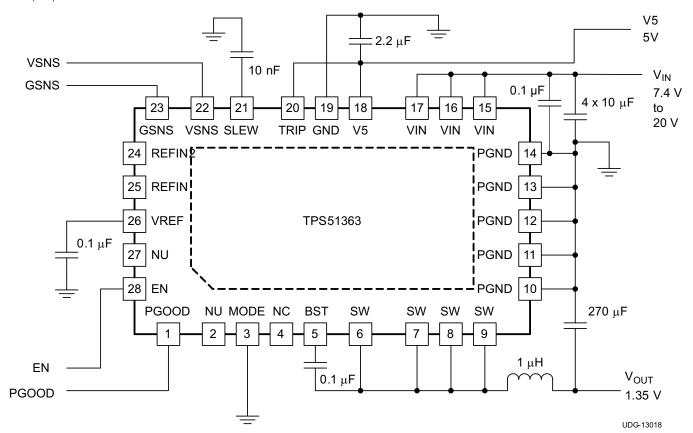

## Design 2:

This design is a DDR3L, VDDQ, application with an output voltage of 1.35 V, maximum processor current  $(I_{CC(max)})$  of 8 A, an OCL of 12 A, and a switching frequency of 400 kHz.

Figure 33. Design 2: Application Schematic

| REFERENCE<br>DESIGNATOR | QTY | SPECIFICATION | MANUFACTURER | PART NUMBER       |  |  |

|-------------------------|-----|---------------|--------------|-------------------|--|--|

| C <sub>IN</sub>         | 4   | 10 µF, 25 V   | Taiyo Yuden  | TMK325BJ106MM     |  |  |

| C <sub>OUT</sub>        | 1   | 270 µF, 2 V   | Panasonic    | 2TPSF270M6E       |  |  |

| L <sub>OUT</sub>        | 1   | 1 μH, 6.7 mΩ  | Cyntec       | PIMB063T-1R0MS-63 |  |  |

#### Table 6. Design 2: List of Materials

## **REVISION HISTORY**

NOTE: Page numbers of current version may differ from previous versions.

| C | hanges from Original (February 2013) to Revision A                                                                                                                                                                                                                                                                                                                                                                                                      | Page |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Added MIN and MAX values to I <sub>OCL</sub> spec in Elec Char table                                                                                                                                                                                                                                                                                                                                                                                    | 5    |

| • | Changed the Functional Block Diagram $V_{REFIN}$ signal line identifier on the UV-detect device from " $V_{REFIN - 32\%}$ " to " $V_{REFIN - 34\%}$ ". Changed signal line identifier on the high-side comparator from " $V_{REFIN}$ + 8/20%" to " $V_{REFIN}$ + 20%". Changed the high-side device symbol from hysteresis to a comparator. Changed signal line identifier on the low-side device from " $V_{REFIN}$ - 8/32%" to " $V_{REFIN}$ - 8/34%. | 8    |

| • | Added Land pads for a 0.1-µF capacitor between VIN and PGND of the TPS51363 Design Layout figure                                                                                                                                                                                                                                                                                                                                                        | 21   |

| • | Added a 0.1-µF capacitor symbol between VIN and PGND of the Design 1: Application Schematic.                                                                                                                                                                                                                                                                                                                                                            | 22   |

| • | Changed L <sub>OUT</sub> inductor part number from PIMB063T to PIMB063T-R68MS-63 in Design 1: List of Materials table.                                                                                                                                                                                                                                                                                                                                  | 22   |

| • | Changed text from "LPDDR3" to "DDR3L" in Design 2 description section.                                                                                                                                                                                                                                                                                                                                                                                  | 23   |

| • | Added 0.1 µF capacitor symbol between VIN and PGND in Design 2: Application Schematic figure                                                                                                                                                                                                                                                                                                                                                            | 23   |

| • | Changed L <sub>OUT</sub> inductor spec from 1 $\mu$ H, 6.5 m $\Omega$ to 6.7 m $\Omega$ , and part number from PCME063T to PIMB063T-<br>1R0MS-63 in Design 2: List of Materials table.                                                                                                                                                                                                                                                                  | 23   |

10-Dec-2020

## PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2)        | Lead finish/<br>Ball material | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|------------------------|-------------------------------|----------------------|--------------|-------------------------|---------|

|                  |               |              |                    |      |                |                        | (6)                           |                      |              |                         |         |

| TPS51363RVER     | ACTIVE        | VQFN-CLIP    | RVE                | 28   | 3000           | RoHS-Exempt<br>& Green | NIPDAU   SN                   | Level-2-260C-1 YEAR  | -10 to 85    | TPS51363                | Samples |

| TPS51363RVET     | ACTIVE        | VQFN-CLIP    | RVE                | 28   | 250            | RoHS-Exempt<br>& Green | NIPDAU   SN                   | Level-2-260C-1 YEAR  | -10 to 85    | TPS51363                | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <= 1000ppm threshold. Antimony trioxide based flame retardants must also meet the <= 1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

# PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

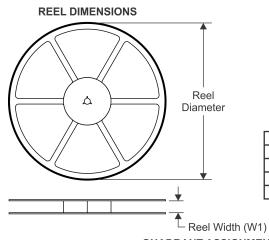

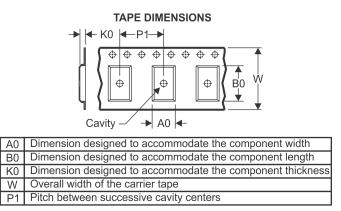

## TAPE AND REEL INFORMATION

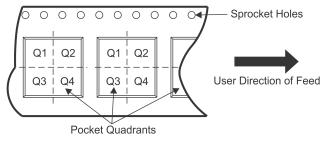

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device       |               | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadran |

|--------------|---------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|-----------------|

| TPS51363RVER | VQFN-<br>CLIP | RVE                | 28 | 3000 | 330.0                    | 12.4                     | 3.71       | 4.71       | 1.1        | 8.0        | 12.0      | Q1              |

| TPS51363RVER | VQFN-<br>CLIP | RVE                | 28 | 3000 | 330.0                    | 12.4                     | 3.8        | 4.8        | 1.18       | 8.0        | 12.0      | Q1              |

| TPS51363RVET | VQFN-<br>CLIP | RVE                | 28 | 250  | 180.0                    | 12.4                     | 3.8        | 4.8        | 1.18       | 8.0        | 12.0      | Q1              |

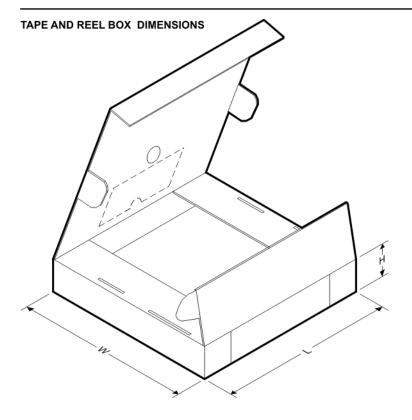

# PACKAGE MATERIALS INFORMATION

13-Mar-2022

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS51363RVER | VQFN-CLIP    | RVE             | 28   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS51363RVER | VQFN-CLIP    | RVE             | 28   | 3000 | 367.0       | 367.0      | 38.0        |

| TPS51363RVET | VQFN-CLIP    | RVE             | 28   | 250  | 213.0       | 191.0      | 35.0        |

# **MECHANICAL DATA**

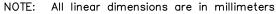

- C. Quad Flatpack, No-leads (QFN) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions. E. Falls within JEDEC MO-220.

# RVE (R-PVQFN-N28)

## PLASTIC QUAD FLATPACK NO-LEAD

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

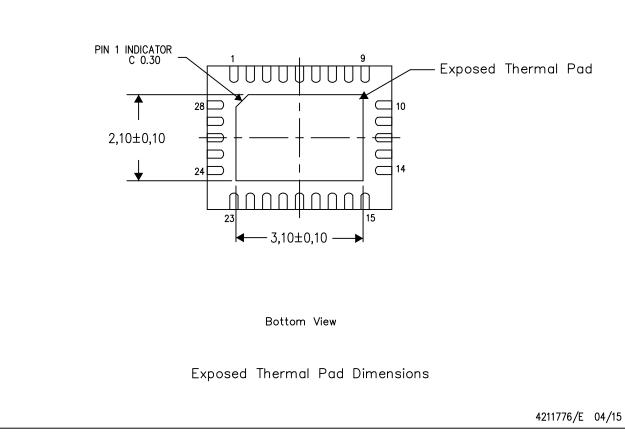

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat-Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Electroformed stencils offer adequate release at thicker values/lower Area Ratios. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- E. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated