TPS70745, TPS70748 TPS70751, TPS70758 TPS70702

SLVS291D-MAY 2000-REVISED DECEMBER 2007

# Dual-Output, Low Dropout Voltage Regulators with Power-Up Sequencing for Split-Voltage DSP Systems

# FEATURES

- Dual Output Voltages for Split-Supply Applications

- Selectable Power-Up Sequencing for DSP Applications (See Part Number TPS708xx for Independent Enable Outputs)

- Output Current Range of 250mA on Regulator 1 and 125mA on Regulator 2

- Fast Transient Response

- Voltage Options: 3.3V/2.5V, 3.3V/1.8V, 3.3V/1.5V, 3.3V/1.2V, and Dual Adjustable Outputs

- Open Drain Power-On Reset with 120ms Delay

- Open Drain Power Good for Regulator 1

- Ultralow 190µA (typ) Quiescent Current

- 1µA Input Current During Standby

- Low Noise: 65µV<sub>RMS</sub> Without Bypass Capacitor

- Quick Output Capacitor Discharge Feature

- Two Manual Reset Inputs

- 2% Accuracy Over Load and Temperature

- Undervoltage Lockout (UVLO) Feature

- 20-Pin PowerPAD<sup>™</sup> TSSOP Package

- Thermal Shutdown Protection

# DESCRIPTION

TPS707xx family devices are designed to provide a complete power management solution for the TMS320<sup>™</sup> DSP family, processor power, ASIC, FPGA, and digital applications where dual output voltage regulators are required. Easy programmability of the sequencing function makes the TPS707xx family ideal for any TMS320 DSP applications with power sequencing requirements. Differentiated features, such as accuracy, fast transient response, SVS supervisory circuit, manual reset inputs, and an enable function, provide a complete system solution.

The TPS707xx family of voltage regulators offer very low dropout voltage and dual outputs with power-up sequence control, which is designed primarily for DSP applications. These devices have extremely low noise output performance without using any added filter bypass capacitors and are designed to have a fast transient response and be stable with  $10\mu$ F low ESR capacitors.

These devices have fixed 3.3V/2.5V, 3.3V/1.8V, 3.3V/1.5V, 3.3V/1.2V, and adjustable/adjustable voltage options. Regulator 1 can support up to 250mA, and regulator 2 can support up to 125mA. Separate voltage inputs allow the designer to configure the source power.

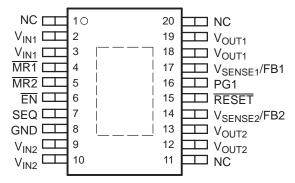

PWP PACKAGE (TOP VIEW)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD, TMS320 are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

# TPS70745, TPS70748 TPS70751, TPS70758 TPS70702

SLVS291D-MAY 2000-REVISED DECEMBER 2007

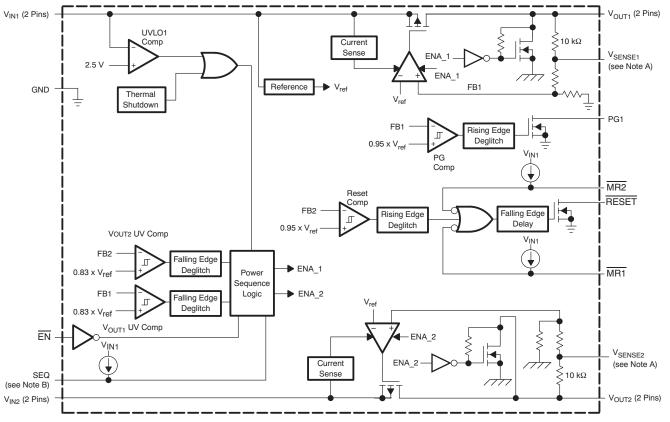

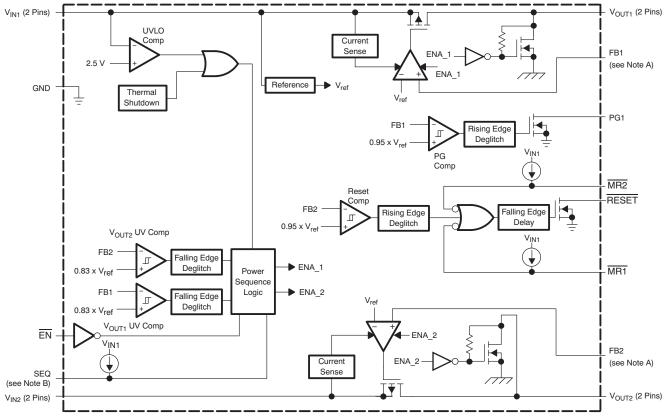

Because the PMOS device behaves as a low-value resistor, the dropout voltage is very low (typically 83mV on regulator 1) and is directly proportional to the output current. Additionally, because the PMOS pass element is a voltage-driven device, the quiescent current is very low and independent of output loading (maximum of  $230\mu$ A over the full range of output current). This LDO family also features a sleep mode; applying a high signal to EN (enable) shuts down both regulators, reducing the input current to  $1\mu$ A at  $T_{\rm u}$  = +25°C.

The device is enabled when the  $\overline{EN}$  pin is connected to a low-level input voltage. The output voltages of the two regulators are sensed at the V<sub>SENSE1</sub> and V<sub>SENSE2</sub> pins, respectively.

The input signal at the SEQ pin controls the power-up sequence of the two regulators. When the device is enabled and the SEQ terminal is pulled high or left open,  $V_{OUT2}$  turns on first and  $V_{OUT1}$  remains off until  $V_{OUT2}$  reaches approximately 83% of its regulated output voltage. At that time  $V_{OUT1}$  is turned on. If  $V_{OUT2}$  is pulled below 83% (for example, an overload condition),  $V_{OUT1}$  is turned off. Pulling the SEQ terminal low reverses the power-up order and  $V_{OUT1}$  is turned on first. The SEQ pin is connected to an internal pull-up current source.

For each regulator, there is an internal discharge transistor to discharge the output capacitor when the regulator is turned off (disabled).

The PG1 pin reports the voltage conditions at  $V_{OUT1}$ , which can be used to implement an SVS for the circuitry supplied by regulator 1.

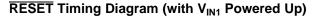

The TPS707xx features a RESET (SVS, POR, or Power-On Reset). RESET output initiates a reset in DSP systems and related digital applications in the event of an undervoltage condition. RESET indicates the status of  $V_{OUT2}$  and both manual reset pins (MR1 and MR2). When  $V_{OUT2}$  reaches 95% of its regulated voltage and MR1 and MR2 are in the logic high state, RESET goes to a high impedance state after a 120ms delay. RESET goes to the logic low state when the  $V_{OUT2}$  regulated output voltage is pulled below 95% (for example, an overload condition) of its regulated voltage. To monitor  $V_{OUT1}$ , the PG1 output pin can be connected to MR1 or MR2.

The device has an undervoltage lockout (UVLO) circuit that prevents the internal regulators from turning on until  $V_{IN1}$  reaches 2.5V.

2

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

|           | VOLTAGE (V) <sup>(2)</sup> |                   | PACKAGE- SPECIFIED   |                                        |                    |                              |

|-----------|----------------------------|-------------------|----------------------|----------------------------------------|--------------------|------------------------------|

| PRODUCT   | V <sub>OUT1</sub>          | V <sub>OUT2</sub> | LEAD<br>(DESIGNATOR) | TEMPERATURE<br>RANGE (T <sub>J</sub> ) | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

| TPS70702  | Adjustable                 | Adjustable        | HTSSOP-24 (PWP)      | -40°C to +125°C                        | TPS70702PWP        | Tube, 70                     |

| 11-370702 | Aujustable                 | Aujustable        | H1330F-24 (FWF)      | -40 C 10 +125 C                        | TPS70702PWPR       | Tape and Reel, 2000          |

| TD070746  | 3.3 V                      | 1.2 V             | HTSSOP-24 (PWP)      | -40°C to +125°C                        | TPS70745PWP        | Tube, 70                     |

| TPS70745  | 3.3 V                      | 1.2 V             | П1330F-24 (FWF)      | -40°C 10 +125°C                        | TPS70745PWPR       | Tape and Reel, 2000          |

| TPS70748  | 2.2.1/                     | 1.5 V             |                      | -40°C to +125°C                        | TPS70748PWP        | Tube, 70                     |

| 1P570746  | 3.3 V                      | 1.5 V             | HTSSOP-24 (PWP)      | -40°C 10 +125°C                        | TPS70748PWPR       | Tape and Reel, 2000          |

| TD070754  | 2.2.1/                     | 1.0.\/            |                      | -40°C to +125°C                        | TPS70751PWP        | Tube, 70                     |

| TPS70751  | 3.3 V                      | V 1.8 V           | HTSSOP-24 (PWP)      | -40°C 10 +125°C                        | TPS70751PWPR       | Tape and Reel, 2000          |

| TD070750  | 2.2.1/                     | 0.5.1/            |                      | 4000 to 140500                         | TPS70758PWP        | Tube, 70                     |

| TPS70758  | 3.3 V 2.5 V                |                   | HTSSOP-24 (PWP)      | -40°C to +125°C                        | TPS70758PWPR       | Tape and Reel, 2000          |

### **ORDERING INFORMATION**<sup>(1)</sup>

For the most current package and ordering information see the Package Option Addendum located at the end of this document, or see (1) the TI web site at www.ti.com.

For fixed 1.20V operation, tie FB to OUT. (2)

### **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                                         | TPS707xx                | UNIT  |

|-------------------------------------------------------------------------|-------------------------|-------|

| Input voltage range: V <sub>IN1</sub> , V <sub>IN2</sub> <sup>(2)</sup> | -0.3 to +7              | V     |

| Voltage range at EN                                                     | -0.3 to +7              | V     |

| Output voltage range (V <sub>OUT1</sub> , V <sub>SENSE1</sub> )         | 5.5                     | V     |

| Output voltage range (V <sub>OUT2</sub> , V <sub>SENSE2</sub> )         | 5.5                     | V     |

| Maximum RESET, PG1 voltage                                              | 7                       | V     |

| Maximum MR1, MR2, and SEQ voltage                                       | V <sub>IN1</sub>        | V     |

| Peak output current                                                     | Internally limited      |       |

| Continuous total power dissipation                                      | See Dissipation Ratings | Table |

| Junction temperature range, T <sub>J</sub>                              | -40 to +150             | °C    |

| Storage temperature range, T <sub>stg</sub>                             | -65 to +150             | °C    |

| ESD rating, HBM                                                         | 2                       | kV    |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

All voltages are tied to network ground. (2)

## **DISSIPATION RATINGS**

| PACKAGE            | AIR FLOW (CFM) | T <sub>A</sub> ≤ +25°C | DERATING<br>FACTOR | T <sub>A</sub> = +70°C | T <sub>A</sub> = +85°C |

|--------------------|----------------|------------------------|--------------------|------------------------|------------------------|

| PWP <sup>(1)</sup> | 0              | 3.067W                 | 30.67mW/°C         | 1.687W                 | 1.227W                 |

| FV/PV/             | 250            | 4.115W                 | 41.15mW/°C         | 2.265W                 | 1.646W                 |

(1) This parameter is measured with the recommended copper heat sink pattern on a 4-layer PCB, 1 oz. copper on a 4-in by 4-in ground layer. For more information, refer to TI technical brief SLMA002.

# **RECOMMENDED OPERATING CONDITIONS**

Over operating temperature range (unless otherwise noted).

|                                                | MIN  | MAX  | UNIT |

|------------------------------------------------|------|------|------|

| Input voltage, $V_1^{(1)}$ (regulator 1 and 2) | 2.7  | 6    | V    |

| Output current, I <sub>O</sub> (regulator 1)   | 0    | 250  | mA   |

| Output current, I <sub>O</sub> (regulator 2)   | 0    | 125  | mA   |

| Output voltage range (for adjustable option)   | 1.22 | 5.5  | V    |

| Operating junction temperature, T <sub>J</sub> | -40  | +125 | °C   |

(1) To calculate the minimum input voltage for maximum output current, use the following equation:  $V_{I(min)} = V_{O(max)} + V_{DO(max load)}$ .

# **ELECTRICAL CHARACTERISTICS**

Over recommended operating junction temperature range ( $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ),  $V_{IN1}$  or  $V_{IN2} = V_{OUT(nom)} + 1V$ ,  $I_O = 1mA$ ,  $\overline{EN} = 0V$ , and  $C_O = 33\mu F$  (unless otherwise noted).

| PARAMETER                                                                                   |                                                   |                                    | TEST CO                                    | ONDITIONS                               | MIN   | TYP   | MAX   | UNIT          |

|---------------------------------------------------------------------------------------------|---------------------------------------------------|------------------------------------|--------------------------------------------|-----------------------------------------|-------|-------|-------|---------------|

|                                                                                             |                                                   | Reference                          | $2.7V < V_1 < 6V,$<br>$T_J = +25^{\circ}C$ | FB connected to $\mathrm{V}_\mathrm{O}$ |       | 1.22  |       |               |

|                                                                                             |                                                   | voltage                            | 2.7V < V <sub>I</sub> < 6V,                | FB connected to V <sub>O</sub>          | 1.196 |       | 1.244 |               |

|                                                                                             |                                                   | 2.7V < V <sub>I</sub> < 6V,        | $T_J = +25^{\circ}C$                       |                                         | 1.2   |       |       |               |

|                                                                                             |                                                   | 1.2V Output                        | 2.7V < V <sub>I</sub> < 6V,                |                                         | 1.176 |       | 1.224 |               |

|                                                                                             |                                                   |                                    | 2.7V < V <sub>I</sub> < 6V,                | $T_J = +25^{\circ}C$                    |       | 1.5   |       |               |

| Vo                                                                                          | Output<br>voltage <sup>(1), (2)</sup>             | 1.5V Output                        | 2.7V < V <sub>I</sub> < 6V,                |                                         | 1.47  |       | 1.53  | V             |

| 0                                                                                           | voltage                                           | 1.0\/ Output                       | 2.8V < V <sub>I</sub> < 6V,                | $T_J = +25^{\circ}C$                    |       | 1.8   |       |               |

|                                                                                             |                                                   | 1.8V Output                        | 2.8V < V <sub>I</sub> < 6V,                |                                         | 1.764 |       | 1.836 |               |

|                                                                                             |                                                   |                                    | 3.5V < V <sub>I</sub> < 6V,                | $T_J = +25^{\circ}C$                    |       | 2.5   |       |               |

|                                                                                             |                                                   | 2.5V Output                        | 3.5V < V <sub>I</sub> < 6V,                |                                         | 2.45  |       | 2.55  |               |

|                                                                                             |                                                   |                                    | $4.3V < V_{\rm I} < 6V,$                   | $T_J = +25^{\circ}C$                    |       | 3.3   |       |               |

|                                                                                             |                                                   | 3.3V Output                        | $4.3V < V_{\rm I} < 6V$ ,                  |                                         | 3.234 |       | 3.366 |               |

| Quiescent current (GND current) for regulator 1 and regulator 2, $\overline{EN} = 0V^{(1)}$ |                                                   | (2)                                | $T_J = +25^{\circ}C$                       |                                         | 190   |       | •     |               |

|                                                                                             |                                                   | (2)                                |                                            |                                         | 23    |       | μA    |               |

| Output vo                                                                                   | Output voltage line regulation $(\Delta V_0/V_0)$ |                                    | $V_{O} + 1V < V_{I} \le 6V,$               | $T_{\rm J} = +25^{\circ}C^{(1)}$        |       | 0.01% |       | V             |

| for regulat                                                                                 | tor 1 and regula                                  | tor 2 $(3)$                        | $V_{O} + 1V < V_{I} \le 6V$                | (1)                                     |       |       | 0.1%  | V             |

| Load regu                                                                                   | lation for V <sub>OUT</sub>                       | <sub>1</sub> and V <sub>OUT2</sub> | T <sub>J</sub> = +25°C                     | (2)                                     |       | 1     |       | mV            |

| V <sub>n</sub>                                                                              | Output noise                                      | Regulator 1                        |                                            |                                         |       | 65    |       |               |

|                                                                                             | voltage                                           | Regulator 2                        | BW = 300Hz  to  50kHz,                     | $C_0 = 33\mu F, T_J = +25^{\circ}C$     |       | 65    |       | $\mu V_{RMS}$ |

| <b>.</b>                                                                                    |                                                   | Regulator 1                        | N/ 01/                                     |                                         |       | 1.6   | 1.9   |               |

| Output cu                                                                                   | rrent limit                                       | Regulator 2                        | V <sub>OUT</sub> = 0V                      |                                         |       | 0.750 | 1     | μA            |

| Thermal s                                                                                   | shutdown junctio                                  | on temperature                     |                                            |                                         |       | +150  |       | °C            |

|                                                                                             |                                                   |                                    | $\overline{EN} = V_I$ ,                    | T <sub>J</sub> = +25°C                  |       |       | 2     |               |

| Ь                                                                                           | Standby                                           | Regulator 1                        | $\overline{EN} = V_I$                      |                                         |       |       | 6     | μA            |

| (standby)                                                                                   |                                                   |                                    | ĒN = V <sub>I</sub> ,                      | $T_J = +25^{\circ}C$                    |       |       | 2     |               |

|                                                                                             |                                                   | Regulator 2                        | ĒN = V <sub>I</sub>                        |                                         |       |       | 6     | μA            |

| PSRR                                                                                        | Power-supply rejection                            | ripple                             | $f = 1 kHz, C_0 = 33 \mu F,$               | $T_{J} = +25^{\circ}C^{(1)}$            |       | 60    |       | dB            |

Minimum input operating voltage is 2.7V or V<sub>O(typ)</sub> + 1V, whichever is greater. Maximum input voltage = 6V, minimum output current = 1mA.

(2)  $I_0 = 1mA$  to 250mA for Regulator 1 and 1mA to 125mA for Regulator 2.

(3) If

$$V_0 < 1.8V$$

then  $V_{Imax} = 6V$ ,  $V_{Imin} = 2.7V$ : Line Reg. (mV) =  $(\%/V) \times V_0 \frac{(V_{Imax} - 2.7V)}{100} \times 1000$

If  $V_0 > 2.5V$  then  $V_{Imax} = 6V$ ,  $V_{Imin} = V_0 + 1V$ : Line Reg. (mV) =  $(\%/V) \times V_0 \frac{(V_{Imax} - (V_0 + 1V))}{100} \times 1000$

4

# ELECTRICAL CHARACTERISTICS (continued)

Over recommended operating junction temperature range ( $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ),  $V_{IN1}$  or  $V_{IN2} = V_{OUT(nom)} + 1V$ ,  $I_O = 1mA$ ,  $\overline{EN} = 0V$ , and  $C_O = 33\mu F$  (unless otherwise noted).

| PARAMETER                                                                                                  | TES                             | T CONDITIONS                | MIN                | TYP                | MAX                | UNIT             |

|------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------|--------------------|--------------------|--------------------|------------------|

| RESET Terminal                                                                                             | 1                               |                             |                    |                    |                    |                  |

| Minimum input voltage for valid RESET                                                                      | Ι <sub>RESET</sub> = 300μΑ,     | V <sub>(RESET)</sub> ≤ 0.8V |                    | 1.0                | 1.3                | V                |

| Trip threshold voltage                                                                                     | V <sub>O</sub> decreasing       |                             | 92%                | 95%                | 98%                | V <sub>OUT</sub> |

| Hysteresis voltage                                                                                         | Measured at V <sub>O</sub>      |                             |                    | 0.5%               |                    | V <sub>OUT</sub> |

| t(RESET)                                                                                                   | RESET pulse duration            | ו                           | 80                 | 120                | 160                | ms               |

| t <sub>r(RESET)</sub>                                                                                      | Rising edge deglitch            |                             |                    | 30                 |                    | μs               |

| Output low voltage                                                                                         | V <sub>I</sub> = 3.5V,          | I <sub>O(RESET)</sub> = 1mA |                    | 0.15               | 0.4                | V                |

| Leakage current                                                                                            | V <sub>(RESET)</sub> = 6V       |                             |                    |                    | 1                  | μΑ               |

| PG1 Terminal                                                                                               |                                 |                             |                    |                    |                    |                  |

| Minimum input voltage for valid PG1                                                                        | I <sub>(PG1)</sub> = 300μA,     | V <sub>(PG1)</sub> ≤ 0.8V   |                    | 1.0                | 1.3                | V                |

| Trip threshold voltage                                                                                     | V <sub>O</sub> decreasing       |                             | 92%                | 95%                | 98%                | V <sub>OUT</sub> |

| Hysteresis voltage                                                                                         | Measured at V <sub>O</sub>      |                             |                    | 0.5%               |                    | V <sub>OUT</sub> |

| t <sub>f(PG1)</sub>                                                                                        | Falling edge deglitch           |                             |                    | 30                 |                    | μs               |

| Output low voltage                                                                                         | $V_{I} = 2.7V,$                 | $I_{O(PG1)} = 1mA$          |                    | 0.15               | 0.4                | V                |

| Leakage current                                                                                            | $V_{(PG1)} = 6V$                |                             |                    |                    | 1                  | μA               |

| EN Terminal                                                                                                |                                 |                             |                    |                    |                    |                  |

| High level EN input voltage                                                                                |                                 |                             | 2                  |                    |                    | V                |

| Low level EN input voltage                                                                                 |                                 |                             |                    |                    | 0.7                | V                |

| Input current (EN)                                                                                         |                                 |                             | -1                 |                    | 1                  | μA               |

| SEQ Terminal                                                                                               |                                 |                             |                    |                    |                    |                  |

| High level SEQ input voltage                                                                               |                                 |                             | 2                  |                    |                    | V                |

| Low level SEQ input voltage                                                                                |                                 |                             |                    |                    | 0.7                | V                |

| Falling edge delay                                                                                         | Measured at $V_{O}$             |                             |                    | 140                |                    | μs               |

| SEQ pull-up current source                                                                                 |                                 |                             |                    | 6                  |                    | μΑ               |

| MR1 / MR2 Terminals                                                                                        |                                 |                             |                    |                    |                    |                  |

| High level input voltage                                                                                   |                                 |                             | 2                  |                    |                    | V                |

| Low level input voltage                                                                                    |                                 |                             |                    |                    | 0.7                | V                |

| Pull-up current source                                                                                     |                                 |                             |                    | 6                  |                    | μA               |

| V <sub>OUT2</sub> Terminal                                                                                 |                                 |                             |                    |                    |                    |                  |

| $V_{\text{OUT2}}$ UV comparator: Positive-going input threshold voltage of $V_{\text{OUT2}}$ UV comparator |                                 |                             | 80% V <sub>O</sub> | 83% V <sub>O</sub> | 86% V <sub>O</sub> | V                |

| V <sub>OUT2</sub> UV comparator: Falling edge deglitch                                                     | V <sub>SENSE_2</sub> decreasing | below threshold             |                    | 140                |                    | μs               |

| Peak output current                                                                                        | 2ms pulse width                 |                             |                    | 375                |                    | mA               |

| Discharge transistor current                                                                               | V <sub>OUT2</sub> = 1.5V        |                             |                    | 7.5                |                    | mA               |

### **ELECTRICAL CHARACTERISTICS (continued)**

Over recommended operating junction temperature range ( $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ),  $V_{IN1}$  or  $V_{IN2} = V_{OUT(nom)} + 1V$ ,  $I_O = 1mA$ ,  $\overline{EN} = 0V$ , and  $C_O = 33\mu F$  (unless otherwise noted).

| PARAMETER                                                                                                  | TEST CONDITIONS                                                              | MIN TY                   | P MAX                             | UNIT |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------|-----------------------------------|------|

| V <sub>OUT1</sub> Terminal                                                                                 |                                                                              |                          |                                   |      |

| $V_{\text{OUT1}}$ UV comparator: Positive-going input threshold voltage of $V_{\text{OUT1}}$ UV comparator |                                                                              | 80% V <sub>O</sub> 83% \ | ∕ <sub>O</sub> 86% V <sub>O</sub> | V    |

| V <sub>OUT1</sub> UV comparator: Hysteresis                                                                |                                                                              | 0.5% \                   | ′o                                | mV   |

| V <sub>OUT1</sub> UV comparator: Falling edge deglitch                                                     | V <sub>SENSE_1</sub> decreasing below threshold                              | 14                       | 10                                | μs   |

| Dropout voltage <sup>(4)</sup>                                                                             | $I_{O} = 250 \text{mA}, T_{J} = +25^{\circ}\text{C}$ $V_{IN1} = 3.2\text{V}$ | 8                        | 33                                | mV   |

| Dropout voltage <sup>(4)</sup>                                                                             | I <sub>O</sub> = 250mA, V <sub>IN1</sub> = 3.2V                              |                          | 140                               | mV   |

| Peak output current <sup>(4)</sup>                                                                         | 2ms pulse width                                                              | 75                       | 50                                | mA   |

| Discharge transistor current                                                                               | V <sub>OUT1</sub> = 1.5V                                                     | 7                        | .5                                | mA   |

| V <sub>IN1</sub> UVLO threshold                                                                            |                                                                              | 2.4                      | 2.65                              | V    |

| FB Terminal                                                                                                |                                                                              |                          |                                   |      |

| Input current: TPS70702                                                                                    | FB = 1.8V                                                                    |                          | 1                                 | μA   |

(4) Input voltage ( $V_{IN1}$  or  $V_{IN2}$ ) =  $V_{O(typ)}$  – 100mV. For 1.5V, 1.8V and 2.5V regulators, the dropout voltage is limited by input voltage range. The 3.3V regulator input is set to 3.2V to perform this test.

6

### DEVICE INFORMATION

**Fixed Voltage Version**

A. For most applications, V<sub>SENSE1</sub> and V<sub>SENSE2</sub> should be externally connected to V<sub>OUT</sub> as close as possible to the device. For other implementations, refer to SENSE terminal connection discussion in the *Application Information* section.

B. If the SEQ terminal is floating at the input, V<sub>OUT2</sub> powers up first.

# TPS70745, TPS70748 TPS70751, TPS70758 TPS70702

SLVS291D-MAY 2000-REVISED DECEMBER 2007

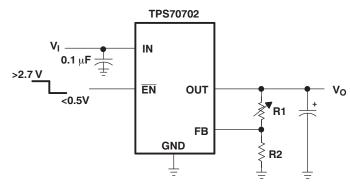

#### **Adjustable Voltage Version**

A. For most applications, FB1 and FB2 should be externally connected to resistor dividers as close as possible to the device. For other implementations, refer to FB terminals connection discussion in the *Application Information* section.

8

B. If the SEQ terminal is floating at the input, V<sub>OUT2</sub> powers up first

B.  $V_{IT}$  –Trip voltage is typically 5% lower than the output voltage (95%  $V_O$ )  $V_{IT-}$  to  $V_{IT+}$  is the hysteresis voltage.

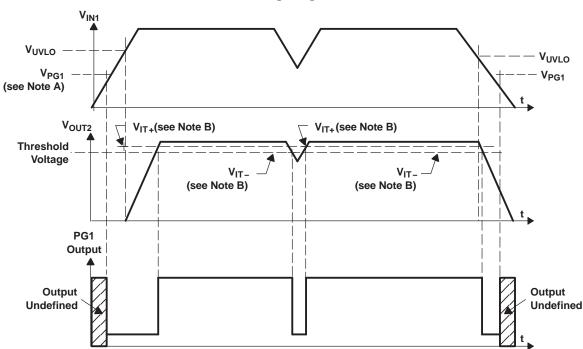

**PG1 Timing Diagram**

- NOTES: A. V<sub>PG1</sub> is the minimum input voltage for a valid PG1. The symbol V<sub>PG1</sub> is not currently listed within EIA or JEDEC standards for semiconductor symbology.

- B.  $V_{IT}$  –Trip voltage is typically 5% lower than the output voltage (95% V<sub>O</sub>) V<sub>IT</sub>- to V<sub>IT</sub>+ is the hysteresis voltage.

#### Table 1. TERMINAL FUNCTIONS

| TERMINAL                 |           | 1/0 | DECODIDITION                                                                                                                                    |

|--------------------------|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                     | NO.       | I/O | DESCRIPTION                                                                                                                                     |

| EN                       | 6         | I   | Active low enable                                                                                                                               |

| GND                      | 8         | —   | Ground                                                                                                                                          |

| MR1                      | 4         | I   | Manual reset input 1, active low, pulled up internally                                                                                          |

| MR2                      | 5         | I   | Manual reset input 2, active low, pulled up internally                                                                                          |

| NC                       | 1, 11, 20 | —   | No connection                                                                                                                                   |

| PG1                      | 16        | 0   | Open drain output, low when $V_{\text{OUT1}}$ voltage is less than 95% of the nominal regulated voltage                                         |

| RESET                    | 15        | 0   | Open drain output, SVS (power-on reset) signal, active low                                                                                      |

| SEQ                      | 7         | I   | Power-up sequence control: SEQ = High, $V_{OUT2}$ powers up first;<br>SEQ = Low, $V_{OUT1}$ powers up first, SEQ terminal pulled up internally. |

| V <sub>IN1</sub>         | 2, 3      | I   | Input voltage of regulator 1                                                                                                                    |

| V <sub>IN2</sub>         | 9, 10     | I   | Input voltage of regulator 2                                                                                                                    |

| V <sub>OUT1</sub>        | 18, 19    | 0   | Output voltage of regulator 1                                                                                                                   |

| V <sub>OUT2</sub>        | 12, 13    | 0   | Output voltage of regulator 2                                                                                                                   |

| V <sub>SENSE2</sub> /FB2 | 14        | I   | Regulator 2 output voltage sense/regulator 2 feedback for adjustable                                                                            |

| V <sub>SENSE1</sub> /FB1 | 17        | I   | Regulator 1 output voltage sense/regulator 1 feedback for adjustable                                                                            |

### **Detailed Description**

The TPS707xx low dropout regulator family provides dual regulated output voltages for DSP applications that require high-performance power management solutions. These devices provide fast transient response and high accuracy with small output capacitors, while drawing low quiescent current. Programmable sequencing provides a power solution for DSPs without any external component requirements. This architecture reduces the component cost and board space while increasing total system reliability. The TPS707xx family has an enable feature that puts the device in sleep mode, reducing the input currents to less than  $3\mu$ A. Other features are integrated SVS (Power-On Reset, RESET) and Power Good (PG1) that monitor output voltages and provide logic output to the system. These differentiated features provide a complete DSP power solution.

The TPS707xx, unlike many other LDOs, feature very low quiescent current that remains virtually constant even with varying loads. Conventional LDO regulators use a pnp pass element, the base current of which is directly proportional to the load current through the regulator ( $I_B = I_C/\beta$ ). The TPS707xx uses a PMOS transistor to pass current; because the gate of the PMOS is voltage=driven, operating current is low and stable over the full load range.

### **Pin Functions**

#### Enable

The EN terminal is an input that enables or shuts down the device. If EN is at a voltage high signal, the device is in shutdown mode. When EN goes to voltage low, the device is enabled.

#### Sequence

The SEQ terminal is an input that programs which output voltage ( $V_{OUT1}$  or  $V_{OUT2}$ ) turns on first. When the device is enabled and the SEQ terminal is pulled high or left open,  $V_{OUT2}$  turns on first and  $V_{OUT1}$  remains off until  $V_{OUT2}$  reaches approximately 83% of its regulated output voltage. At that time,  $V_{OUT1}$  is turned on. If  $V_{OUT2}$  is pulled below 83% (for example, in an overload condition)  $V_{OUT1}$  is turned off. These terminals have a 6-µA pullup current to  $V_{IN1}$ .

Pulling the SEQ terminal low reverses the power-up order and V<sub>OUT1</sub> is turned on first. For detailed timing diagrams, refer to Figure 36 through Figure 40.

#### Power-Good

The PG1 is an open drain, active high output terminal that indicates the status of the  $V_{OUT1}$  regulator. When the  $V_{OUT1}$  reaches 95% of its regulated voltage, PG1 goes to a high impedance state. It goes to a low impedance state when it is pulled below 95% (for example, doing an overload condition) of its regulated voltage. The open drain output of the PG1 terminal requires a pull-up resistor.

#### Manual Reset Pins (MR1 and MR2)

$\overline{\text{MR1}}$  and  $\overline{\text{MR2}}$  are active low input terminals used to trigger a reset condition. When either  $\overline{\text{MR1}}$  or  $\overline{\text{MR2}}$  is pulled to logic low, a POR (RESET) occurs. These terminals have a 6-µA pull-up current to V<sub>IN1</sub>.

#### Sense (V<sub>SENSE1</sub>, V<sub>SENSE2</sub>)

The sense terminals of fixed-output options must be connected to the regulator output, and the connection should be as short as possible. Internally, sense connects to high-impedance, wide-bandwidth amplifiers through a resistor-divider network and noise pickup feeds through to the regulator output. It is essential to route the sense connection in such a way to minimize or avoid noise pickup. Adding RC networks between the  $V_{\text{SENSE}}$  terminals and  $V_{\text{OUT}}$  terminals to filter noise is not recommended because these networks can cause the regulators to oscillate.

#### FB1 and FB2

FB1 and FB2 are input terminals used for adjustable-output devices and must be connected to the external feedback resistor divider. FB1 and FB2 connections should be as short as possible. It is essential to route them in such a way as to minimize or avoid noise pickup. Adding RC networks between the FB terminals and  $V_{OUT}$  terminals to filter noise is not recommended because these networks can cause the regulators to oscillate.

#### **RESET** Indicator

The TPS707xx features a RESET (SVS, POR, or Power-On Reset). RESET can be used to drive power-on reset circuitry or a low-battery indicator. RESET is an active low, open drain output that indicates the status of the  $V_{OUT2}$  regulator and both manual reset pins (MR1 and MR2). When  $V_{OUT2}$  exceeds 95% of its regulated voltage, and MR1 and MR2 are in the high impedance state, RESET goes to a high-impedance state after 120ms delay. RESET goes to a low-impedance state when  $V_{OUT2}$  is pulled below 95% (for example, an overload condition) of its regulated voltage. To monitor  $V_{OUT1}$ , the PG1 output pin can be connected to MR1 or MR2. The open drain output of the RESET terminal requires a pullup resistor. If RESET is not used, it can be left floating.

#### $V_{\text{IN1}}$ and $V_{\text{IN2}}$

$V_{IN1}$  and  $V_{IN2}$  are input to the regulators. Internal bias voltages are powered by  $V_{IN1}$ .

#### V<sub>OUT1</sub> and V<sub>OUT2</sub>

$V_{OUT1}$  and  $V_{OUT2}$  are output terminals of the LDO.

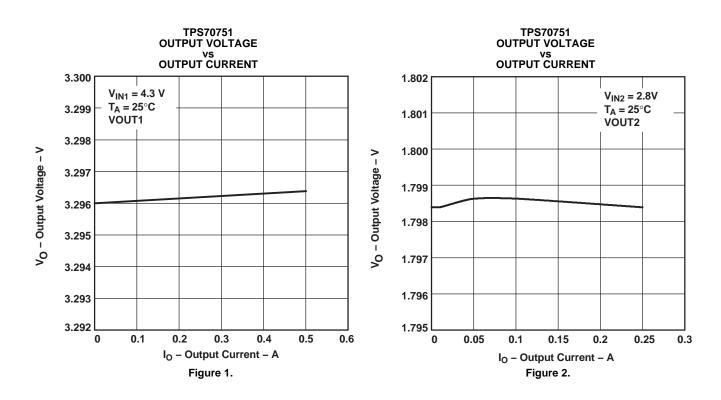

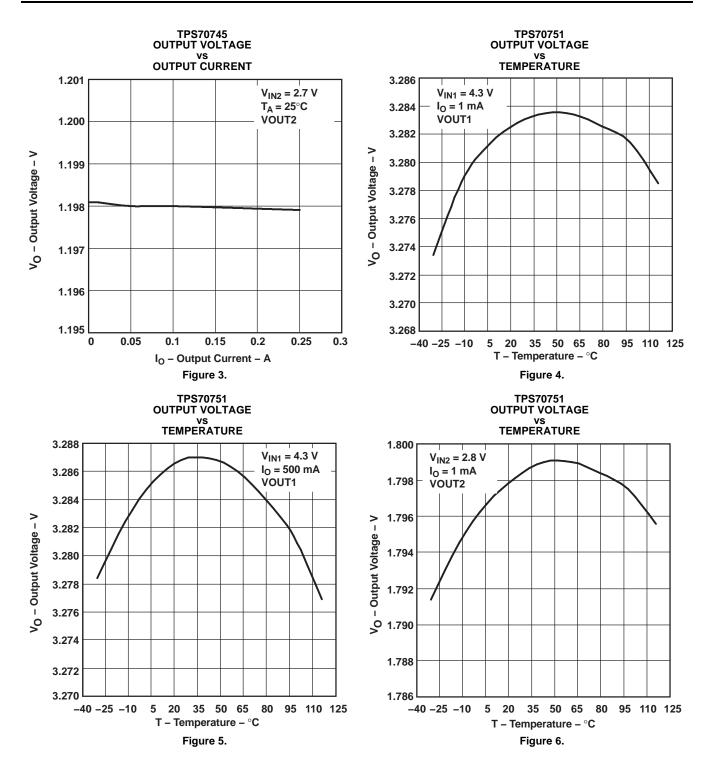

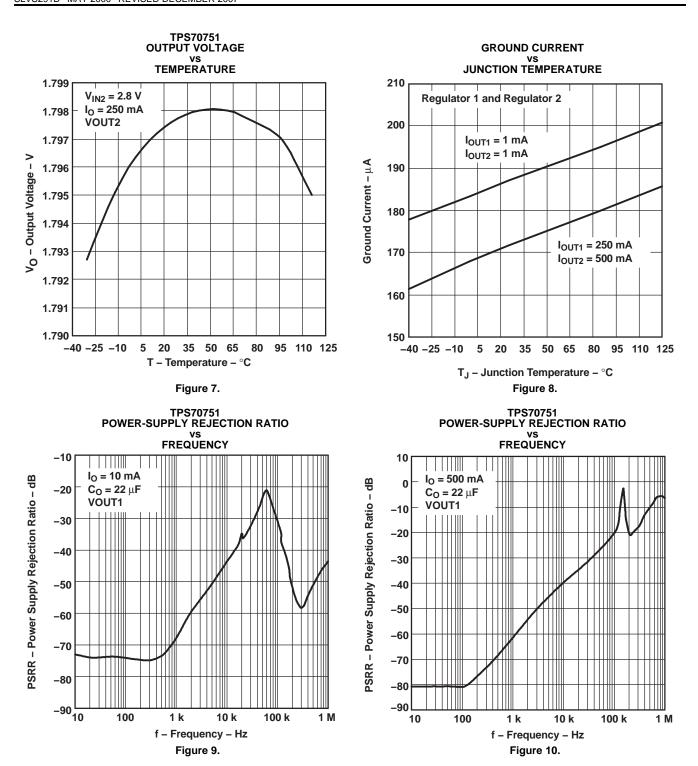

# **TYPICAL CHARACTERISTICS**

#### Table 2. Table of Graphs

|      |                                               |                         | FIGURE                  |

|------|-----------------------------------------------|-------------------------|-------------------------|

| M    | Output valtage                                | vs Output current       | Figure 1 to Figure 3    |

| Vo   | Output voltage                                | vs Temperature          | Figure 4 to Figure 7    |

|      | Ground current                                | vs Junction temperature | Figure 8                |

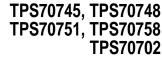

| PSRR | Power-supply rejection ratio                  | vs Frequency            | Figure 9 to Figure 12   |

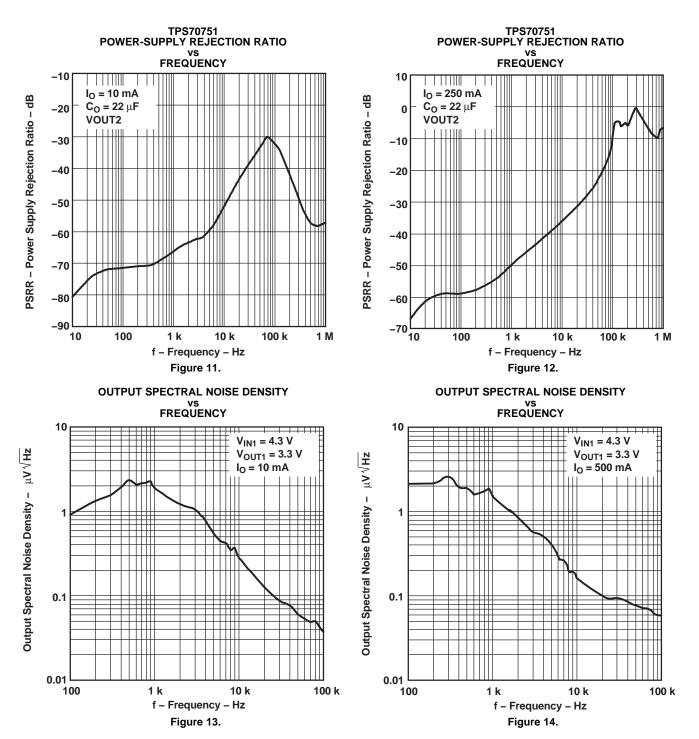

|      | Output spectral noise density                 | vs Frequency            | Figure 13 to Figure 16  |

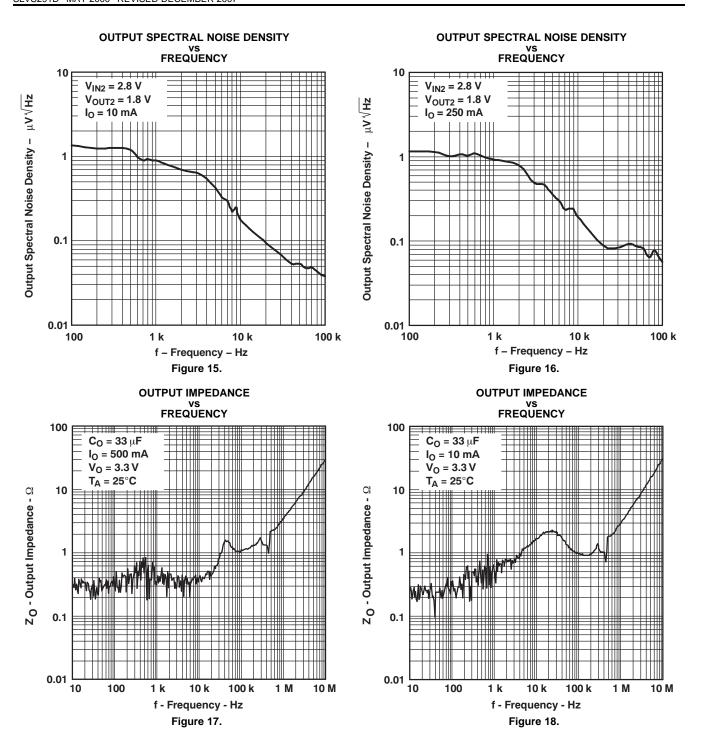

| Zo   | Output impedance                              | vs Frequency            | Figure 17 to Figure 20  |

|      | Dreneutusltere                                | vs Temperature          | Figure 21 and Figure 22 |

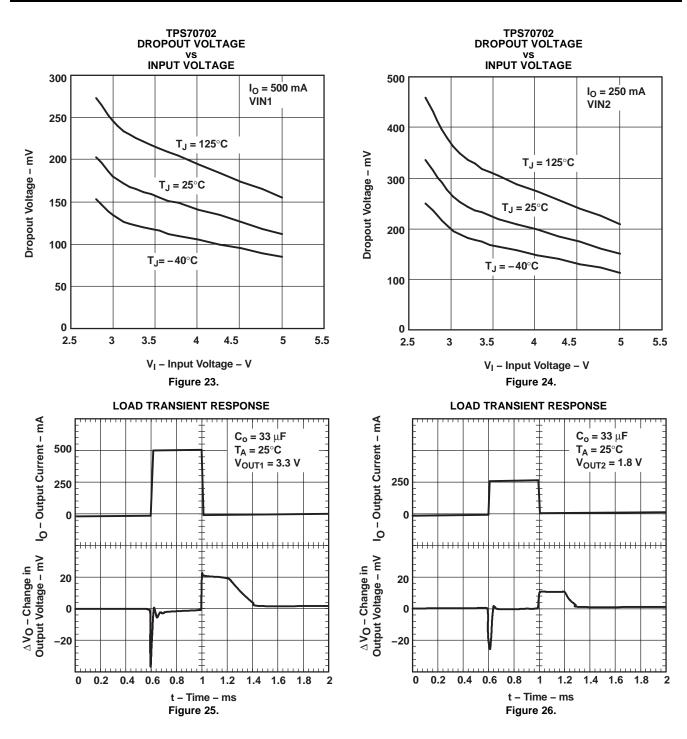

|      | Dropout voltage                               | vs Input voltage        | Figure 23 and Figure 24 |

|      | Load transient response                       |                         | Figure 25 and Figure 26 |

|      | Line transient response                       |                         | Figure 27 and Figure 28 |

| Vo   | Output voltage and enable voltage             | vs Time (start-up)      | Figure 29 and Figure 30 |

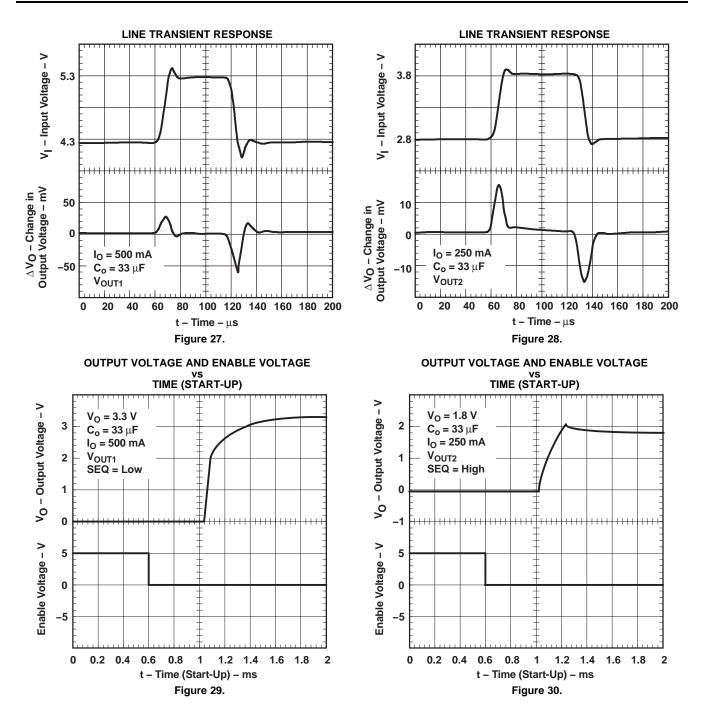

|      | Equivalent series resistance                  | vs Output current       | Figure 31 to Figure 34  |

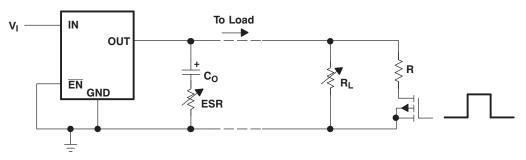

|      | Test circuit for typical regions of stability | Figure 35               |                         |

TEXAS TRUMENTS

www.ti.com

# TPS70745, TPS70748 TPS70751, TPS70758 TPS70702

SLVS291D-MAY 2000-REVISED DECEMBER 2007

<sup>(1)</sup> Equivalent series resistance (ESR) refers to the total series resistance, including the ESR of the capacitor, any series resistance added externally, and PWB trace resistance to  $C_0$ .

Figure 35. Test Circuit for Typical Regions of Stability

# **APPLICATION INFORMATION**

### **Sequencing Timing Diagrams**

This section provides a number of timing diagrams showing how this device functions in different configurations.

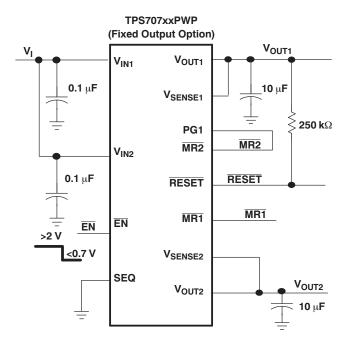

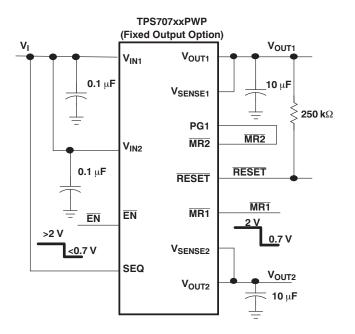

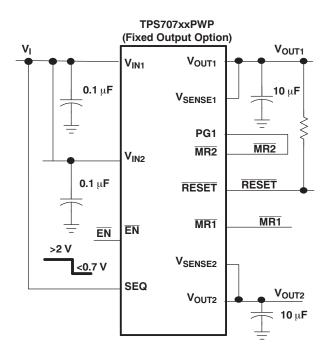

Application condition:  $V_{IN1}$  and  $V_{IN2}$  are tied to the same fixed input voltage greater than the  $V_{UVLO}$ ; SEQ is tied to logic low; PG1 is tied to MR2; MR1 is left unconnected and is therefore at logic high.

$\overline{\text{EN}}$  is initially high; therefore, both regulators are off and PG1 and  $\overline{\text{RESET}}$  are at logic low. With SEQ at logic low, when  $\overline{\text{EN}}$  is taken to logic low, V<sub>OUT1</sub> turns on. V<sub>OUT2</sub> turns on after V<sub>OUT1</sub> reaches 83% of its regulated output voltage. When V<sub>OUT1</sub> reaches 95% of its regulated output voltage, PG1 (tied to  $\overline{\text{MR2}}$ ) goes to logic high. When both V<sub>OUT1</sub> and V<sub>OUT2</sub> reach 95% of their respective regulated output voltages and both  $\overline{\text{MR1}}$  and  $\overline{\text{MR2}}$  (tied to PG1) are at logic high,  $\overline{\text{RESET}}$  is pulled to logic high after a 120ms delay. When  $\overline{\text{EN}}$  is returned to logic high, both devices power down and both PG1 (tied to  $\overline{\text{MR2}}$ ) and  $\overline{\text{RESET}}$ return to logic low.

Figure 36. Timing when SEQ = Low

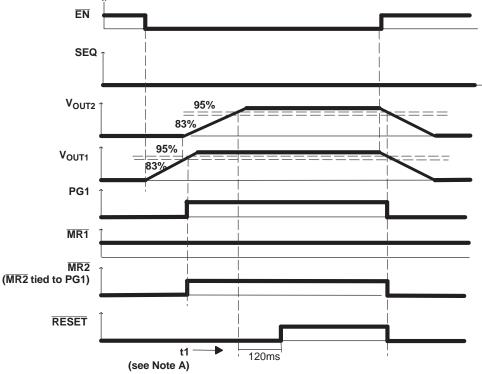

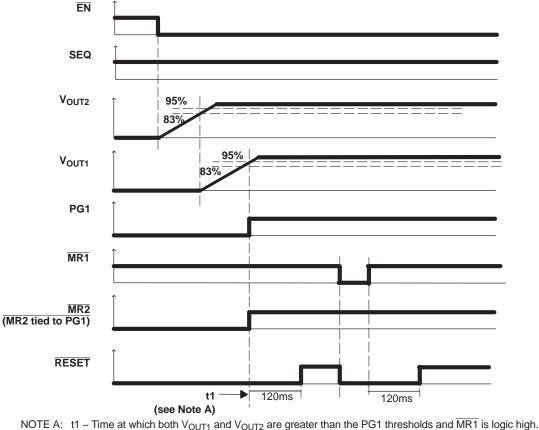

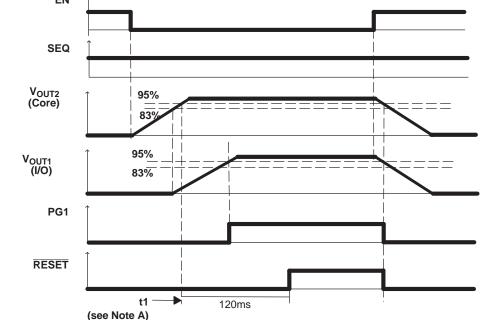

Application condition:  $V_{IN1}$  and  $V_{IN2}$  are tied to the same fixed input voltage greater than the  $V_{UVLO}$ ; SEQ is tied to logic high; PG1 is tied to MR2; MR1 is left unconnected and is therefore at logic high.

$\overline{\rm EN}$  is initially high; therefore, both regulators are off and PG1 and  $\overline{\rm RESET}$  are at logic low. With SEQ at logic high, when  $\overline{\rm EN}$  is taken to logic low, V<sub>OUT2</sub> turns on. V<sub>OUT1</sub> turns on after V<sub>OUT2</sub> reaches 83% of its regulated output voltage. When V<sub>OUT1</sub> reaches 95% of its regulated output voltage, PG1 (tied to  $\overline{\rm MR2}$ ) goes to logic high. When both V<sub>OUT1</sub> and V<sub>OUT2</sub> reach 95% of their respective regulated output voltages and both  $\overline{\rm MR1}$  and  $\overline{\rm MR2}$  (tied to PG1) are at logic high, RESET is pulled to logic high after a 120ms delay. When  $\overline{\rm EN}$  is returned to logic high, both devices turn off and both PG1 (tied to  $\overline{\rm MR2}$ ) and RESET return to logic low.

Figure 37. Timing when SEQ = High

# TPS70745, TPS70748 TPS70751, TPS70758 TPS70702

SLVS291D-MAY 2000-REVISED DECEMBER 2007

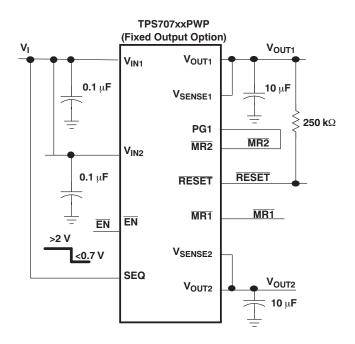

Application condition:  $V_{IN1}$  and  $VI_{N2}$  are tied to the same fixed input voltage greater than the  $V_{UVLO}$ ; SEQ is tied to logic high; PG1 is tied to MR2; MR1 is initially at logic high but is eventually toggled.

$\overline{\rm EN}$  is initially high; therefore, both regulators are off and PG1 and  $\overline{\rm RESET}$  are at logic low. With SEQ at logic high, when  $\overline{\rm EN}$  is taken low,  $V_{\rm OUT2}$  turns on.  $V_{\rm OUT1}$  turns on after  $V_{\rm OUT2}$  reaches 83% of its regulated output voltage. When  $V_{\rm OUT1}$  reaches 95% of its regulated output voltage, PG1 (tied to  $\overline{\rm MR2}$ ) goes to logic high. When both  $V_{\rm OUT1}$  and  $V_{\rm OUT2}$  reach 95% of their respective regulated output voltages and both  $\overline{\rm MR1}$  and  $\overline{\rm MR2}$  (tied to PG1) are at logic high,  $\overline{\rm RESET}$  is pulled to logic high after a 120ms delay. When  $\overline{\rm MR1}$  is taken low,  $\overline{\rm RESET}$  returns to logic low but the outputs remain in regulation. When  $\overline{\rm MR1}$  is returned to logic high, since both  $V_{\rm OUT1}$  and  $V_{\rm OUT2}$  remain above 95% of their respective regulated output voltages and  $\overline{\rm MR2}$  (tied to PG1) remains at logic high,  $\overline{\rm RESET}$  is pulled to logic high after a 120ms delay.

A:  $t_1 - t_1$  me at which both  $v_{OUT1}$  and  $v_{OUT2}$  are greater than the PG t thresholds and MR t is logic t

Figure 38. Timing when MR1 is Toggled

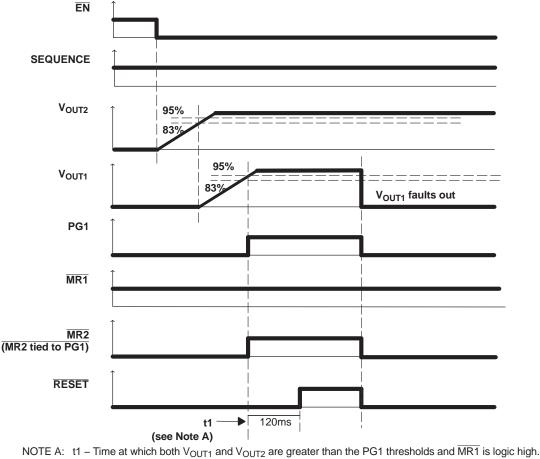

Application condition:  $V_{IN1}$  and  $V_{IN2}$  are tied to the same fixed input voltage greater than the  $V_{UVLO}$ ; SEQ is tied to logic high; PG1 is tied to MR2; MR1 is left unconnected and is therefore at logic high.

$\overline{\rm EN}$  is initially high; therefore, both regulators are off and PG1 and  $\overline{\rm RESET}$  are at logic low. With SEQ at logic high, when  $\overline{\rm EN}$  is taken low,  $V_{\rm OUT2}$  turns on.  $V_{\rm OUT1}$  turns on after  $V_{\rm OUT2}$  reaches 83% of its regulated output voltage. When  $V_{\rm OUT1}$  reaches 95% of its regulated output voltage, PG1 (tied to  $\overline{\rm MR2}$ ) goes to logic high. When both  $V_{\rm OUT1}$  and  $V_{\rm OUT2}$  reach 95% of their respective regulated output voltages and both  $\overline{\rm MR1}$  and  $\overline{\rm MR2}$  (tied to PG1) are at logic high, RESET is pulled to logic high after a 120ms delay. When a fault on  $V_{\rm OUT1}$  causes it to fall below 95% of its regulated output voltage, PG1 (tied to  $\overline{\rm MR2}$ ) goes to logic low, causing  $\overline{\rm RESET}$  to return to logic low.  $V_{\rm OUT2}$  remains on because SEQ is high.

SLVS291D-MAY 2000-REVISED DECEMBER 2007

Figure 39. Timing when V<sub>OUT1</sub> Faults Out

# TPS70745, TPS70748 TPS70751, TPS70758 TPS70702

SLVS291D-MAY 2000-REVISED DECEMBER 2007

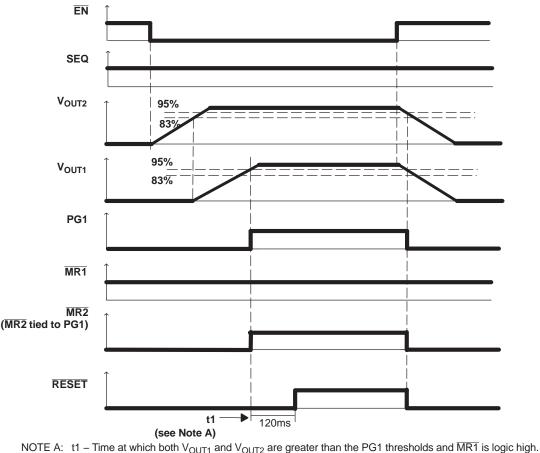

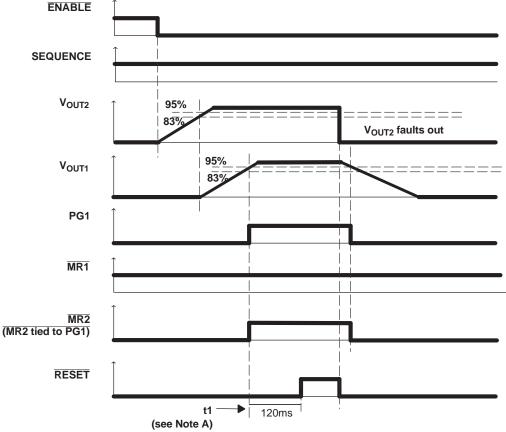

Application condition:  $V_{IN1}$  and  $V_{IN2}$  are tied to the same fixed input voltage greater than the  $V_{UVLO}$ ; SEQ is tied to logic high; PG1 is tied to MR2; MR1 is left unconnected and is therefore at logic high.

$\overline{\rm EN}$  is initially high; therefore, both regulators are off and PG1 and  $\overline{\rm RESET}$  are at logic low. With SEQ at logic high, when  $\overline{\rm EN}$  is taken low,  $V_{\rm OUT2}$  turns on.  $V_{\rm OUT1}$  turns on after  $V_{\rm OUT2}$  reaches 83% of its regulated output voltage. When  $V_{\rm OUT1}$  reaches 95% of its regulated output voltage, PG1 (tied to  $\overline{\rm MR2}$ ) goes to logic high. When both  $V_{\rm OUT1}$  and  $V_{\rm OUT2}$  reach 95% of their respective regulated output voltages and both  $\overline{\rm MR1}$  and  $\overline{\rm MR2}$  (tied to PG1) are at logic high, RESET is pulled to logic high after a 120ms delay. When a fault on  $V_{\rm OUT2}$  causes it to fall below 95% of its regulated output voltage, RESET returns to logic low and  $V_{\rm OUT1}$  falls below 95% of its regulated output voltage, PG1 (tied to  $\overline{\rm MR2}$ ) returns to logic low.

Figure 40. Timing when V<sub>OUT2</sub> Faults Out

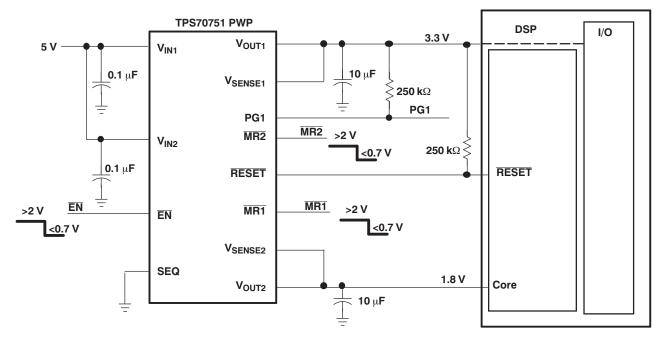

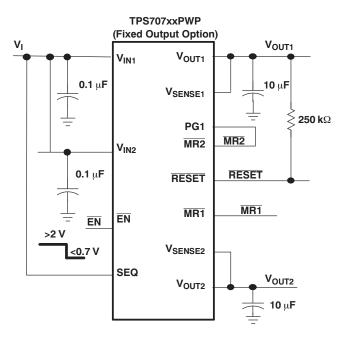

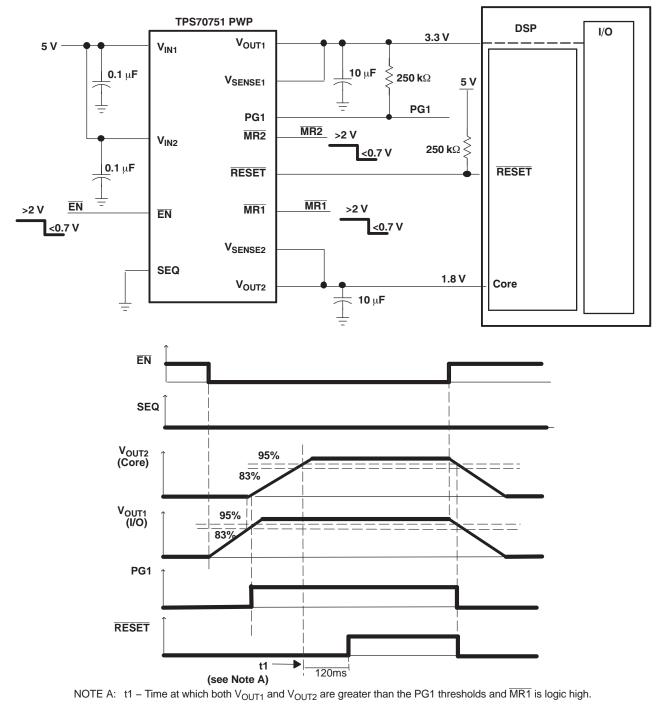

# Split Voltage DSP Application

Figure 41 shows a typical application where the TPS70751 is powering up a DSP. In this application, by grounding the SEQ pin,  $V_{OUT1}$  (I/O) is powered up first, and then  $V_{OUT2}$  (core).

Figure 41. Application Timing Diagram (SEQ = Low)

# TPS70745, TPS70748 TPS70751, TPS70758 TPS70702

SLVS291D-MAY 2000-REVISED DECEMBER 2007

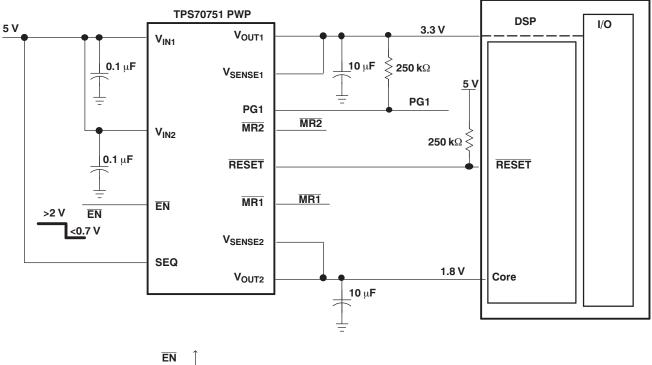

Figure 42 shows a typical application where the TPS70751 is powering up a DSP. In this application, by pulling up the SEQ pin,  $V_{OUT2}$  (core) is powered up first, and then  $V_{OUT1}$  (I/O).

NOTE A: t1 – Time at which both V<sub>OUT1</sub> and V<sub>OUT2</sub> are greater than the PG1 thresholds and MR1 is logic high.

Figure 42. Application Timing Diagram (SEQ = High)

### **Input Capacitor**

For a typical application, an input bypass capacitor  $(0.1\mu F$  to  $1\mu F)$  is recommended. This capacitor filters any high-frequency noise generated in the line. For fast transient conditions where droop at the input of the LDO may occur because of high inrush current, it is recommended to place a larger capacitor at the input as well. The size of this capacitor depends on the output current and response time of the main power supply, as well as the distance to the V<sub>1</sub> pins of the LDO.

### **Output Capacitor**

As with most LDO regulators, the TPS707xx requires an output capacitor connected between OUT and GND to stabilize the internal control loop. The minimum recommended capacitance value is  $10\mu$ F and the ESR (equivalent series resistance) must be between  $50m\Omega$  and  $2.5\Omega$ . Capacitor values  $10\mu$ F or larger are acceptable, provided the ESR is less than  $2.5\Omega$ . Solid tantalum electrolytic, aluminum electrolytic, and multilayer ceramic capacitors are all suitable, provided they meet the requirements described above. Larger capacitors provide a wider range of stability and better load transient response. Table 3 provides a partial listing of surface-mount capacitors suitable for use with the TPS707xx for fast transient response application.

This information, along with the ESR graphs, is included to assist in selection of suitable capacitance for the user application. When necessary to achieve low height requirements along with high output current and/or high load capacitance, several higher ESR capacitors can be used in parallel to meet the guidelines above.

| VALUE | MANUFACTURER | MAXIMUM ESR | MFR PART NO.    |

|-------|--------------|-------------|-----------------|

| 22F   | Kemet        | 345mΩ       | 7495C226K0010AS |

| 33F   | Sanyo        | 100mΩ       | 10TPA33M        |

| 47F   | Sanyo        | 100mΩ       | 6TPA47M         |

| 68F   | Sanyo        | 45mΩ        | 10TPC68M        |

Table 3. Partial Listing of TPS707xx-Compatible Surface-Mount Capacitors

#### ESR and Transient Response

LDOs typically require an external output capacitor for stability. In fast transient response applications, capacitors are used to support the load current while the LDO amplifier is responding. In most applications, one capacitor is used to support both functions.

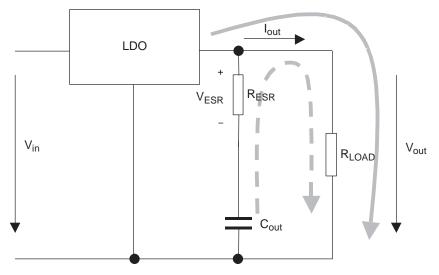

Besides its capacitance, every capacitor also contains parasitic impedances. These parasitic impedances are resistive as well as inductive. The resistive impedance is called *equivalent series resistance* (ESR), and the inductive impedance is called *equivalent series inductance* (ESL). The equivalent schematic diagram of any capacitor can therefore be drawn as shown in Figure 43.

Figure 43. ESR and ESL

In most cases one can neglect the effect of inductive impedance ESL. Therefore, the following application focuses mainly on the parasitic resistance ESR.

Figure 44 shows the output capacitor and its parasitic resistances in a typical LDO output stage.

Figure 44. LDO Output Stage with Parasitic Resistances ESR

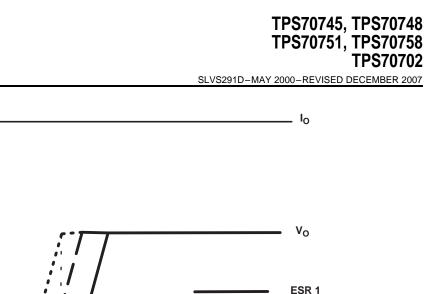

In steady state (dc state condition), the load current is supplied by the LDO (solid arrow) and the voltage across the capacitor is the same as the output voltage ( $V_{(CO)} = V_{OUT}$ ). This condition means no current is flowing into the C<sub>0</sub> branch. If I<sub>OUT</sub> suddenly increases (a transient condition), the following results occur:

- The LDO is not able to supply the sudden current need because of its response time (t<sub>1</sub> in Figure 45). Therefore, capacitor C<sub>O</sub> provides the current for the new load condition (dashed arrow). C<sub>O</sub> now acts like a battery with an internal resistance, ESR. Depending on the current demand at the output, a voltage drop occurs at R<sub>ESR</sub>. This voltage is shown as V<sub>ESR</sub> in Figure 40.

- When C<sub>0</sub> is conducting current to the load, initial voltage at the load will be V<sub>0</sub> = V<sub>(CO)</sub> V<sub>ESR</sub>. As a result of the discharge of C<sub>0</sub>, the output voltage V<sub>0</sub> drops continuously until the response time t<sub>1</sub> of the LDO is reached and the LDO resumes supplying the load. From this point, the output voltage starts rising again until it reaches the regulated voltage. This period is shown as t<sub>2</sub> in Figure 45.

ESR 2 ESR 3

Figure 45 also shows the impact of different ESRs on the output voltage. The left brackets show different levels of ESRs where number 1 displays the lowest and number 3 displays the highest ESR.

From above, the following conclusions can be drawn:

The higher the ESR, the larger the droop at the beginning of load transient.

t<sub>1</sub>

t2

The smaller the output capacitor, the faster the discharge time and the greater the voltage droop during the LDO response period.

#### Conclusion

EXAS RUMENTS

www.ti.com

To minimize the transient output droop, capacitors must have a low ESR and be large enough to support the minimum output voltage requirement.

### Programming the TPS70702 Adjustable LDO Converter

The output voltage of the TPS70702 adjustable regulators are programmed using external resistor dividers as shown in Figure 46.

Resistors R1 and R2 should be chosen for approximately 50µA divider current. Lower value resistors can be used, but offer no inherent advantage and waste more power. Higher values should be avoided as leakage currents at the sense terminal increase the output voltage error. The recommended design procedure is to choose R2 =  $30.1 k\Omega$  to set the divider current at approximately  $50\mu$ A, and then calculate R1 using Equation 1:

$$R1 = \left(\frac{V_{o}}{V_{ref}} - 1\right) \times R2$$

where:

V<sub>REE</sub> = 1.224V typ (the internal reference voltage)

(1)

#### OUTPUT VOLTAGE PROGRAMMING GUIDE

| OUTPUT<br>VOLTAGE | R1  | R2  | UNIT |

|-------------------|-----|-----|------|

| 2.5 V             | 174 | 169 | kΩ   |

| 3.3 V             | 287 | 169 | kΩ   |

| 3.6 V             | 324 | 169 | kΩ   |

### Figure 46. TPS70702 Adjustable LDO Regulator Programming

#### **Regulator Protection**

Both TPS707xx PMOS-pass transistors have built-in back diodes that conduct reverse currents when the input voltage drops below the output voltage (for example, during power-down). Current is conducted from the output to the input and is not internally limited. When extended reverse voltage is anticipated, external limiting may be appropriate.

The TPS707xx also features internal current limiting and thermal protection. During normal operation, the TPS707xx regulator 1 limits output current to approximately 1.6A (typ) and regulator 2 limits output current to approximately 750mA (typ). When current limiting engages, the output voltage scales back linearly until the overcurrent condition ends. While current limiting is designed to prevent gross device failure, care should be taken not to exceed the power dissipation ratings of the package. If the temperature of the device exceeds +150°C (typ), thermal-protection circuitry shuts it down. Once the device has cooled below +130°C (typ), regulator operation resumes.

### **Power Dissipation and Junction Temperature**

Specified regulator operation is assured to a junction temperature of +125°C; the maximum junction temperature should be restricted to +125°C under normal operating conditions. This restriction limits the power dissipation the regulator can handle in any given application. To ensure the junction temperature is within acceptable limits, calculate the maximum allowable dissipation,  $P_{D(max)}$ , and the actual dissipation,  $P_D$ , which must be less than or equal to  $P_{D(max)}$ .

The maximum-power-dissipation limit is determined using Equation 2:

$$\mathsf{P}_{\mathsf{D}(\mathsf{max})} = \frac{\mathsf{T}_{\mathsf{J}} \operatorname{max} - \mathsf{T}_{\mathsf{A}}}{\mathsf{R}_{\mathsf{\theta}\mathsf{J}\mathsf{A}}}$$

where:

- T<sub>Jmax</sub> is the maximum allowable junction temperature

- $R_{\theta JA}$  is the thermal resistance junction-to-ambient for the package; that is, 32.6°C/W for the 20-terminal PWP with no airflow

- T<sub>A</sub> is the ambient temperature

The regulator dissipation is calculated using Equation 3:

$$\mathsf{P}_{\mathsf{D}} = (\mathsf{V}_{\mathsf{I}} - \mathsf{V}_{\mathsf{O}}) \times \mathsf{I}_{\mathsf{O}}$$

Power dissipation resulting from quiescent current is negligible. Excessive power dissipation triggers the thermal protection circuit.

(2)

(3)

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| TPS70702PWP      | ACTIVE        | HTSSOP       | PWP                | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70702                 | Samples |

| TPS70702PWPG4    | ACTIVE        | HTSSOP       | PWP                | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70702                 | Samples |

| TPS70702PWPR     | ACTIVE        | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70702                 | Samples |

| TPS70745PWP      | ACTIVE        | HTSSOP       | PWP                | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70745                 | Samples |

| TPS70748PWP      | ACTIVE        | HTSSOP       | PWP                | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70748                 | Samples |

| TPS70748PWPG4    | ACTIVE        | HTSSOP       | PWP                | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70748                 | Samples |

| TPS70751PWP      | ACTIVE        | HTSSOP       | PWP                | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70751                 | Samples |

| TPS70751PWPR     | ACTIVE        | HTSSOP       | PWP                | 20   | 2000           | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70751                 | Samples |

| TPS70758PWP      | ACTIVE        | HTSSOP       | PWP                | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70758                 | Samples |

| TPS70758PWPG4    | ACTIVE        | HTSSOP       | PWP                | 20   | 70             | RoHS & Green    | NIPDAU                               | Level-2-260C-1 YEAR  | -40 to 125   | PT70758                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

#### www.ti.com

# PACKAGE OPTION ADDENDUM

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:**The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE MATERIALS INFORMATION

Texas Instruments

www.ti.com

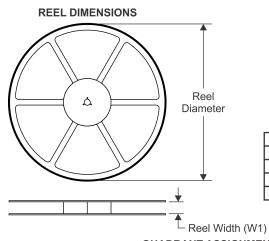

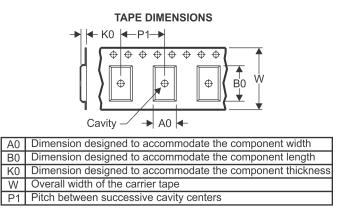

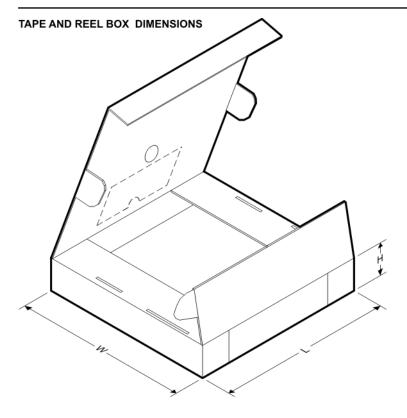

# TAPE AND REEL INFORMATION

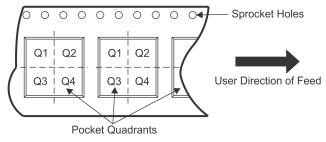

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| TPS70702PWPR                | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TPS70751PWPR                | HTSSOP          | PWP                | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

www.ti.com

# PACKAGE MATERIALS INFORMATION

5-Jan-2022

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS70702PWPR | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS70751PWPR | HTSSOP       | PWP             | 20   | 2000 | 350.0       | 350.0      | 43.0        |

www.ti.com

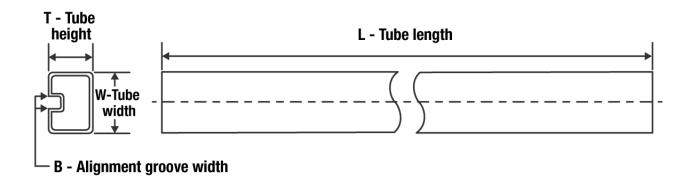

## TUBE

| *All | dimensions | are | nominal |

|------|------------|-----|---------|

|      | unnensions | are | nonnai  |

| Device        | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|---------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPS70702PWP   | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS70702PWPG4 | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS70745PWP   | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS70748PWP   | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS70748PWPG4 | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS70751PWP   | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS70758PWP   | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TPS70758PWPG4 | PWP          | HTSSOP       | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

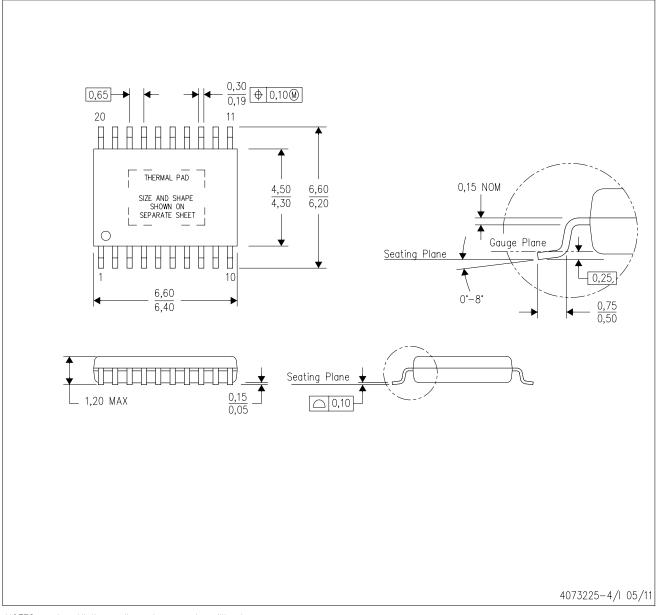

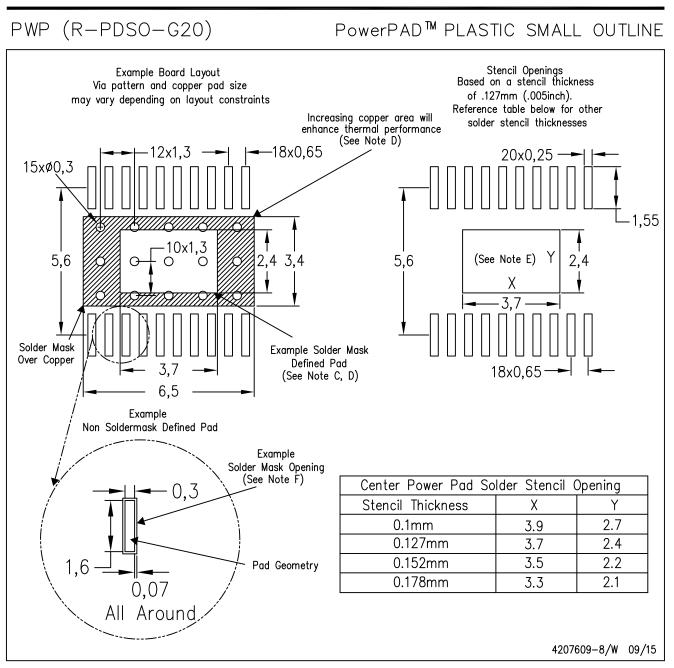

PWP (R-PDSO-G20)

PowerPAD<sup>™</sup> PLASTIC SMALL OUTLINE

All linear dimensions are in millimeters. NOTES: Α.

- Β. This drawing is subject to change without notice.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side. C.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad D.

- Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions. E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

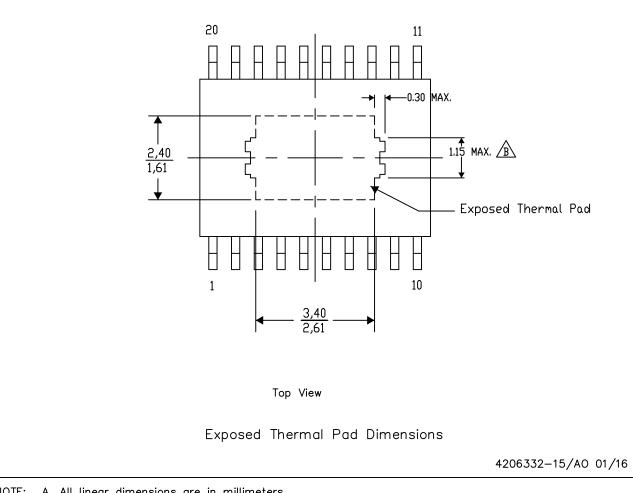

#### PowerPAD<sup>™</sup> SMALL PLASTIC OUTLINE PWP (R-PDSO-G20)

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: A. All linear dimensions are in millimeters

A Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

NOTES:

Α.

B. This drawing is subject to change without notice.

All linear dimensions are in millimeters.

- C. Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <http://www.ti.com>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations.

- F. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated