# **Not for New Design**

These parts are in production but have been determined to be NOT FOR NEW DESIGN. This classification indicates that sale of this device is currently restricted to existing customer applications. The device should not be purchased for new design applications because obsolescence in the near future is probable. Samples are no longer available.

Date of status change: December 14, 2017

**Recommended Substitutions: A6271-1**

NOTE: For detailed information on purchasing options, contact your local Allegro field applications engineer or sales representative.

Allegro MicroSystems, LLC reserves the right to make, from time to time, revisions to the anticipated product life cycle plan for a product to accommodate changes in production capabilities, alternative product availabilities, or market demand. The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringements of patents or other rights of third parties which may result from its use.

### **FEATURES AND BENEFITS**

- Automotive AEC-Q100 qualified

- Constant-current LED drive

- 4.2 to 50 V supply

- 53.3 V maximum LED string voltage

- Boost, buck-boost, and buck switching converters

- Programmable switching frequency 70 to 700 kHz

- PWM-controlled PMOS driver allows accurate LED current control at low duty cycles

- Dimming via external PWM, internal PWM and/or analog dimming

- Frequency dither scheme for effective spread spectrum to reduce EMI

- Comprehensive fault protection and fault flag

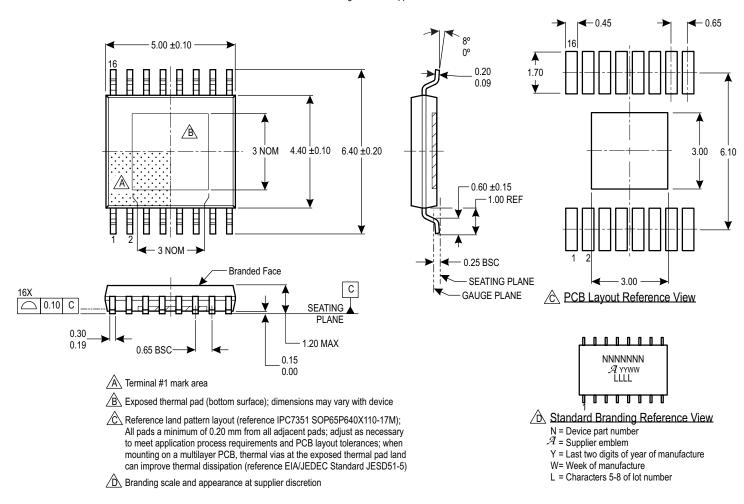

### PACKAGE:

16-Pin eTSSOP (LP) with Exposed Thermal Pad

### **DESCRIPTION**

The A6271 is a DC-DC converter controller, providing a programmable constant-current output for driving high-power LEDs in series. The controller is based on a programmable fixed-frequency, peak current-mode control architecture. The DC-DC converter can be configured in a myriad of different switching configurations including boost, buck-boost, and buck (ground-referenced switch).

The A6271 provides a cost-effective solution using an external logic-level MOSFET and minimum additional external components. The maximum LED current is set with a single external sense resistor and can be accurately modulated using a current reference input (analog control). External PWM dimming is possible via the PWMIN input, which also provides a shutdown mode. As an alternative, an internal PWM dimming circuit can be used by programming the PWMIN and DR pins. Either PWM scheme controls the PWMOUT output which drives an external p-channel MOSFET connected in series with the LED string. This MOSFET is also used to isolate the load during certain fault conditions, including output shorts to ground.

Continued on next page...

### **APPLICATIONS**

- Automotive high-power LED lighting systems

- Fog lights, reversing lights, daytime running lights, position lights, headlights

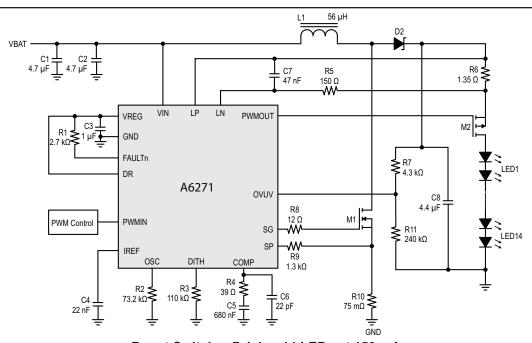

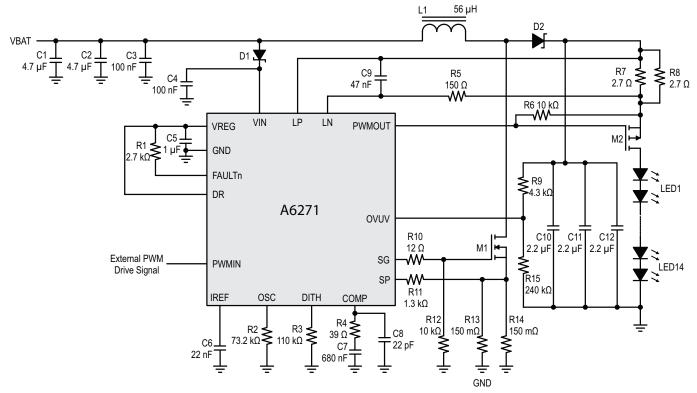

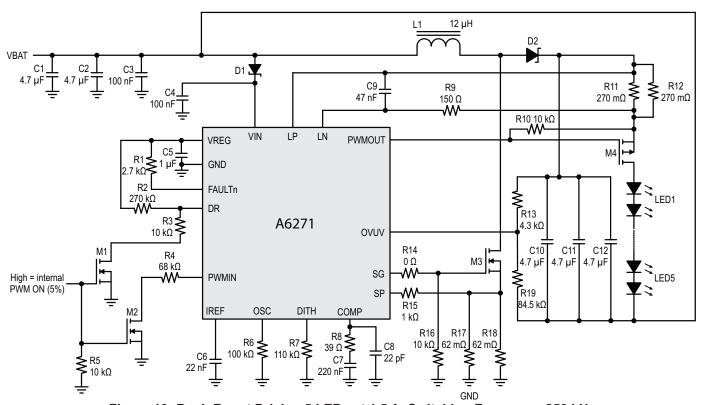

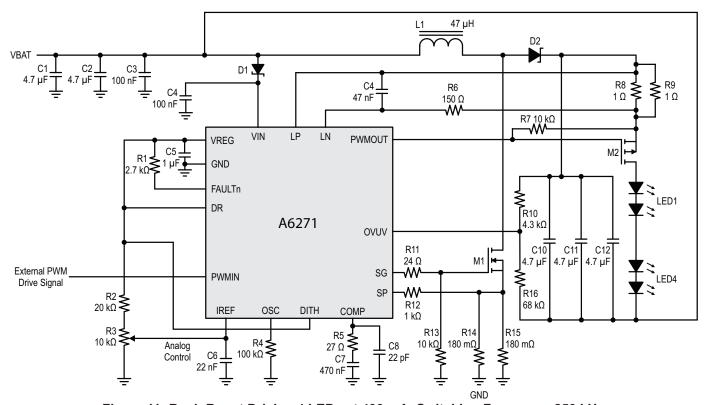

Boost Switcher Driving 14 LEDs at 150 mA

### **Description (continued)**

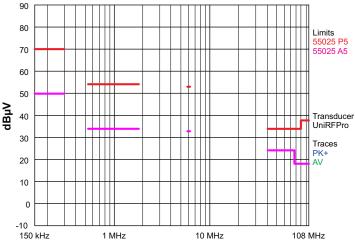

The A6271 has been carefully designed to minimize electromagnetic emissions through distributed decoupling and an externally programmable frequency dither circuit configured for the EMI specification CISPR 25. It is also possible to program the fundamental switching frequency below 150 kHz where most EMI standards begin.

The A6271 has a comprehensive set of integrated protection features to protect the IC, the LED driver system, and the LED string against

faults. Fixed-output overvoltage protection ensures no maximum voltage rating violations, even under a single point failure of the programmable-output overvoltage protection circuit. Other protection features include: LED overload (boost), output undervoltage (buck or buck-boost), input supply (VIN) undervoltage, 5 V regulator (VREG) output undervoltage, high-side supply (PWM PMOS) undervoltage, and thermal protection.

### **SPECIFICATIONS**

#### **SELECTION GUIDE**

| Part Number  | Packing [1]                 | Package                               |

|--------------|-----------------------------|---------------------------------------|

| A6271KLPTR-T | 4000 pieces per 13-in. reel | 16-pin TSSOP with exposed thermal pad |

#### ABSOLUTE MAXIMUM RATINGS [2]

| Characteristic                                         | Symbol               | Notes              | Rating      | Unit |

|--------------------------------------------------------|----------------------|--------------------|-------------|------|

| VIN                                                    | V <sub>IN</sub>      |                    | -0.3 to 55  | V    |

| PWMOUT, LP, LN, OVUV                                   |                      |                    | -0.3 to 58  | V    |

| OSC, DITH, COMP, FAULTn, SG, SP, IREF, PWMIN, DR, VREG |                      |                    | -0.3 to 6.5 | V    |

| LP                                                     | V <sub>LP</sub>      | With respect to LN | -0.5 to 0.5 | V    |

| Maximum Continuous Junction<br>Temperature             | T <sub>J</sub> (max) |                    | 150         | °C   |

| Storage Temperature Range                              | T <sub>stg</sub>     |                    | -55 to 150  | °C   |

<sup>[2]</sup> With respect to GND.

### THERMAL CHARACTERISTICS

| Characteristic | Symbol          | Test Conditions [3]                                          | Value | Unit |  |  |

|----------------|-----------------|--------------------------------------------------------------|-------|------|--|--|

|                | В               | 4-layer PCB based on JEDEC standard                          | 34    | °C/W |  |  |

| eTSSOP Package | $R_{\theta JA}$ | 2-layer PCB with 3.8in <sup>2</sup> of copper area each side | 43    | °C/W |  |  |

|                | $R_{\theta JC}$ | Junction to thermal pad                                      | 2     | °C/W |  |  |

<sup>[3]</sup> Additional thermal information available on the Allegro website.

<sup>[1]</sup> Contact Allegro™ for additional packing options.

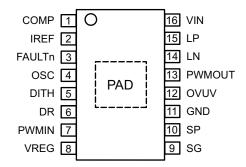

### PINOUT DIAGRAM AND TERMINAL LIST TABLE

Package LP, 16-Pin eTSSOP Pinout Diagram

### **Terminal List Table**

| Symbol | Number | Function                                                                                                                                                                                                                                                       |

|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMP   | 1      | Compensation pin for output of GM error amplifier.                                                                                                                                                                                                             |

| IREF   | 2      | Analog dimming input. With a capacitor connected to this pin, provides a soft-start period when coming out of sleep mode.                                                                                                                                      |

| FAULTn | 3      | Open drain. Logic low indicates detection of a fault. Faults include: LED overload (boost), output undervoltage (buck or buck-boost), output overvoltage, programmable overvoltage, input supply (VIN) undervoltage, 5 V Regulator (VREG) output undervoltage. |

| OSC    | 4      | Oscillator input for setting switching frequency and for external synchronization.                                                                                                                                                                             |

| DITH   | 5      | Dither frequency range set. Connect resistor from this pin to GND. Connect to VREG if not used.                                                                                                                                                                |

| DR     | 6      | A voltage applied to this pin programs the duty cycle of PWM internal mode.                                                                                                                                                                                    |

| PWMIN  | 7      | Used for either putting the device into sleep mode or analog dimming control. Can also be used for external or internal PWM control.                                                                                                                           |

| VREG   | 8      | 5 V regulator output. Connect filter capacitor from VREG to GND.                                                                                                                                                                                               |

| SG     | 9      | Switch gate drive output.                                                                                                                                                                                                                                      |

| SP     | 10     | Switch current sense and slope compensation.                                                                                                                                                                                                                   |

| GND    | 11     | Ground.                                                                                                                                                                                                                                                        |

| OVUV   | 12     | Programmable-output overvoltage and undervoltage protection input.                                                                                                                                                                                             |

| PWMOUT | 13     | PWM gate drive for external p-channel MOSFET (active low).                                                                                                                                                                                                     |

| LN     | 14     | LED current sense -ve.                                                                                                                                                                                                                                         |

| LP     | 15     | LED current sense +ve.                                                                                                                                                                                                                                         |

| VIN    | 16     | Main supply.                                                                                                                                                                                                                                                   |

| PAD    | _      | Exposed pad of both packages provides both electrical contact to the ground and good thermal contact to the PCB. This pad must be soldered to the ground plane preferably by multiple through-hole vias.                                                       |

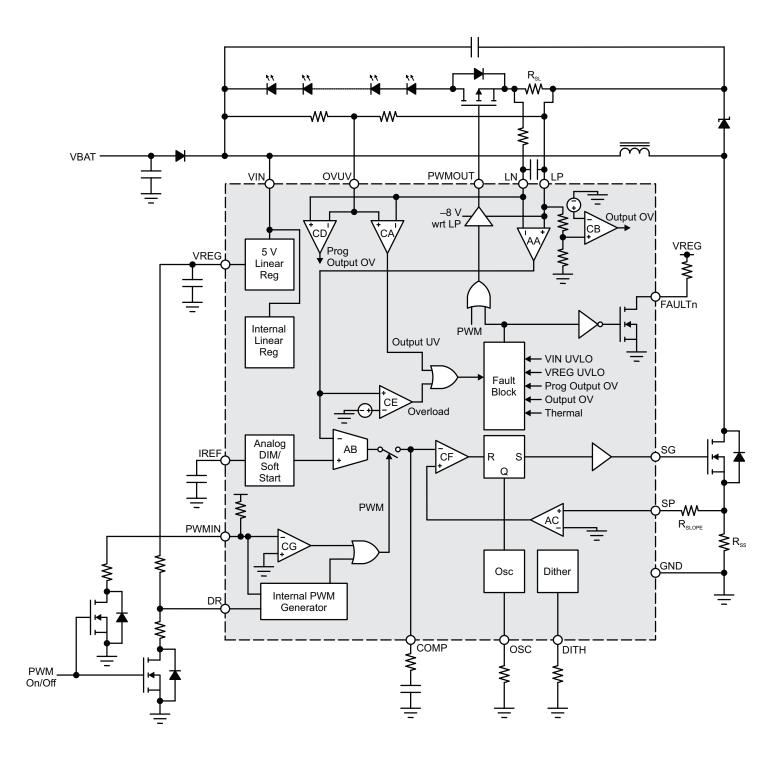

**Functional Block Diagram**

ELECTRICAL CHARACTERISTICS: Valid at T<sub>1</sub> = -40°C to 150°C, V<sub>IN</sub> = 5 to 45 V, unless noted otherwise.

| Characteristics                                           | Symbol                | Test Conditions                                                                                                                 | Min.                   | Тур. | Max.             | Unit |

|-----------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------------|------|

| SUPPLY and REFERENCE                                      |                       |                                                                                                                                 |                        |      |                  |      |

| V <sub>IN</sub> Functional Operating Range <sup>[2]</sup> | V <sub>IN</sub>       | VIN undervoltage turn off plus VIN undervoltage hysteresis cleared; PWMOUT undervoltage turnon cleared                          | 4.2                    | -    | 50               | V    |

| V Quiggaant Current                                       | I <sub>INQ</sub>      | SG Open Circuit                                                                                                                 | _                      | 3.5  | 5                | mA   |

| V <sub>IN</sub> Quiescent Current                         | I <sub>INS</sub>      | PWMIN = GND > disable time                                                                                                      | _                      | 6    | 20               | μA   |

| VREG Output Voltage                                       | \/                    | $I_{REG} = 0$ to 2 mA, $V_{IN} \ge 5.3$ V                                                                                       | 4.85                   | 5.04 | 5.15             | V    |

| VREG Output Voltage                                       | $V_{REG}$             | $I_{REG} = 2 \text{ mA}, V_{IN} = 5 \text{ V}$                                                                                  | 4.65                   | -    | _                | V    |

| VREG Output Voltage [3]                                   | $V_{REG}$             | $I_{REG} = 2 \text{ mA}, V_{IN} = 9 \text{ to } 45 \text{ V},$<br>$T_{J} = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | 4.95                   | 5.05 | 5.15             | V    |

| VREG Current Limit                                        | I <sub>REGCL</sub>    |                                                                                                                                 | 25                     | _    | _                | mA   |

| GATE OUTPUT DRIVE                                         | ,                     |                                                                                                                                 |                        |      |                  |      |

| Turn-On Time                                              | t <sub>r</sub>        | C <sub>LOAD</sub> = 1 nF, 20% to 80%                                                                                            | _                      | 30   | _                | ns   |

| Turn-Off Time                                             | t <sub>f</sub>        | C <sub>LOAD</sub> = 1 nF, 80% to 20%                                                                                            | _                      | 30   | _                | ns   |

| Minimum Off-Time                                          | t <sub>off(MIN)</sub> |                                                                                                                                 | _                      | 135  | 165              | ns   |

| Dull Un On Registance                                     |                       | $T_J = 25^{\circ}C$ , $I_{GHx} = -100 \text{ mA}$                                                                               | _                      | 1.7  | _                | Ω    |

| Pull-Up On-Resistance                                     | R <sub>DS(on)UP</sub> | $T_J = 150$ °C, $I_{GHx} = -100$ mA                                                                                             | _                      | _    | 3.6              | Ω    |

| Pull-Down On-Resistance                                   | Б                     | $T_J = 25^{\circ}C$ , $I_{GLx} = 100 \text{ mA}$                                                                                | _                      | 0.75 | _                | Ω    |

| Full-Down On-Resistance                                   | R <sub>DS(on)DN</sub> | T <sub>J</sub> = 150°C, I <sub>GLx</sub> = 100 mA                                                                               | _                      | -    | 2                | Ω    |

| Output High Voltage                                       | V <sub>SGH</sub>      | I <sub>SG</sub> = -100 μA                                                                                                       | V <sub>REG</sub> – 0.1 | _    | V <sub>REG</sub> | V    |

| Output Low Voltage                                        | $V_{SGL}$             | I <sub>SG</sub> = 100 μA                                                                                                        | _                      | -    | 0.1              | V    |

| LOGIC INPUTS AND OUTPUTS                                  |                       |                                                                                                                                 |                        |      |                  |      |

| FAULTn Output (Open Drain)                                | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA, fault asserted                                                                                          | _                      | _    | 0.4              | V    |

| FAULTn Output Leakage Current <sup>[1]</sup>              | I <sub>OH</sub>       | V <sub>O</sub> = 5.5 V, fault not asserted                                                                                      | -1                     | _    | 1                | μA   |

| PWMIN Low Voltage                                         | V <sub>PWMINL</sub>   |                                                                                                                                 | _                      | _    | 0.3              | V    |

| PWMIN High Voltage                                        | V <sub>PWMINH</sub>   |                                                                                                                                 | 2                      | _    | _                | V    |

| Input Hysteresis                                          | V <sub>Ihys</sub>     |                                                                                                                                 | 150                    | 180  | _                | mV   |

| PWMIN Sleep Pull-Up Current <sup>[1]</sup>                | I <sub>PWMSLEEP</sub> |                                                                                                                                 | _                      | -1.5 | _                | μA   |

| OSCILLATOR                                                | ,                     |                                                                                                                                 |                        |      |                  |      |

| Ossillator Fraguency                                      | f                     | $R_{OSC} = 51 \text{ k}\Omega$                                                                                                  | _                      | 500  | _                | kHz  |

| Oscillator Frequency                                      | fosc                  | $R_{OSC}$ = 73.4 k $\Omega$                                                                                                     | 315                    | 350  | 385              | kHz  |

| Oscillator Frequency Range <sup>[3]</sup>                 | f <sub>osc</sub>      |                                                                                                                                 | 70                     | _    | 700              | kHz  |

| OSC Input Low Voltage                                     | V <sub>OIL</sub>      |                                                                                                                                 | _                      | _    | 0.8              | V    |

| OSC Input High Voltage                                    | V <sub>OIH</sub>      |                                                                                                                                 | 2                      | _    | _                | V    |

| OSC Watchdog Period                                       | t <sub>OSWD</sub>     | Between successive rising edges                                                                                                 | 17                     | _    | _                | μs   |

Continued on the next page...

### **ELECTRICAL CHARACTERISTICS (continued):** Valid at $T_J = -40^{\circ}$ C to 150°C, $V_{IN} = 5$ to 45 V, unless noted otherwise.

| Characteristics                                          | Symbol                | Test Conditions                                     |                          | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------|-----------------------|-----------------------------------------------------|--------------------------|------|------|------|------|

| LED CURRENT SENSE                                        |                       |                                                     |                          |      |      |      |      |

| Input Bias Current LN                                    | I <sub>LN</sub>       | V <sub>LP</sub> = V <sub>LN</sub> = 12 V            |                          | _    | 5    | _    | μA   |

| Input Bias Current LP                                    | I <sub>LP</sub>       | V <sub>LP</sub> = V <sub>LN</sub> = 12 V            |                          | _    | 200  | _    | μA   |

| Differential Sense Voltage                               | V <sub>IDL</sub>      | PWMIN = high, $V_{IDL} = V_{LP} - V_{LN}$ ,         | I <sub>REF</sub> > 1.2 V | 200  | 204  | 208  | mV   |

| Input Common-Mode Range                                  | V <sub>CMLH</sub>     | $V_{LP} = V_{LN}$                                   |                          | 5    | _    | 53.3 | V    |

| ANALOG DIMMING                                           |                       |                                                     |                          |      |      |      |      |

| Disable Time                                             | t <sub>DISAN</sub>    | PWMIN = low                                         |                          | 24.8 | 29   | 35   | ms   |

| Differential Course Vallege                              | \/                    | V <sub>IREF</sub> = 0.5 V                           |                          | _    | 102  | _    | mV   |

| Differential Sense Voltage                               | V <sub>IDL</sub>      | V <sub>IREF</sub> = 0.25 V                          |                          | 47   | 51   | 55   | mV   |

| IREF Maximum Voltage                                     | V <sub>IREFMAX</sub>  | Corresponds to sense voltage = 2                    | 200 mV                   | _    | 1    | _    | V    |

| IREF Minimum Voltage                                     | V <sub>IREFMIN</sub>  | Corresponds to sense voltage = 0                    | 0 mV                     | _    | 0    | _    | V    |

| PWM DIMMING: INTERNAL AND EXTERNA                        |                       | ,                                                   |                          |      |      |      |      |

| PWMIN to LED Turn-On Time                                | t <sub>DIMON</sub>    | C <sub>L</sub> = 2 nF between PWMOUT and            | LN                       | _    | 270  | _    | ns   |

| PWMIN to LED Turn-Off Time                               | t <sub>DIMOFF</sub>   | C <sub>L</sub> = 2 nF between PWMOUT and            | d LN                     | _    | 210  | _    | ns   |

| PWMOUT Low Voltage                                       | V <sub>PWMLO</sub>    | LED on, PWMOUT wrt LP, V <sub>IN</sub> =            | 10 V                     | -9   | _    | -6.5 | V    |

| Peak Pull-Up Current <sup>[1]</sup>                      | I <sub>PULLUP</sub>   | PWMIN = low, PWMOUT wrt LP :                        | = 0 V                    | _    | -25  | _    | mA   |

| Peak Pull-Down Current                                   | I <sub>PULLDOWN</sub> | PWMIN = high, PWMOUT wrt LP                         | = -8 V                   | _    | 50   | _    | mA   |

| PWM DIMMING: EXTERNAL                                    | •                     |                                                     |                          |      |      |      |      |

| Disable Time                                             | t <sub>DISEPWM</sub>  | PWMIN = low                                         |                          | 24.8 | 29   | 35   | ms   |

| PWM DIMMING: INTERNAL                                    |                       |                                                     |                          |      |      |      |      |

| Maximum PWM Dimming Frequency                            | f <sub>PWM</sub>      |                                                     |                          | _    | 1000 | _    | Hz   |

| Minimum PWM Dimming Frequency                            | f <sub>PWM</sub>      |                                                     |                          | _    | 200  | _    | Hz   |

| PWM Dimming Frequency                                    | f <sub>PWM</sub>      | 70 kΩ between PWMIN and GND                         | )                        | 180  | 200  | 220  | Hz   |

|                                                          | <u></u>               | V = 2.24 V f = 200 Hz                               | T <sub>J</sub> = 25°C    | 87   | 90   | 93   | %    |

|                                                          | D <sub>PWM90</sub>    | $V_{DR} = 3.24 \text{ V}, f_{PWM} = 200 \text{ Hz}$ | T <sub>J</sub> = 150°C   | _    | 90   | _    | %    |

| DIA/AA Durty Cycle                                       |                       | ., ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,             | T <sub>J</sub> = 25°C    | 4.5  | 5    | 5.5  | %    |

| PWM Duty Cycle                                           | D <sub>PWM5</sub>     | V <sub>DR</sub> = 180 mV, f <sub>PWM</sub> = 200 Hz | T <sub>J</sub> = 150°C   | _    | 5    | _    | %    |

|                                                          | D <sub>PWM0</sub>     | V <sub>DR</sub> = 0 V, f <sub>PWM</sub> = 200 Hz    | T <sub>J</sub> = 25°C    | _    | 0.3  | _    | %    |

|                                                          | V <sub>DRDCMAX</sub>  | Minimum voltage on DR for 100%                      | duty cycle               | _    | 3.6  | _    | V    |

| Disable Time                                             | t <sub>DISIPWM</sub>  | PWMIN = low                                         |                          | 12.4 | 14.5 | 17.5 | ms   |

| SOFT-START                                               |                       |                                                     |                          |      |      |      |      |

| Startup Ramp Up Source Current <sup>[1]</sup>            | I <sub>SOURCE</sub>   | Coming out of sleep mode                            |                          | _    | -1   | _    | μA   |

| Ramp Up Threshold                                        | V <sub>RAMPUP</sub>   |                                                     |                          | _    | 1    | _    | V    |

| Ramp Down Threshold                                      | V <sub>RAMPDOWN</sub> |                                                     |                          | _    | 100  | _    | mV   |

| SWITCH CURRENT SENSE AND AMPLIFIE                        |                       |                                                     |                          |      |      |      |      |

| Input Bias Current [1]                                   | I <sub>BIASS</sub>    | $V_{SP}$ = 300 mV, $R_{SLOPE}$ = 1.5 k $\Omega$     |                          | -20  | _    | _    | μA   |

| Switch Current Overload Threshold Voltage <sup>[3]</sup> | V <sub>IDS</sub>      |                                                     |                          | 375  | 400  | 435  | mV   |

| Voltage Gain                                             | A <sub>CS</sub>       |                                                     | <u> </u>                 | _    | 2.25 | _    | V/V  |

Continued on the next page...

### ELECTRICAL CHARACTERISTICS (continued): Valid at $T_J = -40^{\circ}$ C to 150°C, $V_{IN} = 5$ to 45 V, unless noted otherwise.

| Characteristics                           | Symbol                | Test Conditions                                                             | Min.  | Тур. | Max.  | Unit            |

|-------------------------------------------|-----------------------|-----------------------------------------------------------------------------|-------|------|-------|-----------------|

| SLOPE COMPENSATION                        |                       |                                                                             |       |      |       |                 |

| Peak Current [1]                          | I <sub>SLOPE</sub>    | Sawtooth current waveform added to current-<br>sense input (SP)             | -116  | -    | -93   | μA              |

| GM AMPLIFIER                              |                       |                                                                             |       |      |       |                 |

| Open Loop DC Gain                         | A <sub>VEA</sub>      |                                                                             | _     | 62   | _     | dB              |

| Transconductance                          | g <sub>mCOMP</sub>    |                                                                             | 550   | 750  | 950   | μA/V            |

| COMP Source/Sink Current [1]              | I <sub>COMP</sub>     |                                                                             | _     | ±50  | _     | μΑ              |

| COMP Leakage Current [1]                  | I <sub>LCOMP</sub>    |                                                                             | _     | ±200 | _     | nA              |

| DITHER GENERATOR                          |                       |                                                                             |       |      |       |                 |

| Dither Modulation Frequency               | f <sub>DITH</sub>     |                                                                             | 7.9   | 9.6  | 11.2  | kHz             |

| Maximum Switching Frequency               | f <sub>OSCMAX</sub>   | $R_{OSC}$ = 72 kΩ, $R_{DITH}$ = 110 kΩ                                      | 348   | 400  | 452   | kHz             |

| Minimum Switching Frequency               | f <sub>OSCMIN</sub>   | $R_{OSC}$ = 72 kΩ, $R_{DITH}$ = 110 kΩ                                      | 261   | 300  | 339   | kHz             |

| PROTECTION FEATURES                       |                       |                                                                             |       |      |       |                 |

| Fault Blank Timer <sup>[4]</sup>          | t <sub>FB</sub>       | Startup                                                                     | _     | 3    | _     | ms              |

| VIN Undervoltage Turn-Off                 | V <sub>INUV</sub>     | Decreasing V <sub>IN</sub> , I <sub>REG</sub> = 2 mA                        | 3.9   | -    | 4.2   | V               |

| VIN Undervoltage Hysteresis               | $\Delta V_{INUV}$     |                                                                             | 250   | _    | 380   | mV              |

| VREG Undervoltage Turn-Off                | V <sub>REGUV</sub>    | Decreasing V <sub>REG</sub>                                                 | 3.25  | -    | 3.5   | V               |

| VREG Undervoltage Hysteresis              | $\Delta V_{REGUV}$    |                                                                             | _     | 300  | _     | mV              |

| LED Overcurrent Threshold                 | V <sub>OCLED</sub>    | LP wrt LN                                                                   | 260   | 320  | 380   | mV              |

| Fixed-Output Overvoltage Threshold        | V <sub>FOOV</sub>     | Monitored at LP pin with respect to GND                                     | 53.3  | 55.5 | 57    | V               |

| Programmable-Output Overvoltage Threshold | V <sub>POOV</sub>     | OVUV wrt LN                                                                 | -1.24 | -1.1 | -1    | V               |

| Output Undervoltage Threshold             | V <sub>OUV</sub>      | OVUV wrt LN                                                                 | -300  | -    | _     | mV              |

| Switch Current Overload Period            | t <sub>SCOP</sub>     | Inner loop switch current                                                   | _     | 64   | _     | clock<br>cycles |

| LED Overcurrent Period                    | t <sub>OPI</sub>      |                                                                             | _     | 2    | _     | clock<br>cycles |

| LED Output Undervoltage Period            | t <sub>OPV</sub>      |                                                                             | _     | 30   | -     | clock<br>cycles |

| Hiccup Shutdown Period                    | t <sub>HIC</sub>      | LED overcurrent, or output undervoltage, or overvoltage, or switch overload | 22    | 26.5 | 31.75 | ms              |

| PWMOUT Undervoltage Turn-On               | V <sub>PWMUVON</sub>  | Measured at LP wrt GND                                                      | _     | -    | 6     | V               |

| PWMOUT Undervoltage Turn-Off              | V <sub>PWMUVOFF</sub> | Measured at LP wrt GND                                                      | 3.7   | _    | 5.8   | V               |

| Overtemperature Shutdown Threshold        | T <sub>JF</sub>       | Temperature increasing                                                      | 155   | 170  | _     | °C              |

| Overtemperature Hysteresis                | $\Delta T_J$          | Recovery = $T_{JF} - \Delta T_{J}$                                          | _     | 20   | -     | °C              |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device pin.

<sup>[2]</sup> Function is correct, but some parameters may not meet specification.

$<sup>\</sup>space{-0.05cm}$  Parameters guaranteed by design and characterization.

<sup>[4]</sup> Fault blank timer only enabled for either output undervoltage or switch current overload.

### FUNCTIONAL DESCRIPTION

The A6271 is a DC-DC converter controller designed to drive series-connected high-power LEDs in automotive applications. The A6271 can be configured in a variety of switching topologies, including: boost, buck-boost, and buck (ground-referenced switch). For each switching configuration, the appropriate loop compensation (COMP) and slope compensation (SLOPE) passive components are selected for optimal performance.

The A6271 integrates all the necessary control elements to provide a cost-effective solution using an external logic-level, n-channel MOSFET (switching device), p-channel MOSFET (PWM device), and minimum additional external passive components. The maximum LED current is set with a single external sense resistor and can be accurately modulated using a current reference input (analog control). Direct PWM control is possible via the PWMIN input, which also provides a shutdown mode.

### **Circuit Operation**

#### **CONVERTER**

The controller is based on a fixed-frequency, peak current-mode control architecture. There are two loops within the controller. The inner loop, formed by the amplifier AC (refer to Functional Block Diagram), the slope generator, the comparator, CF, and the RS bistable, controls the inductor current as measured through the switching MOSFET by the sense resistor  $R_{SS}$ . The outer loop, formed by the amplifier AA and the integrating GM amplifier AB, controls the average LED current by providing the current demand signal for the inner loop.

The LED current is measured by the sense resistor,  $R_{SL}$ , and is averaged and amplified to a level where it is compared to the internal reference current to produce an error signal at the output of the GM amplifier, AB. This error signal is effectively the current demand signal and determines the amount of energy transferred to the LEDs on a cycle-by-cycle basis via the inner loop.

The control loops work together as follows: at the beginning of each oscillator cycle, the bistable is set and the switching MOSFET is on. The switch current builds up due to the voltage developed across the inductor, and when the corresponding signal produced at the output of amplifier AC reaches the current demand level on the output of amplifier AB, the bistable is reset and the switching MOSFET is turned off. The cycle is repeated on the next oscillator cycle.

If the current through the LEDs increases, the output of AA

increases, causing the current demand signal to decrease. This reduces the amount of energy transferred to the LED load by terminating the switch current sooner and reducing the LED current.

#### **EXTERNAL PULSE-WIDTH MODULATION DIMMING**

The DR pin should be pulled to VREG.

During PWM operation, when PWMIN is pulled low, the LED stack PWMOUT is pulled high with respect to LP, turning off the external p-channel MOSFET, isolating the LED string. In addition, the GM output (amplifier AB) is 'parked' (COMP components disconnected) at the new level and the gate drive (SG) is disabled. As the output capacitance is isolated from the LED string, there is no loss of charge.

When PWMIN goes high impedance, or is pulled high, the COMP components are reconnected (with the previous 'parked' value'), the gate drive (SG) is enabled, PWMOUT is pulled to around –8 V with respect to LP turning on the external MOSFET and allowing current to flow through the LED string.

#### INTERNAL PULSE-WIDTH MODULATION DIMMING

Where an external PWM signal is not available, the internal PWM generator can be used for controlling the LED brightness. A resistor connected between the PWMIN pin and GND sets the PWM frequency according to the following formula:

$$R_{{\scriptscriptstyle FREQ}} = \frac{14,000}{f_{{\scriptscriptstyle PWM}}}$$

where  $R_{FREO}$  is in  $k\Omega$  and  $f_{PWM}$  is in Hz.

The duty cycle is controlled by applying a voltage to the DR pin. The VREG can be used for the supply voltage and a potential divider can be used to set the DR voltage. An additional resistor can be added in parallel via a MOSFET switch between DR and GND to change the duty cycle between two levels.

The relationship between the DR voltage and the duty cycle is as follows:

*PWM Duty cycle* (%) =

$$27.81 \times DR$$

*voltage*

So, for example, with a DR voltage = 1.8 V, the programmed duty cycle = 50%.

In terms of the control of the external MOSFET via the PWM-OUT pin, the control is identical as the external PWM scheme.

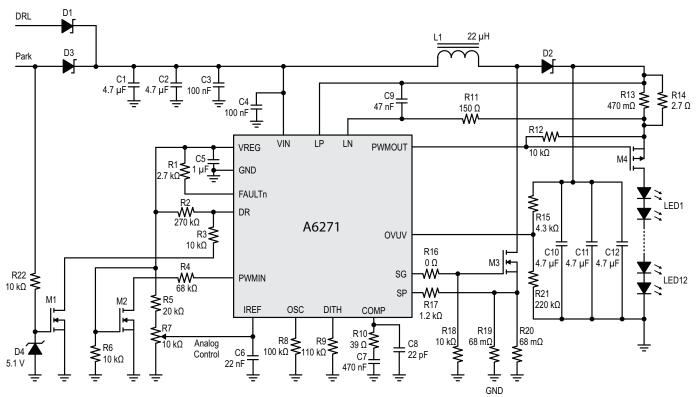

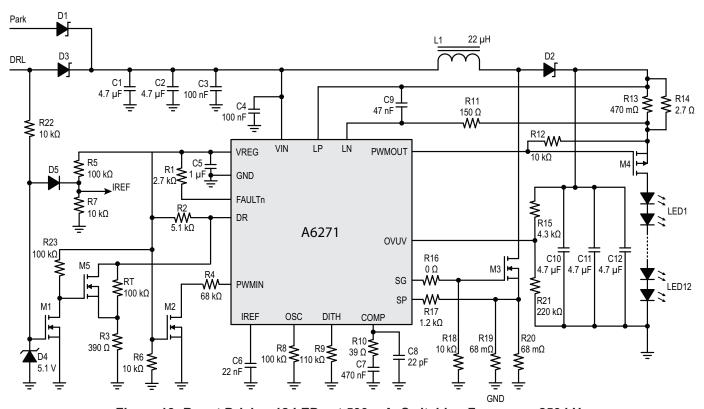

When using the internal PWM scheme, an n-channel MOSFET is required to open the ground connection of the resistor connected between PWMIN and GND to ensure that startup occurs. The gate of the MOSFET is connected to VREG as shown in Figures 13 and 14, or to an external control signal as shown in Figures 9 and 11.

As the PWMIN input has a pull-up of only 1.1  $\mu$ A in sleep mode, it is essential that the zero gate voltage, drain current (leakage) of the MOSFET does not exceed this number at maximum ambient temperatures.

#### **ANALOG DIMMING**

The IREF pin can then be used for full analog control. The LED current can be linearly adjusted from zero to full (100%) LED current ( $I_{LED}$ ) by changing the IREF pin from 0 to  $\geq$  1 V.

This feature is useful in applications where PWM control is either not required or not available and the LEDs require some dynamic correction for brightness adjustment.

Analog dimming can be used along with either pulse-widthmodulation technique, internal or external. This is useful for applications where some color correction is required along with brightness control.

Soft-start can be provided via the analog dim signal when either coming out of sleep or hiccup mode. The internal 1  $\mu A$  internal source current on the IREF node can be overridden by applying a ramp signal to IREF. The soft-start duration is controlled by the signal on IREF as it is ramped from 0 to 1 V.

If no soft-start is required, the IREF pin should be connected to VREG. If no internal PWM is required, the DR pin should be connected to VREG.

### **SOFT-START**

When the A6271 comes out of sleep mode, soft-start is required to bring the output voltage up in a controlled open-loop fashion. This minimizes the possibility of the control loop saturating during the startup phase and subsequent output voltage overshoot, which can induce high transient peak currents in the LED string prior to the loop being brought back into linear control.

The soft-start period can be programmed by the selection of the appropriate capacitor between IREF pin and GND pin according to the following formula:

$$C_{soft} = \frac{t_{soft} \times 1 \times 10^{-6}}{1.2}$$

where t<sub>soft</sub> is the desired soft-start period.

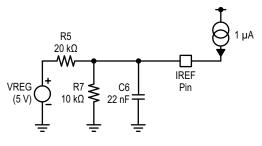

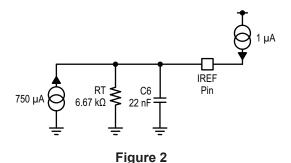

If analog dimming is applied, the equivalent current source from this circuit will add to the internal 1  $\mu A$  source current on the IREF node. Generally speaking, when using analog dimming via VREG and a potential divider, no soft-start or negligible soft-start is provided as shown in the example below. References are taken from Figure 9 on page 23:

Figure 1

From the above diagram, VREG, R5, and R7 can be simplified using Norton's Theorem.

The equivalent resistance can be found:

$$R_T = \frac{20 \times 10}{20 + 10} = 6.67 \, k\Omega$$

The current source can be found:

$$I_{source} = \frac{5}{R_T} = 750 \ \mu A$$

From the above schematic, it is clear that the 750  $\mu$ A current source will dominate and almost no soft-start will be provided. In this particular case, the only option is to resize C6, or increase the values of R5 and R7, or both.

#### LED CURRENT-SENSE RESISTOR

The LED current is programmed by the LED sense resistor,  $R_{\rm SL}$ , according to:

$$I_{LED} = \frac{V_{IDL}}{R_{SI}}$$

where the loop typically regulates  $V_{IDL}$  to 200 mV when in either internal or external PWM modes.

The power loss of the resistor should be taken into account to ensure the correct package size is selected.

The power loss of the LED current-sense resistor, R<sub>SL</sub> is:

$$P = I_{LED}^2 \times R_{SL}$$

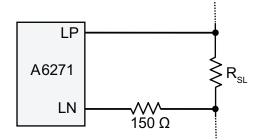

It is advisable to insert a 150  $\Omega$  resistor in series with the LN pin, as shown below, to protect the internal ESD structures between LN and LP under certain fault conditions. The 150  $\Omega$  value is selected as a balance between limiting the fault current and minimizing the LED current error caused by the bias current flowing into the LN pin.

Figure 3

### **SLEEP MODE**

If PWMIN is held low for longer than the disable time,  $t_{DIS1}$  or  $t_{DIS2}$ , then the A6271 will shut down and put the majority of the circuitry into a low-power sleep mode.

When internal PWM dimming is used, the disable time,  $t_{DIS1}$ , is 14.5 ms.

When either external PWM dimming or analog dimming is used, the disable time,  $t_{DIS2}$  is 29 ms.

### **5 V REGULATOR, VREG**

To provide a filtered output and to ensure the regulator is stable, a 1  $\mu F$  ceramic capacitor is required to be connected between VREG and GND. The ceramic type should be a quality type such as X5R, X7R, or X8R.

The 5 V regulator is sized for driving the external switching MOSFET. However, it can be used for functions that require minimal current, e.g. pulling up the FAULTn output and providing a reference for the DR, the IREF pin, or both.

To check the load that the MOSFET provides, it is necessary to check the total gate charge required for a 5 V drive. This can be derived from the gate charge,  $Q_G$ , versus gate drive voltage,  $V_{GS}$ , from the MOSFET datasheet. Once the gate charge is found, the regulator load current can be determined:

$$I_{LOAD} = (Q_G \times f_{SW}) + I_{external}$$

where  $I_{\text{external}}$  is the additional circuitry added to the VREG output.

The  $I_{LOAD}$  should not exceed the VREG external current limit ( $I_{REGCL}$ ).

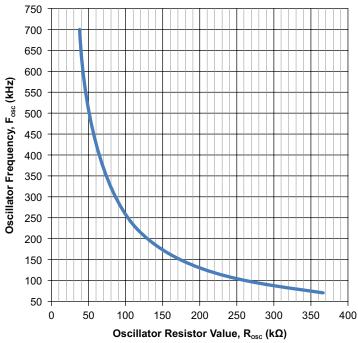

Figure 4: R<sub>OSC</sub> Required for a Particular Oscillator Frequency

#### **OSCILLATOR**

The main oscillator may be configured as a clock source or it may be driven by an external clock signal. The oscillator is designed to run between 70 and 700 kHz.

When the oscillator is configured as a clock source, the frequency is programmed via an external resistor between OSC pin and GND pin. The appropriate resistor can be found:

$$R_{OSC} = \frac{25,690}{f_{OSC}}$$

where  $R_{OSC}$  is in  $k\Omega$  and  $f_{OSC}$  is in kHz.

Figure 4 shows the resulting R<sub>OSC</sub> for various frequencies.

When the OSC pin is driven by an external clock source, a number of A6271s can be synchronized together. If the clock period is greater than or equal to 17  $\mu$ s, a watchdog circuit causes the running frequency to default to the internal oscillator, which runs at 350 kHz.

If the oscillator pin goes either open circuit or short circuits to GND, the running frequency defaults to 350 kHz.

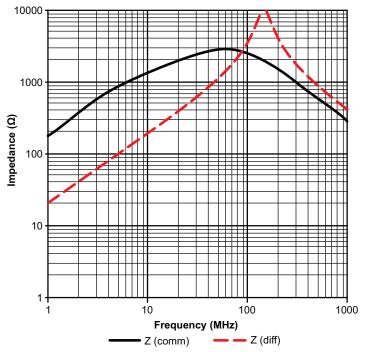

### FREQUENCY DITHERING

To assist in minimizing EMI emissions, the main oscillator can be dithered so that the energy is spread over a defined frequency band. The defined frequency band is effectively the minimum and maximum switching frequency selected. This frequency is varied above and below the selected oscillator frequency and is set via a resistor connected between Dither pin and GND pin. The frequency band can be selected as follows:

$$\Delta f = \pm 22 \times \frac{R_{OSC}}{R_{DITH}}$$

where  $\Delta f$  is a plus/minus percentage change with respect to the oscillator frequency.

For example, if an oscillator frequency of 350 kHz and a dithered frequency band of  $\pm 50$  kHz was selected, given a minimum switching frequency of 300 kHz and a maximum switching frequency of 400 kHz, the  $R_{\mbox{\scriptsize OSC}}$  and  $R_{\mbox{\scriptsize DITHER}}$  can be found:

$$R_{OSC} = \frac{25,690}{f_{OSC}}$$

$$R_{OSC} = \frac{25,690}{350} = 73.4 \text{ k}\Omega, \text{ say } 72 \text{ k}\Omega$$

$\Delta f$  as a percentage of the delta with respect to the oscillator frequency is  $(50/350) \times 100\% = 14.3\%$ .

Therefore, R<sub>DITH</sub> can be found from:

$$\Delta f = \pm 22 \times \frac{R_{OSC}}{R_{DITH}}$$

$$R_{DITH} = 22 \times \frac{72}{143} = 110 \text{ k}\Omega$$

The switching frequency is modulated at a rate of 10 kHz via a triangular waveform. This means in one modulation cycle, the switching frequency varies linearly from a minimum to a maximum to a minimum again.

If the dither feature is not required, the DITH pin should be tied to VREG.

### **PROTECTION**

The A6271 includes a number of safety features to ensure the controller, the external power components, and the LED string are protected.

The Fault Flag becomes active for any fault.

When the device recovers from a fault, a soft-start is performed unless analog dimming is selected and the DR pin is tied to VREG.

At initial startup, when coming out of sleep mode, or when the hiccup period terminates, a fault blank period, t<sub>FB</sub>, of 3 ms is applied for two fault conditions including low-side switch current limit (inner loop) protection and LED overload protection (caused by an undervoltage), before the fault circuitry becomes active. This period allows steady-state conditions to occur before fault monitoring takes place.

### **Output Overvoltage Protection**

Two overvoltage protection circuits exist: an internal fixed circuit and an externally programmable circuit. In the majority of applications, the externally programmable circuit will provide the protection. The internal circuit is present in the event that the external feedback resistor chain of the programmable circuit goes open circuit. This feature is particularly desirable in systems that require high levels of reliability and the ability to withstand failure modes. Another advantage is the possibility, in lower voltage applications, to select reduced operating voltages for the switching MOSFET, PWM MOSFET, recirculation diode, and output filter capacitors with confidence.

If an overvoltage occurs in either of the two circuits, the high-side MOSFET drive (PWMOUT) and the low-side MOSFET drive (SG) are immediately disabled and FAULTn is active. After one fault mask switching cycle, the hiccup timer, t<sub>HIC</sub>, is initiated for a period of 26.5 ms. At the beginning of the hiccup period, the IREF node (soft-start) capacitor is discharged immediately. After the hiccup period, an auto-restart is performed under control of the soft-start capacitor.

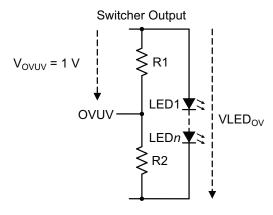

A potential divider is set up between the LP node (output of the converter) and the cathode end of the LED stack. The output of the potential divider is monitored by a comparator referenced to the LN node. Once this voltage decreases below –1 V(max), an overvoltage condition is reported.

It is recommended that the impedance of the potential divider is kept relatively high, especially in high-voltage LED strings, to minimize the current draw. It should be noted that there is negligible bias current drawn by the comparator monitor circuit.

As an example, consider an LED string which has a maximum LED string voltage of 45 V and an output overvoltage ( $VLED_{OV}$ ) is to be reported at a minimum of 15% above this value.

Cathode: LED Stack

Figure 5

R2 can be found:

$$R2 = \frac{R1 \times (VLED_{OV} - V_{OVUV})}{V_{OVUV}}$$

Assume resistor R1 is selected to be 4.3 k $\Omega$ .

$$VLED_{OV}$$

is  $1.15 \times 45 = 52 \text{ V}$ .

V<sub>OVUV</sub> is a minimum of 1 V.

From the above formula:

$$R2 = \frac{4.3 \times (52 - 1)}{1} = 219 \text{ k}\Omega, \text{ select } 220 \text{ k}\Omega$$

#### **Overload Protection**

There are two circuits:

- 1. LED overcurrent threshold

- 2. Output undervoltage threshold

In the case of a LED overcurrent fault, the high-side MOSFET drive (PWMOUT) and the low-side MOSFET drive (SG) are disabled after two fault mask switching cycles, FAULTn is active, the IREF node (soft-start) capacitor is discharged, then the hiccup timer, t<sub>HIC</sub>, is initiated for a period of 26.5 ms. After the hiccup period, an auto-restart is performed under control of the soft-start capacitor.

In the case of an output undervoltage fault, the high-side MOS-FET drive (PWMOUT) is immediately disabled and FAULTn is active. After thirty fault mask switching cycles, the low-side MOSFET drive (SG) is disabled, IREF node (soft-start) capacitor is discharged, and the hiccup timer, t<sub>HIC</sub>, is initiated for a period of 26.5 ms. After the hiccup period, an auto-restart is performed under control of the soft-start capacitor.

### **Low-Side Switch Current Limit (inner loop)**

At startup, a 3 ms blank period is applied before the circuitry becomes active. Cycle-by-cycle current protection is provided through the low-side MOSFET. If an overcurrent occurs for longer than 64 switching clock cycles, the high-side MOSFET drive (PWMOUT) and the low-side MOSFET drive (SG) are disabled, FAULTn is active, and the hiccup timer, t<sub>HIC</sub>, is initiated for a period of 26.5 ms. During the hiccup period, the IREF node (soft-start) capacitor is discharged immediately. After the hiccup period, an auto-restart is performed under control of the soft-start capacitor.

#### Input Undervoltage or VREG Undervoltage Protection

If either condition occurs, the low-side MOSFET drive (SG) is disabled and FAULTn is active (assuming VREG is high enough, if FAULTn is pulled to VREG). In the case of the input undervoltage, the high-side MOSFET drive (PWMOUT) is also disabled.

Both the input voltage and the VREG voltage must rise above their respective turn-on thresholds before a restart is possible. In the case of startup through the input voltage turn-on threshold, the system is brought up under control of the soft-start. In the case of startup through the VREG turn-on threshold, no soft-start is provided.

### **PWM Output Undervoltage**

During startup, the output (LP node) must increase above 6 V to ensure the high-side MOSFET turns on. This is generally not a problem with switching topologies that can boost the output voltage with respect to the input voltage. In the case of the buck topology, the LN/LP node is referenced to VIN; therefore, the input voltage has to be equal to or greater than 6 V to guarantee a successful startup.

### **Overtemperature Shutdown**

If the chip exceeds the overtemperature shutdown threshold, the low-side MOSFET drive (SG) is immediately disabled, FAULTn is active, and the IREF node (soft-start) capacitor is discharged immediately. An auto-restart is performed under control of the soft-start capacitor once the temperature drops below the overtemperature minus the hysteresis level.

The table on the following page summarizes the above faults along with other pin specific faults.

# Automotive, High-Current LED Controller

Table 1: Fault Table

| Fault                                                                                                                                                                                                        | Action                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low-Side Switch Current Limit                                                                                                                                                                                | When fault occurs, cycle-by-cycle current limit operates.  If fault >64 counts: low-side MOSFET (SG) and PWM MOSFET (PWMOUT) off and FAULTn active, hiccup period, then auto-restart with soft-start.  Note: fault blanked for 3 ms during startup.    |

| LED Overcurrent                                                                                                                                                                                              | Low-side MOSFET (SG) and PWM MOSFET (PWMOUT) immediately off and FAULTn active, hiccup period after 2 counts, then auto-restart with soft-start.                                                                                                       |

| Output Undervoltage  Low-side MOSFET (SG) and PWM MOSFET (PWMOUT) immediately off. If fault > 30 counts: FAL hiccup period, then auto-restart with soft-start.  Note: fault blanked for 3 ms during startup. |                                                                                                                                                                                                                                                        |

| Fixed-Output Overvoltage                                                                                                                                                                                     | Low-side MOSFET (SG) off and PWM MOSFET (PWMOUT) immediately turns off and FAULTn active, hiccup period after 1 count, then auto-restart with soft-start.                                                                                              |

| Programmable-Output Overvoltage                                                                                                                                                                              | Low-side MOSFET (SG) off and PWM MOSFET (PWMOUT) immediately turns off and FAULTn active, hiccup period after 1 count, then auto-restart with soft-start.                                                                                              |

| Input Undervoltage                                                                                                                                                                                           | Low-side MOSFET (SG) and PWM MOSFET (PWMOUT) immediately turns off and FAULTn active assuming there is sufficient drive to the flag. Once input voltage is above the VIN undervoltage threshold, plus hysteresis, auto-restart with soft-start occurs. |

| VREG Undervoltage                                                                                                                                                                                            | Low-side MOSFET (SG) immediately turns off and FAULTn active assuming there is sufficient drive to the flag. Once VREG voltage is above the VREG undervoltage threshold, plus hysteresis, then auto-restart.                                           |

| Thermal Shutdown                                                                                                                                                                                             | Low-side MOSFET (SG) immediately turns off and FAULTn active. Auto-restart with soft start occurs after the temperature drops below the overtemperature minus hysteresis level.                                                                        |

| PWMOUT Undervoltage                                                                                                                                                                                          | Low-side MOSFET (SG) off and PWM MOSFET (PWMOUT) off immediately and FAULTn active. Auto-restart with soft-start occurs.                                                                                                                               |

| OSC Pin Fault                                                                                                                                                                                                | The oscillator will switch to default frequency of 350 kHz.                                                                                                                                                                                            |

| COMP Short to GND                                                                                                                                                                                            | Force regulator to minimum duty cycle.                                                                                                                                                                                                                 |

### **COMPONENT SELECTION**

#### Inductor

The main factor in selecting the inductor value is to target a certain ripple current to ensure the peak current-mode control works correctly. A reasonable figure is a peak-to-peak ripple current of around 15% of the average inductor current. The maximum inductor current occurs at minimum input voltage and maximum duty cycle.

### **BOOST INDUCTOR SELECTION**

The maximum duty cycle can be found:

$$D_{MAX} = \frac{V_{LED} + (V_f - V_{IN(MIN)})}{V_{LED} + V_f}$$

where  $V_{LED}$  is the LED output voltage,  $V_f$  is the forward voltage drop of the recirculation diode, and  $V_{IN(MIN)}$  is the minimum input voltage.

The maximum average inductor current can be determined:

$$I_{AVE} = \frac{I_{LED}}{(1 - D_{MAX})}$$

The ripple current,  $\Delta I = 0.15 \times I_{AVE}$ .

The minimum inductance can now be found:

$$L = \frac{(V_{LED} + V_f - V_{IN(MIN)}) \times (1 - D_{MAX})}{\Delta I \times f_{SW}}$$

where  $f_{SW}$  is the switching frequency.

The peak current in the inductor is:

$$I_{LPK} = I_{AVE} + \frac{\Delta I}{2}$$

### **BUCK-BOOST INDUCTOR SELECTION**

The maximum duty cycle can be found:

$$D_{MAX} = \frac{V_{LED} + V_f}{V_{LED} + V_f + V_{IN(MIN)}}$$

where  $V_{LED}$  is the LED output voltage,  $V_f$  is the forward voltage drop of the recirculation diode, and  $V_{IN(MIN)}$  is the minimum input voltage.

The maximum average inductor current can be determined:

$$I_{AVE} = \frac{I_{LED}}{I - D_{MAX}}$$

The ripple current,  $\Delta I = 0.15 \times I_{AVE}$ .

The minimum inductance can now be found:

$$L = \frac{V_{IN(MIN)} \times D_{MAX}}{\Delta I \times f_{SW}}$$

where  $f_{SW}$  is the switching frequency.

The peak current in the inductor is:

$$I_{LPK} = I_{AVE} + \frac{\Delta I}{2}$$

When selecting an inductor from manufacturers' datasheets, there are often two current ratings given:

1. Saturation current. This is the current level that causes the inductance to drop by between 10 and 40% depending on the manufacturer.

The saturation current should be greater than the peak current,  $I_{LPK}$ , with some margin to allow for overload conditions.

RMS or average current. This is the current level that determines a certain temperature rise in the inductor with a given ambient temperature. This is normally presented as a single figure: operating temperature.

The RMS or average inductor current rating should be greater than the estimated maximum average current,  $I_{\rm AVE}$ .

Recommended inductor manufacturers:

· Coilcraft: MSS1278T or MSS1078T Range

TDK: SLF12575 type H

#### **SWITCH CURRENT SENSE**

The switch current sense of the 'inner loop' is measured by the external sense resistor,  $R_{\rm SS}$ , and the switch sense amplifier, AC. As well as providing the peak current information to determine the duty cycle, it also provides pulse-by-pulse current limiting through the switching MOSFET and slope compensation to prevent subharmonic oscillations at duty cycles greater than 50%.

The current limit of the inner loop is set by the input limit of the sense amplifier,  $V_{\rm IDS}$ , the maximum switch current that has been determined, and the effects of the slope compensation have to be taken into account. The operating duty cycle has to be calculated at maximum load and minimum operating input voltage. The amount of slope compensation can be calculated for this operating point and can then be added to the actual current-sense signal to determine the maximum signal amplitude before cycle-bycycle current limiting takes effect. Refer to Slope Compensation

Section to find  $di_L/dt$  then  $di_{SLOPE}/dt$ .

$$R_{SS} = \frac{0.32}{1.2 \times \left(I_{LP} + \left(\frac{di_{SLOPE}}{dt} \times \frac{D_{MAX}}{F_{SW}}\right)\right)}$$

Note that the minimum value of  $V_{\text{IDS}}$  is used with an additional 20% to allow for margin.

I<sub>LP</sub> is the peak current in the inductor.

The power loss of the switch current-sense resistor, R<sub>SS</sub>, can be found:

### **Boost Rss Power Loss**

Using the  $D_{MAX}$  and  $I_{AVE}$  from the boost part of the inductor section, the power loss of  $R_{SS}$  can be found:

$$P_{loss} = I_{AVE}^2 \times D_{MAX} \times R_{SS}$$

### **Buck-Boost Rss Power Loss**

Using the  $D_{MAX}$  and  $I_{AVE}$  from the buck-boost part of the inductor section, the power loss of  $R_{SS}$  can be found:

$$P_{loss} = I_{AVE}^2 \times D_{MAX} \times R_{SS}$$

Resistor manufacturers typically derate the devices from an ambient temperature of around 70°C. The power rating including derating of the sense resistor should exceed the maximum power loss at maximum ambient temperature.

### **SLOPE COMPENSATION**

Slope compensation can be added to the MOSFET current-sense signal on pin SP to prevent subharmonic oscillations where the peak-to-average control error becomes increasingly larger at duty cycles in excess of 50%. A current source is provided at the SP pin as a sawtooth from 0 to 100  $\mu A$ . An external resistor,  $R_{SLOPE}$ , connected between the SP pin and the source connection of the MOSFET, is used to program the appropriate voltage level to scale the slope compensation for correct use with the appropriate topology and set up conditions that have been adopted.

### **Boost Slope Resistor**

The inductor down slope is:

$$\frac{di_L}{dt} = \frac{V_{LED} + V_f - V_{IN(MIN)}}{L}$$

### **Buck-Boost Slope Resistor**

The inductor down slope is:

$$\frac{di_L}{dt} = \frac{V_{LED} + V_f}{L}$$

The optimum down slope as illustrated by Ridley can be found from:

$$\frac{di_{SLOPE}}{dt} = \frac{di_L}{dt} \times \left(1 - \frac{0.18}{D_{MAX}}\right)$$

The slope compensation resistor can be found:

$$R_{SLOPE} = \frac{\frac{di_{SLOPE}}{dt} \times R_{SS}}{100 \times 10^{-6} \times 1 \times 10^{-6} \times f_{SW}}$$

where  $R_{SLOPE}$  is in ohms ( $\Omega$ ).

### **CONTROL LOOP COMPENSATION**

The recommended way of closing the control loop is to remove the influence of the right-hand plane zero (RHPZ) in both boost and buck-boost topologies. The reason for this is that the RHPZ increases the gain by 20 dB/decade and at the same time introduces a 90-degree phase lag.

The minimum frequency that the RHPZ occurs at is:

For boost mode:

$$f_{RHPZ} = \frac{V_{LED} \times (1 - D_{MAX})^2}{2 \times \pi \times L \times I_{LED}}$$

For buck-boost mode:

$$f_{RHPZ} = \frac{V_{LED} \times (I - D_{MAX})^2}{2 \times \pi \times L \times I_{LED} \times D_{MAX}}$$

It is recommended that the 0 dB crossover point is approximately:

$$f_{CROSS} = \frac{f_{RHPZ}}{5}$$

With effective peak current-mode control, it can be assumed that the second power pole is pushed high enough in the frequency domain to have no influence on the overall loop response. It is reasonable to assume the overall loop response is effectively a single pole set by the GM amplifier (COMP node). The error

amp zero is set at the same frequency as the output power pole to ensure the loop is closed at a rate of 20 dB/decade.

The open-loop DC gain of the system can be found:

Boost:

$$DC Gain = \frac{5 \times 1,259 \times R_{SL} \times (1 - D_{MAX}) \times \left(\frac{V_{LED}}{I_{LED}}\right)}{R_{SS} \times \left(\left(\frac{V_{LED}}{I_{LED}}\right) + (n \times R_{dyn}) + R_{SL}\right)}$$

**Buck-Boost:**

$$DC \ Gain = \frac{5 \times 1,259 \times R_{SL} \times (1 - D_{MAX}) \times \left(\frac{V_{LED}}{I_{LED}}\right)}{R_{SS} \times \left(\left(\frac{V_{LED}}{I_{LED}}\right) + D_{MAX} \times ((n \times R_{dyn}) + R_{SL})\right)}$$

where n = number of LEDs and  $R_{dyn} = LED$  dynamic resistance.

Note that the LED dynamic resistance may be given in the LED datasheet. If it is not, it can be derived by a simple measurement. Set up a power supply with a current limit at the operating point ( $I_{LED1}$ ). Apply the current to an individual LED and measure the voltage drop ( $V_{LED1}$ ). Change the current limit by a small amount, say 5% ( $I_{LED2}$ ), and measure the voltage drop ( $V_{LED2}$ ). The dynamic resistance can be estimated:

$$R_{dyn} = \frac{V_{LED1} - V_{LED2}}{I_{LED1} - I_{LED2}}$$

The RC constant required to achieve 0 dB with a slope of 20 dB/decade at the crossover frequency,  $f_{\text{CROSS}}$ :

$$RC = \frac{1}{2 \times \pi \times f_{CROSS}}$$

The frequency of the first GM amplifier pole can be found:

$$f_{pl} = \frac{1}{2 \times \pi \times RC \times DC \ Gain}$$

Capacitor on the output of the GM amplifier (COMP node) required to achieve the above pole position:

$$C_{comp} = \frac{750 \times 10^{-6}}{2 \times \pi \times f_{pl} \times 1,258}$$

The frequency position of the power stage pole and the GM amplifier zero is:

Boost:

$$f_{p2}$$

and  $f_{zI} = \frac{V_{LED} + I_{LED} \times ((n \times R_{dyn}) + R_{SL})}{2 \times \pi \times V_{LED} \times C_{OUT} \times ((n \times R_{dyn}) + R_{SL})}$

**Buck-Boost:**

$$f_{p2} and f_{zl} = \frac{V_{LED} + D_{MAX} \times I_{LED} \times ((n \times R_{dyn}) + R_{SL})}{2 \times \pi \times V_{LED} \times C_{OUT} \times ((n \times R_{dyn}) + R_{SL})}$$

The resistor  $(R_{comp})$  in series with the compensation capacitor  $(C_{comp})$  on the COMP node can be found:

$$R_{comp} = \frac{1}{2 \times \pi \times f_{p2} \times C_{comp}}$$

### **LOW-SIDE SWITCHING MOSFET**

A logic-level n-channel MOSFET is used as the switch for the DC-DC converter.

In the boost configuration, the maximum voltage across the drain-source connection is:

$$V_{DS} = V_{LED} + V_f$$

In the buck-boost configuration, the maximum voltage across the drain-source connection is:

$$V_{DS} = V_{LED} + V_f + V_{INMAX}$$

The actual rating of the MOSFET selected should be greater than the maximum voltage plus some margin. It is recommended that the minimum margin should be no less than 20% of the maximum voltage.

In the case of buck-boost mode, the maximum rating should factor in load-dump conditions.

In terms of the current rating, the MOSFET is generally selected for a low  $R_{DS}$  rating to minimize the power dissipation. This means the current rating is well in excess of the actual maximum current used in the application.

The power loss in the MOSFET is determined by the static loss and the switching losses.

#### **Static Loss**

Using the  $D_{MAX}$  and  $I_{AVE}$  from the boost or buck-boost part of the inductor section, the power loss of  $R_{DS}$  can be found:

$$P_{loss} = I_{AVE}^{2} \times D_{MAX} \times R_{DS}$$

Note that the  $R_{DS}$  figures are generally presented at 25°C room ambients. The actual  $R_{DS}$  can be determined by considering the normalized  $R_{DS}$  versus temperature graph.

Another consideration of the static loss is cold-crank situations. It is important to ensure the gate-drive amplitude (derived from VREG) at the minimum input voltage provides sufficient drive that the  $R_{\rm DS}$  does not increase by much, therefore minimizing any increase in losses. A good quality logic-level MOSFET should have good  $R_{\rm DS}$  performance at drive voltages of less than 4 V.

The VREG load can be determined by estimating the gate losses. From the MOSFET datasheet, the total gate charge can estimated with a gate drive of 5 V using the appropriate graph. In addition, any other circuitry that VREG is powering should also be factored. The current drawn from VREG due to the MOSFET drive can be determined:

$$VREG_{MOSFETload} = Q_{TOTALGate} \times f_{SW}$$

### **Switching Losses**

The switching losses in the MOSFET are determined by the length of time of the Miller region. To minimize conducted and radiated EMI emissions, this region is deliberately extended by adding series resistance between the gate drive (SG) and the gate of the device. It is assumed that the turn-off loss is similar to the turn-on loss.

In the case of the boost converter, the switching loss:

$$P_{switch} = (V_{LED} + V_f) \times I_{AVE} \times t_{miller} \times f_{SW}$$

In the case of the buck boost converter, the switching loss:

$$P_{switch} = (V_{LED} + V_f + V_{IN(MIN)}) \times I_{AVE} \times t_{miller} \times f_{SW}$$

### **RECIRCULATION DIODE**

The diode should have a low forward voltage to reduce conduction losses and a low capacitance to reduce switching losses and minimize EMI. Schottky diodes can provide both features if carefully selected. The forward voltage drop is a natural advantage for Schottky diodes and reduces as the current rating increases. However, as the current rating increases, the diode capacitance also increases, so the optimum selection is usually the lowest current rating above the required maximum, in this case  $I_{\rm LPK}$ .

In the boost configuration, the maximum reverse voltage across the diode is:

$$V_{RRM} = V_{LED} + V_f$$

In the buck-boost configuration, the maximum reverse voltage across the diode is:

$$V_{RRM} = V_{LED} + V_f + V_{IN(MAX)}$$

The actual rating of the diode selected should be greater than the maximum voltage plus some margin. It is recommended that the minimum margin should be no less than 20% of the maximum voltage. In the case of buck-boost mode, the maximum rating should factor in load-dump conditions.

#### **HIGH-SIDE PWM MOSFET**

A p-channel MOSFET is used as the PWM switch for the LED stack.

In both boost and buck-boost modes, the maximum voltage across the drain-source connection is  $V_{\rm LED}$ . The actual rating of the MOSFET selected should be greater than the maximum voltage plus some margin. It is recommended that the minimum margin should be no less than 20% of the maximum voltage.

The power loss of this MOSFET is dominated by the static loss. The switching losses can largely be ignored as the PWM frequencies are relatively low.

The power loss of the MOSFET R<sub>DS</sub> can be found:

$$P_{loss} = I_{LED}^2 \times R_{DS}$$

The gate drive for the PWM MOSFET is derived from the LED output rail (LP pin). In boost and buck-boost modes, this node is boosted with respect to the input voltage ( $V_{IN}$ ), so there should be sufficient negative gate drive.

In other operating modes such as buck, where the output voltage is less than the input voltage, it may be necessary to use low threshold p-channel MOSFETs to ensure adequate overdrive during cold-crank situations.

#### **OUTPUT CAPACITOR**

There are several points to consider when selecting the output capacitor.

Due to the switching topology used, the ripple current for this circuit is high since the output capacitor provides the LED current when the DC-DC converter switch is active in both boost and buck-boost modes. The capacitor is then recharged each time the inductor passes energy to the output. The ripple current on the output capacitor will be equal to the peak inductor current. The corresponding output ripple can be derived from the amount of charge transferred to the output during the switch on time.

To minimize heating effects and voltage ripple, the equivalent series resistance (ESR) and the equivalent series inductance (ESL) should be kept as low as possible. This can be achieved by multilayer ceramic chip (MLCC) capacitors. To reduce performance variation over temperature, low drift types such as X7R and X5R should be used.

The value of the output capacitor will typically be in the range of 3.3 to 10  $\mu F$ , and it should be rated above the maximum LED stack voltage,  $V_{LED}$ . There is an E-field effect with ceramic capacitors that causes the capacitance to fall at elevated voltages. It is therefore recommended that a good margin is selected to minimize this effect.

One potential issue of ceramic capacitors is audible noise during pulse-width modulation (PWM). This is caused by the piezo-electric effect of the ceramic substrate. To minimize the effects of this, it is recommended to use multiple physically smaller capacitors. If this is still an issue, it is recommended that either low-impedance electrolytic or polymer capacitors be used.

### **INPUT CAPACITOR**

The function of the input filter capacitor is to provide a low-impedance shunt path for the current drawn by the A6271 when the switching MOSFET turns on. The objective is to minimize the ripple current reflected back into the source supply. This approach helps to minimize conducted emissions into the power source. Additional line impedance in the form of chokes can be added to improve the emissions further.

In a correctly designed system, with a quality capacitor or capacitors positioned adjacent to the power train circuitry, these capacitors should supply the ripple current.

The amount of capacitance required at the input is dictated by the EMI performance. This is usually distributed with series ferrite beads and either differential-mode chokes, or common-mode chokes, or both.

### Layout

The following layout guidelines should be followed to ensure satisfactory electrical and EMI performance.

Ground planes should be used on as many layers as possible. This is essential in minimizing 'ground bounce' (differential voltage across the ground connection). 'Ground bounce' can lead to radiated noise which can then be picked up on both input and output connections and manifest as common-mode noise. Any ground planes on different layers should be connected using multiple vias in an attempt to minimize ground impedances. The ground tab under the A6271 should also have multiple vias connecting to the ground plane or planes.