## 5.0 V, 750 mA Low Dropout Linear Regulator with Delayed RESET

The CS8126 is a low dropout, high current 5.0 V linear regulator. It is an improved replacement for the CS8156. Improvements include higher accuracy, tighter saturation control, better supply rejection, and enhanced RESET circuitry. Familiar PNP regulator features such as reverse battery protection, overvoltage shutdown, thermal shutdown, and current limit make the CS8126 suitable for use in automotive and battery operated equipment. Additional on-chip filtering has been included to enhance rejection of high frequency transients on all external leads.

An active microprocessor RESET function is included on-chip with externally programmable delay time. During power-up, or after detection of any error in the regulated output, the RESET lead will remain in the low state for the duration of the delay. Types of errors include short circuit, low input voltage, overvoltage shutdown, thermal shutdown, or others that cause the output to become unregulated. This function is independent of the input voltage and will function correctly with an output voltage as low as 1.0 V. Hysteresis is included in both the reset and Delay comparators for enhanced noise immunity. A latching discharge circuit is used to discharge the Delay capacitor, even when triggered by a relatively short fault condition. This circuit improves upon the commonly used SCR structure by providing full capacitor discharge (0.2 V type).

Note: The CS8126 is lead compatible with the LM2927 and LM2926.

## Features

- Low Dropout Voltage (0.6 V at 0.5 A)

- 3.0% Output Accuracy

- Active **RESET**

- External **RESET** Delay for Reset

- Protection Circuitry

- Reverse Battery Protection

- +60 V, -50 V Peak Transient Voltage

- Short Circuit Protection

- Internal Thermal Overload Protection

- These are Pb-Free Devices

## **ON Semiconductor®**

http://onsemi.com

### **ORDERING INFORMATION**

| Device          | Package                           | Shipping <sup>†</sup> |

|-----------------|-----------------------------------|-----------------------|

| CS8126-1YDPS7G  | D <sup>2</sup> PAK–7<br>(Pb–Free) | 50 Units / Rail       |

| CS8126-1YDPSR7G | D <sup>2</sup> PAK-7<br>(Pb-Free) | 750/Tape & Reel       |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

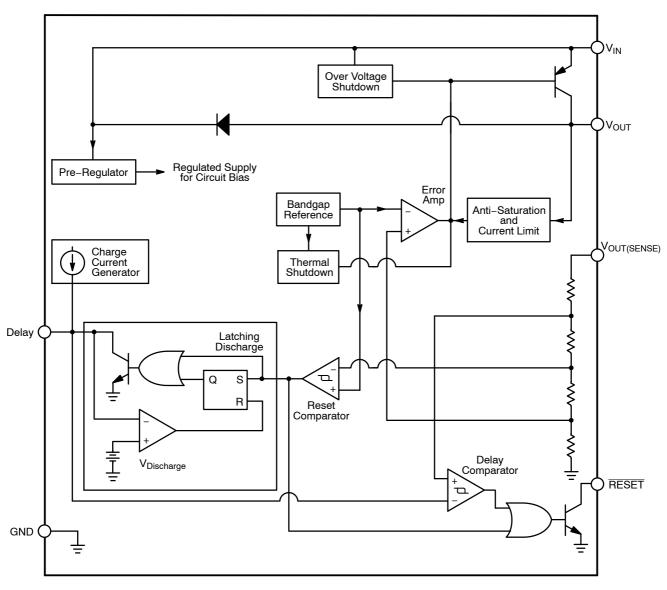

Figure 1. Block Diagram

### **MAXIMUM RATINGS\***

| Rating                                                                                                     | Value              | Unit         |

|------------------------------------------------------------------------------------------------------------|--------------------|--------------|

| Power Dissipation                                                                                          | Internally Limited | -            |

| Peak Transient Voltage (46 V Load Dump)                                                                    | -50, 60            | V            |

| Output Current                                                                                             | Internally Limited | -            |

| ESD Susceptibility (Human Body Model)                                                                      | 4.0                | kV           |

| Package Thermal Resistance:<br>Junction-to-Case, R <sub>θJC</sub><br>Junction-to-Ambient, R <sub>θJA</sub> | 2.1<br>10–50**     | °C/W<br>°C/W |

| Junction Temperature Range                                                                                 | -40 to +150        | °C           |

| Storage Temperature Range                                                                                  | –55 to +150        | °C           |

| Lead Temperature Soldering: Wave Solder (through hole styles<br>Reflow (SMD styles                         | , , , ,            | °C<br>℃      |

Maximum ratings are those values beyond which device damage can occur. Maximum ratings applied to the device are individual stress limit values (not normal operating conditions) and are not valid simultaneously. If these limits are exceeded, device functional operation is not implied, damage may occur and reliability may be affected.

1. 10 second maximum.

2. 60 second maximum above 183°C.

\*The maximum package power dissipation must be observed.

\*\*Depending on thermal properties of substrate.  $R_{\theta JA} = R_{\theta JC} + R_{\theta CA}$ .

# $\begin{array}{l} \textbf{ELECTRICAL CHARACTERISTICS} \quad (T_A = -40^\circ C \text{ to } +125^\circ C, \ T_J = -40^\circ C \text{ to } +150^\circ C, \ V_{IN} = 6.0 \text{ to } 26 \text{ V}, \\ I_O = 5.0 \text{ to } 500 \text{ mA}, \ R_{RESET} = 4.7 \text{ k}\Omega \text{ to } V_{CC}, \ unless otherwise noted.) \end{array}$

| Characteristic                           | Test Conditions                                                                             | Min  | Тур              | Max              | Unit           |

|------------------------------------------|---------------------------------------------------------------------------------------------|------|------------------|------------------|----------------|

| Output Stage (V <sub>OUT</sub> )         |                                                                                             |      |                  |                  |                |

| Output Voltage                           | _                                                                                           | 4.85 | 5.00             | 5.15             | V              |

| Dropout Voltage                          | I <sub>OUT1</sub> = 500 mA                                                                  | -    | 0.35             | 0.60             | V              |

| Supply Current                           | $I_{OUT} \le 10 \text{ mA}$<br>$I_{OUT} \le 100 \text{ mA}$<br>$I_{OUT} \le 500 \text{ mA}$ |      | 2.0<br>6.0<br>55 | 7.0<br>12<br>100 | mA<br>mA<br>mA |

| Line Regulation                          | $V_{IN}$ = 6.0 to 26 V, $I_{OUT}$ = 50 mA                                                   | -    | 5.0              | 50               | mV             |

| Load Regulation                          | $I_{OUT}$ = 50 to 500 mA, $V_{IN}$ = 14 V                                                   | -    | 10               | 50               | mV             |

| Ripple Rejection                         | f = 120 Hz, $V_{IN}$ = 7.0 to 17 V, $I_{OUT}$ = 250 mA                                      | 54   | 75               | -                | dB             |

| Current Limit                            | _                                                                                           | 0.75 | 1.20             | -                | Α              |

| Overvoltage Shutdown                     | _                                                                                           | 32   | -                | 40               | V              |

| Maximum Line Transient                   | V <sub>OUT</sub> ≤ 5.5 V                                                                    | -    | 95               | -                | V              |

| Reverse Polarity Input Voltage DC        | $V_{OUT} \ge -0.6 \text{ V}$ , 10 $\Omega$ Load                                             | -15  | -30              | -                | V              |

| Reverse Polarity Input Voltage Transient | 1.0% Duty Cycle, T < 100 ms, 10 $\Omega$ Load                                               | -    | -80              | -                | V              |

| Thermal Shutdown Note 3                  |                                                                                             | 150  | 180              | 210              | °C             |

3. Guaranteed By Design

# **ELECTRICAL CHARACTERISTICS (continued)** ( $T_A = -40^{\circ}C$ to $+125^{\circ}C$ , $T_J = -40^{\circ}C$ to $+150^{\circ}C$ , $V_{IN} = 6.0$ to 26 V, $I_O = 5.0$ to 500 mA, $R_{RESET} = 4.7 \text{ k}\Omega$ to $V_{CC}$ , unless otherwise noted.)

| Characteristic                    | Test Conditions                                                        | Min          | Тур          | Max                                                | Unit   |

|-----------------------------------|------------------------------------------------------------------------|--------------|--------------|----------------------------------------------------|--------|

| <b>RESET</b> and Delay Functions  |                                                                        |              |              |                                                    |        |

| Delay Charge Current              | V <sub>Delay</sub> = 2.0 V                                             | 5.0          | 10           | 15                                                 | μΑ     |

| RESET Threshold                   | $V_{OUT}$ Increasing, $V_{RT(ON)}$ $V_{OUT}$ Decreasing, $V_{RT(OFF)}$ | 4.65<br>4.50 | 4.90<br>4.70 | V <sub>OUT</sub> - 0.01<br>V <sub>OUT</sub> - 0.15 | V<br>V |

| RESET Hysteresis                  | $V_{RH} = V_{RT(ON)} - V_{RT(OFF)}$                                    | 150          | 200          | 250                                                | mV     |

| Delay Threshold                   | Charge, V <sub>DC(HI)</sub><br>Discharge, V <sub>DC(LO)</sub>          | 3.25<br>2.85 | 3.50<br>3.10 | 3.75<br>3.35                                       | V<br>V |

| Delay Hysteresis                  | _                                                                      | 200          | 400          | 800                                                | mV     |

| RESET Output Voltage Low          | 1.0 V < V_{OUT} < V_RTL, 3.0 k $\Omega$ to V_OUT                       | -            | 0.1          | 0.4                                                | V      |

| RESET Output Leakage Current      | V <sub>OUT</sub> > V <sub>RT(ON)</sub>                                 | -            | 0            | 10                                                 | μΑ     |

| Delay Capacitor Discharge Voltage | Voltage Discharge Latched "ON", V <sub>OUT</sub> > V <sub>RT</sub>     |              | 0.2          | 0.5                                                | V      |

| Delay Time                        | C <sub>Delay</sub> = 0.1 μF*. Note 4                                   |              | 32           | 48                                                 | ms     |

\*Delay Time =

$$\frac{C_{Delay} \times V_{Delay} | hreshold Charge}{|C_{harge}} = C_{Delay} \times 3.2$$

4. Assumes Ideal Capacitor

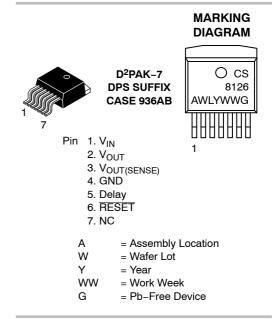

## PACKAGE LEAD DESCRIPTION

| PACKAGE LEAD # | LEAD SYMBOL              | FUNCTION                                                                                                                 |  |

|----------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| 1              | V <sub>IN</sub>          | Unregulated supply voltage to IC.                                                                                        |  |

| 2              | V <sub>OUT</sub>         | Regulated 5.0 V output.                                                                                                  |  |

| 4              | GND                      | Ground connection.                                                                                                       |  |

| 5              | Delay                    | Timing capacitor for RESET function.                                                                                     |  |

| 6              | RESET                    | CMOS/TTL compatible output lead. RESET goes low after detection of any error in the regulated output or during power up. |  |

| 3              | V <sub>OUT</sub> (SENSE) | Remote sensing of output voltage.                                                                                        |  |

| 7              | NC                       | No Connection.                                                                                                           |  |

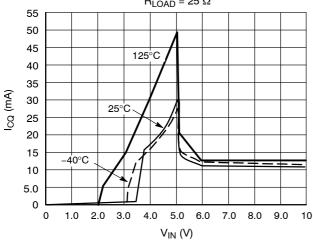

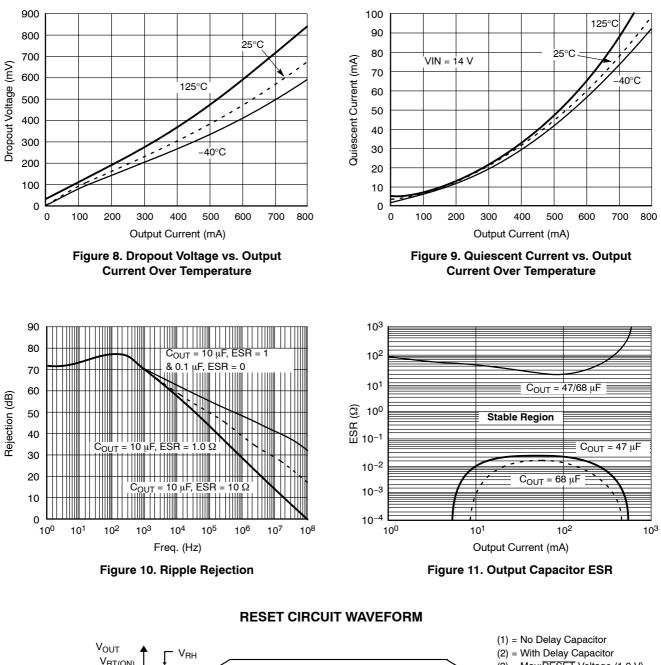

### **TYPICAL PERFORMANCE CHARACTERISTICS**

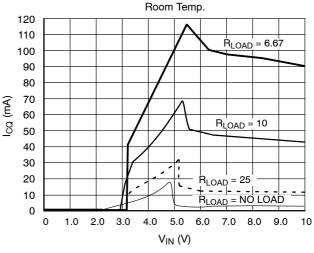

Figure 2. I<sub>CQ</sub> vs. V<sub>IN</sub> Over Temperature

Vout (V)

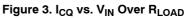

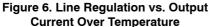

Figure 4. VOUT vs. VIN Over Temperature

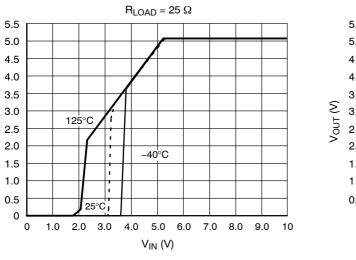

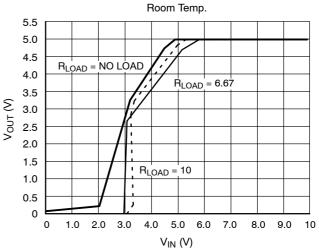

Figure 7. Load Regulation vs. Output **Current Over Temperature**

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

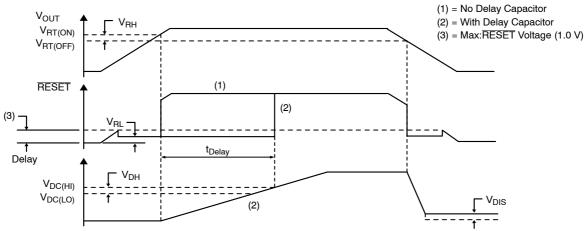

## Figure 12. RESET Circuit Waveform

## **CIRCUIT DESCRIPTION**

The CS8126 RESET function, has hysteresis on both the Reset and Delay comparators, a latching Delay capacitor discharge circuit, and operates down to 1.0 V.

The  $\overline{\text{RESET}}$  circuit output is an open collector type with ON and OFF parameters as specified. The  $\overline{\text{RESET}}$  output NPN transistor is controlled by the two circuits described (see Block Diagram).

### Low Voltage Inhibit Circuit

This circuit monitors output voltage, and when the output voltage falls below  $V_{RT(OFF)}$ , causes the RESET output transistor to be in the ON (saturation) state. When the output voltage rises above  $V_{RT(ON)}$ , this circuit permits the RESET output transistor to go into the OFF state if allowed by the RESET Delay circuit.

### **RESET** Delay Circuit

This circuit provides a programmable (by external capacitor) delay on the  $\overline{\text{RESET}}$  output lead. The Delay lead provides source current to the external delay capacitor only when the "Low Voltage Inhibit" circuit indicates that output

voltage is above  $V_{RT(ON)}$ . Otherwise, the Delay lead sinks current to ground (used to discharge the delay capacitor). The discharge current is latched ON when the output voltage falls below  $V_{RT(OFF)}$ . The Delay capacitor is fully discharged anytime the output voltage falls out of regulation, even for a short period of time. This feature ensures a controlled <u>RESET</u> pulse is generated following detection of an error condition. The circuit allows the <u>RESET</u> output transistor to go to the OFF (open) state only when the voltage on the Delay lead is higher than V<sub>DC(H1)</sub>.

The Delay time for the **RESET** function is calculated from the formula:

Delay time =

$$\frac{C_{Delay} \times V_{Delay} Threshold}{I_{Charge}}$$

Delay time =

$$C_{Delay} \times 3.2 \times 10^5$$

If  $C_{\text{Delay}} = 0.1 \,\mu\text{F}$ , Delay time (ms) = 32 ms  $\pm$  50%: i.e. 16 ms to 48 ms. The tolerance of the capacitor must be taken into account to calculate the total variation in the delay time.

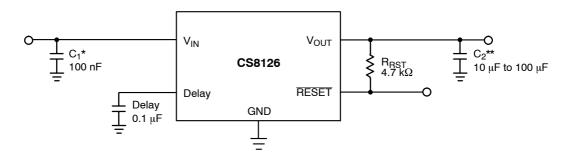

\* C<sub>1</sub> is required if the regulator is far from the power source filter.

\*\* C<sub>2</sub> is required for stability.

### Figure 13. Application Diagram

### **APPLICATION NOTES**

### **Stability Considerations**

The output or compensation capacitor helps determine three main characteristics of a linear regulator: start-up delay, load transient response and loop stability.

The capacitor value and type should be based on cost, availability, size and temperature constraints. A tantalum or aluminum electrolytic capacitor is best, since a film or ceramic capacitor with almost zero ESR, can cause instability. The aluminum electrolytic capacitor is the least expensive solution, but, if the circuit operates at low temperatures ( $-25^{\circ}$ C to  $-40^{\circ}$ C), both the value and ESR of the capacitor will vary considerably. The capacitor manufacturers data sheet usually provides this information.

The value for the output capacitor  $C_2$  shown in the test and applications circuit should work for most applications, however it is not necessarily the optimized solution.

To determine an acceptable value for  $C_2$  for a particular application, start with a tantalum capacitor of the recommended value and work towards a less expensive alternative part.

**Step 1:** Place the completed circuit with a tantalum capacitor of the recommended value in an environmental chamber at the lowest specified operating temperature and monitor the outputs with an oscilloscope. A decade box connected in series with the capacitor will simulate the higher ESR of an aluminum capacitor. Leave the decade box outside the chamber, the small resistance added by the longer leads is negligible.

**Step 2:** With the input voltage at its maximum value, increase the load current slowly from zero to full load while observing the output for any oscillations. If no oscillations are observed, the capacitor is large enough to ensure a stable design under steady state conditions.

**Step 3:** Increase the ESR of the capacitor from zero using the decade box and vary the load current until oscillations appear. Record the values of load current and ESR that cause the greatest oscillation. This represents the worst case load conditions for the regulator at low temperature.

**Step 4:** Maintain the worst case load conditions set in step 3 and vary the input voltage until the oscillations increase. This point represents the worst case input voltage conditions.

**Step 5:** If the capacitor is adequate, repeat steps 3 and 4 with the next smaller valued capacitor. A smaller capacitor will usually cost less and occupy less board space. If the output oscillates within the range of expected operating conditions, repeat steps 3 and 4 with the next larger standard capacitor value.

**Step 6:** Test the load transient response by switching in various loads at several frequencies to simulate its real working environment. Vary the ESR to reduce ringing.

**Step 7:** Raise the temperature to the highest specified operating temperature. Vary the load current as instructed in step 5 to test for any oscillations.

Once the minimum capacitor value with the maximum ESR is found, a safety factor should be added to allow for the tolerance of the capacitor and any variations in regulator performance. Most good quality aluminum electrolytic capacitors have a tolerance of  $\pm$  20% so the minimum value found should be increased by at least 50% to allow for this tolerance plus the variation which will occur at low temperatures. The ESR of the capacitor should be less than 50% of the maximum allowable ESR found in step 3 above.

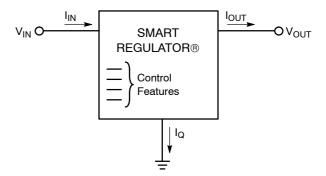

## Calculating Power Dissipation in a Single Output Linear Regulator

The maximum power dissipation for a single output regulator (Figure 14) is:

$P_{D(max)} = \{V_{IN(max)} - V_{OUT(min)}\} | OUT(max) + V_{IN(max)} | Q$ (1)

where:

$V_{IN(max)}$  is the maximum input voltage,

V<sub>OUT(min)</sub> is the minimum output voltage,

$I_{OUT(max)}$  is the maximum output current, for the application, and

$I_Q$  is the quiescent current the regulator consumes at  $I_{OUT(max)}$ .

Once the value of  $P_{D(max)}$  is known, the maximum permissible value of  $R_{0JA}$  can be calculated:

$$R_{\Theta JA} = \frac{150^{\circ}C - T_{A}}{P_{D}}$$

(2)

The value of  $R_{\theta JA}$  can then be compared with those in the package section of the data sheet. Those packages with  $R_{\theta JA}$ 's less than the calculated value in equation 2 will keep the die temperature below 150°C.

In some cases, none of the packages will be sufficient to dissipate the heat generated by the IC, and an external heatsink will be required.

Figure 14. Single Output Regulator With Key Performance Parameters Labeled

### **Heat Sinks**

A heat sink effectively increases the surface area of the package to improve the flow of heat away from the IC and into the surrounding air.

Each material in the heat flow path between the IC and the outside environment will have a thermal resistance. Like series electrical resistances, these resistances are summed to determine the value of  $R_{\theta JA}$ .

$$R_{\Theta JA} = R_{\Theta JC} + R_{\Theta CS} + R_{\Theta SA}$$

(3)

where:

$R_{\theta JC}$  = the junction-to-case thermal resistance,

$R_{\theta CS}$  = the case–to–heatsink thermal resistance, and

$R_{\theta SA}$  = the heatsink-to-ambient thermal resistance.

$R_{\theta JC}$  appears in the package section of the data sheet. Like  $R_{\theta JA}$ , it is a function of package type.  $R_{\theta CS}$  and  $R_{\theta SA}$  are functions of the package type, heatsink and the interface between them. These values appear in heat sink data sheets of heat sink manufacturers.

SMART REGULATOR is a registered trademark of Semiconductor Components Industries, LLC (SCILLC).

DATE 08 SEP 2009

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

0.310

0.136

4

0.050 PITCH

DIMENSIONS: MILLIMETERS

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " .", may or may not be present.

= Work Week

XXXXXXXXX

AWLYWWG

XXXXX = Specific Device Code

= Wafer Lot

= Year

А

Y

G

WI

WW

= Assembly Location

= Pb-Free Package

| DOCUMENT NUMBER:                                                                  | 98AON14119D                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                          |                                                       |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|

| DESCRIPTION:                                                                      | D <sup>2</sup> PAK-7 (SHORT LEAD)                                                           |                                                                                                                                                                                                                                                                                                              | PAGE 1 OF 1                                           |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | stries, LLC dba ON Semiconductor or its subsidiaries in the United States<br>y products herein. ON Semiconductor makes no warranty, representation<br>r assume any liability arising out of the application or use of any product or<br>cidental damages. ON Semiconductor does not convey any license under | or guarantee regarding<br>r circuit, and specifically |  |

Ε

1

SCALE 1:1

L1

D

7x b

⊕ 0.13 (M) B A (M)

0.584

7X 0.040 -

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative