Support & training

SLLSEX2E - DECEMBER 2016 - REVISED JULY 2022

## TDP158 6-Gbps, AC-Coupled to TMDS<sup>™</sup> or HDMI <sup>™</sup> Level Shifter Redriver

### 1 Features

Texas

INSTRUMENTS

- AC-coupled TMDS or DisplayPort<sup>™</sup> dual-mode physical layer input to HDMI 2.0b TMDS physical layer output supporting up to 6 Gbps data rate, compatible with HDMI 2.0b electrical parameters

- Supporting DisplayPort dual-mode standard version 1.1

- Support 4k2k60p and up to WUXGA 16-bit color depth or 1080p with higher refresh rates

- Programmable fixed receiver equalizer up to 15.5 dB

- Global or independent high speed lane control, pre-emphasis and transmit swing, and slew rate control

- I<sup>2</sup>C or pin strap programmable

- Configurable as a DisplayPort redriver through the l<sup>2</sup>C

- Full lane swap on main lanes

- Low power consumption

- 200 mW active at 6-Gbps and –8 mW at shutdown state

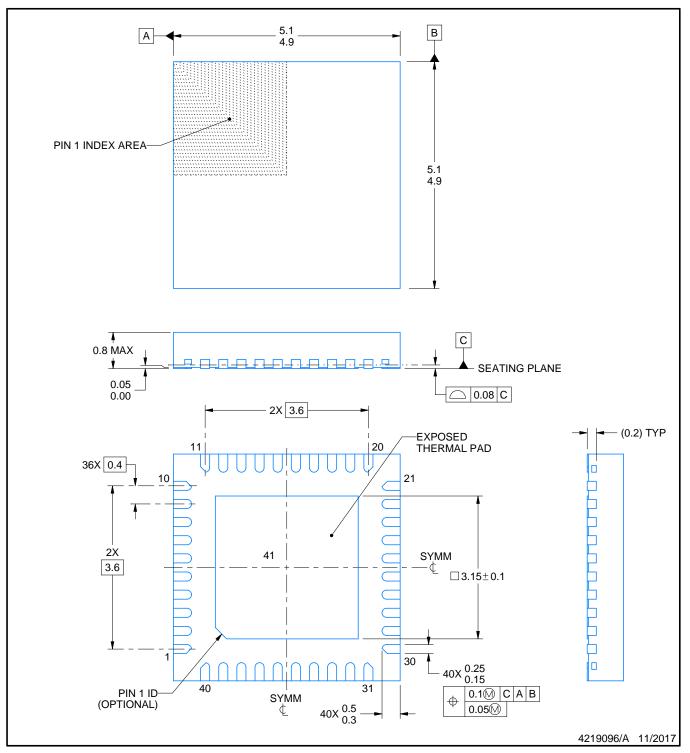

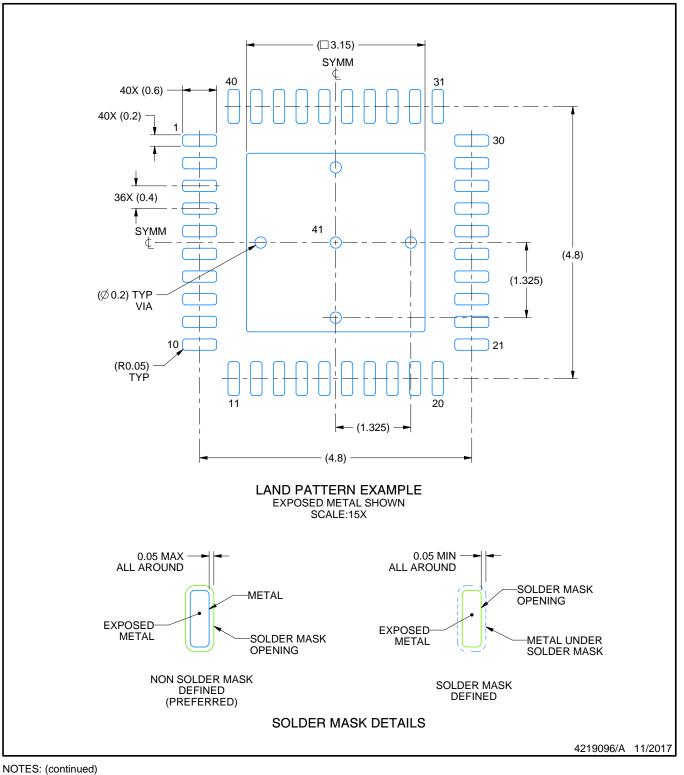

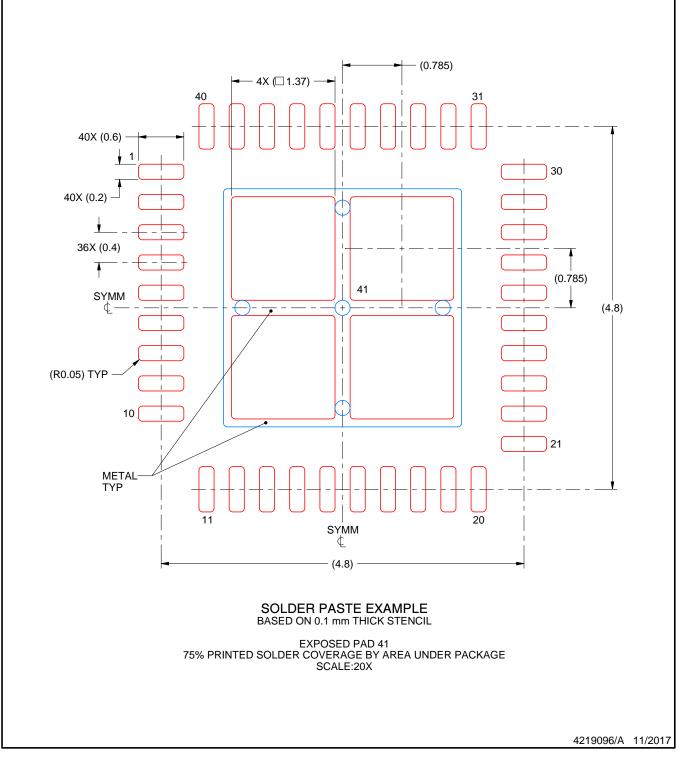

- 40-pin, 0.4 mm Pitch, 5 mm × 5 mm, WQFN package, pin compatible to the SN75DP159RSB retimer

### 2 Applications

- Notebook, desktop, all-in-ones, tablet, gaming and industrial PC

- Audio or video equipment

- Blu-ray<sup>™</sup> DVD

- Gaming systems

- HDMI adaptor or dongle

- Docking station

### **3 Description**

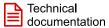

The TDP158 device is an AC-coupled HDMI signal to transition-minimized differential signal (TMDS) Redriver supporting digital video interface (DVI) 1.0 and high-definition multimedia interface (HDMI) 1.4b and 2.0b output signals. The TDP158 supports four TMDS channels and Digital Display Control (DDC) interfaces. The TDP158 supports signaling rates up to 6 Gbps to allow for the highest resolutions of 4k2k60p 24 bits per pixel and up to WUXGA 16-bit color depth or 1080p with higher refresh rates. The TDP158 can be configured to support the HDMI 2.0 standard.

The TDP158 supports dual power supply rails of 1.1 V on V<sub>DD</sub> and 3.3 V on V<sub>CC</sub> for power reduction. Several methods of power management are implemented to reduce overall power consumption. TDP158 supports fixed receiver EQ gain using  $I^2C$  or pin strap to compensate for different lengths input cable or board traces.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| TDP158      | WQFN (40) | 5.00 mm × 5.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

### **Table of Contents**

| 1 | Features                                                 | 1              |

|---|----------------------------------------------------------|----------------|

| 2 | Applications                                             | 1              |

|   | Description                                              |                |

| 4 | Revision History                                         | 2              |

|   | Pin Configuration and Functions                          |                |

| 6 | Specifications                                           | 6              |

|   | 6.1 Absolute Maximum Ratings                             |                |

|   | 6.2 ESD Ratings                                          |                |

|   | 6.3 Recommended Operating Conditions                     | <mark>6</mark> |

|   | 6.4 Thermal Information                                  |                |

|   | 6.5 Electrical Characteristics, Power Supply             | 8              |

|   | 6.6 Electrical Characteristics, Differential Input       | 9              |

|   | 6.7 Electrical Characteristics, TMDS Differential        |                |

|   | Output                                                   | 9              |

|   | 6.8 Electrical Characteristics, DDC, I2C, HPD, and       |                |

|   | ARC                                                      | 9              |

|   | 6.9 Electrical Characteristics, TMDS Differential        |                |

|   | Output in DP-Mode                                        | 10             |

|   | 6.10 Switching Characteristics, TMDS                     | 10             |

|   | 6.11 Switching Characteristics, HPD                      | 10             |

|   | 6.12 Switching Characteristics, DDC and I <sup>2</sup> C | 11             |

|   | 6.13 Typical Characteristics                             | 12             |

| 7 | Parameter Measurement Information                        | 13             |

| 8 | Detailed Description                                     | 19             |

|   |                                                          |                |

| 8.1 Overview                                          | 19  |

|-------------------------------------------------------|-----|

| 8.2 Functional Block Diagram                          | 20  |

| 8.3 Feature Description                               |     |

| 8.4 Device Functional Modes                           | .27 |

| 8.5 Register Maps                                     |     |

| 9 Application and Implementation                      |     |

| 9.1 Application Information                           |     |

| 9.2 Typical Application                               |     |

| 10 Power Supply Recommendations                       |     |

| 10.1 Power Management                                 |     |

| 10.2 Standby Power                                    |     |

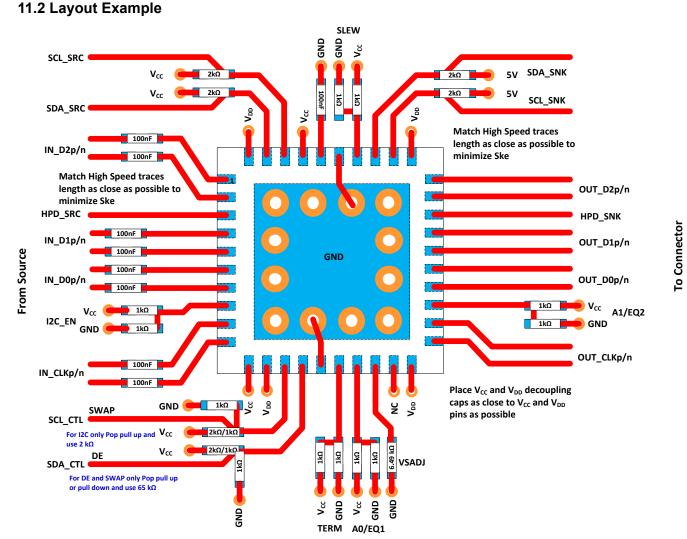

| 11 Layout                                             |     |

| 11.1 Layout Guidelines                                |     |

| 11.2 Layout Example                                   |     |

| 12 Device and Documentation Support                   |     |

| 12.1 Documentation Support                            |     |

| 12.2 Receiving Notification of Documentation Updates. |     |

| 12.3 Support Resources                                |     |

| 12.4 Trademarks                                       |     |

| 12.5 Electrostatic Discharge Caution                  |     |

| 12.6 Glossary                                         |     |

| 13 Mechanical, Packaging, and Orderable               |     |

| Information                                           | 48  |

|                                                       | .0  |

### **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| С | hanges from Revision D (March 2020) to Revision E (July 2022)                                                   | Page |

|---|-----------------------------------------------------------------------------------------------------------------|------|

| • | Updated the numbering format for tables, figures, and cross-references throughout the document                  | 1    |

| • | Added inclusive terminology throughout the data sheet                                                           | 1    |

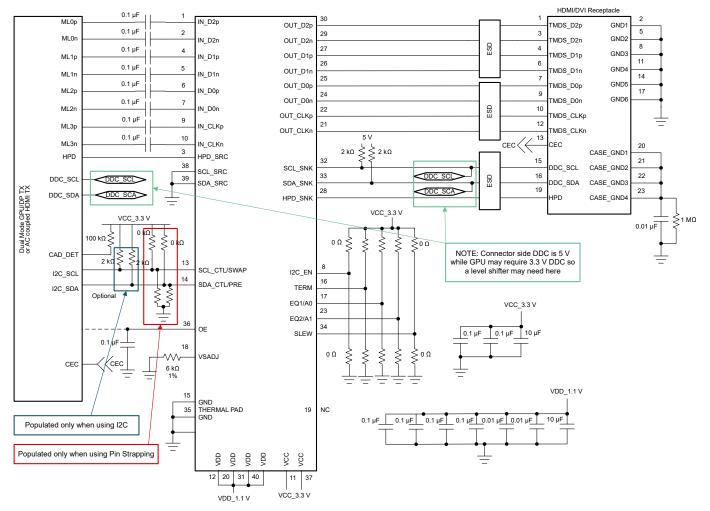

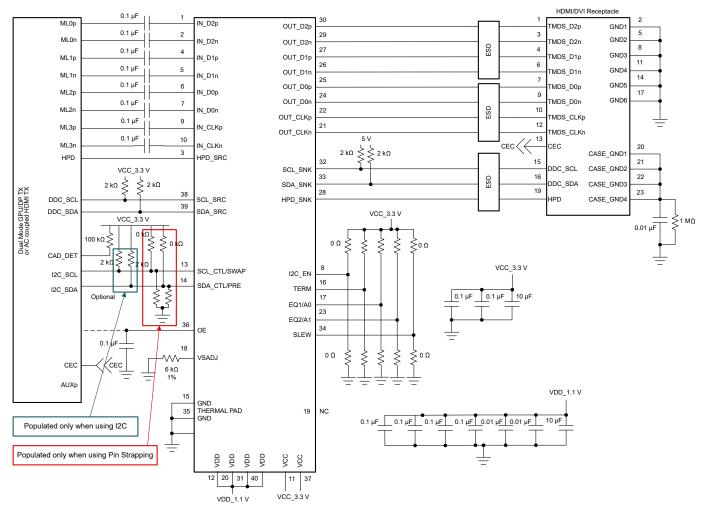

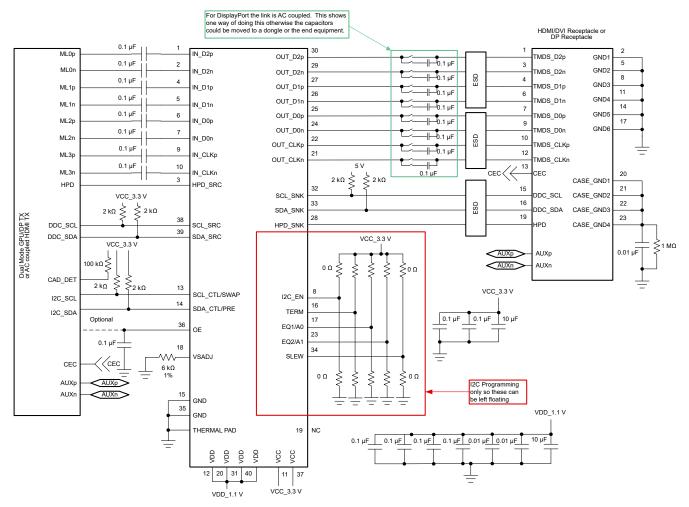

| • | Updated the TDP158 in Source Side Application figure with ESD between device and receptacle                     | 39   |

| • | Updated the <i>TDP158 Source Side Application with DDC Snoop</i> figure with ESD between device and receptacle. | 43   |

| • | Updated the <i>TDP158 in Dual Role Source Side Application</i> figure with ESD between device and recepted 44   |      |

| Changes from Revision C (October 2019) to Revision D (March 2020) |                                | Page |

|-------------------------------------------------------------------|--------------------------------|------|

| •                                                                 | Changed HDMI 2.0a to HDMI 2.0b | 1    |

| С | hanges from Revision B (June 2017) to Revision C (October 2019)                                        | Page |

|---|--------------------------------------------------------------------------------------------------------|------|

| • | Deleted Feature: Both Extended Commercial and Industrial Temperature Device Options                    | 1    |

| • | Changed Feature: From: Pin Compatible to the SN65DP159RSB and SN75DP159RSB Retimer To: Pin             | n    |

|   | Compatible to the SN75DP159RSB Retimer                                                                 | 1    |

| • | Deleted TDP158I from the Device Information table                                                      | 1    |

| • | Changed the T <sub>J</sub> MIN value From: -40°C To: 0°C in the Recommended Operating Conditions table | 6    |

| • | Deleted T <sub>A</sub> for TDP158I in the Recommended Operating Conditions table                       |      |

| • | Changed the last sentence of the Overview section to remove the TDP158I device                         |      |

| С | hanges from Revision A (January 2017) to Revision B (June 2017)                                        | Page |

| • | Changed the title From: "HDMI ™ Redriver" To: "HDMI ™ Level Shifter Redriver"                          | 1    |

| • | Changed the Features List                                                                              |      |

|   | Changed the Applicational ist                                                                          | 4    |

Changed the Applications List......

| • | Changed From: Preview To: Production data                                                                                                                                                                                           | 1    |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| С |                                                                                                                                                                                                                                     | age  |

| • | Changed From. 0 12 resistors to. 1 K12 resistors, and a noise liner (capacitor) for the no connect in Figure 1                                                                                                                      |      |

|   | Changed From: 0 $\Omega$ resistors To: 1 k $\Omega$ resistors, and a noise filter (capacitor) for the no connect in Figure 1                                                                                                        |      |

| • | Changed From: 0 $\Omega$ resistors To: 1 k $\Omega$ resistors, and a noise filter (capacitor) for the no connect in Figure 9                                                                                                        | 9-6  |

| • | Changed From: 0 $\Omega$ resistors To: 1 k $\Omega$ resistors, and a noise filter (capacitor) for the no connect in Figure 9                                                                                                        |      |

| _ | pulldown to GND, or left floating."                                                                                                                                                                                                 | 43   |

|   | be tied directly to VCC, GND or left floating." To: "Control pins should be tied to 1 k $\Omega$ pullup to VCC, 1 k $\Omega$                                                                                                        |      |

| : | Changed text in the second paragraph of the Source Side HDMI Application section From: "Control pins ca                                                                                                                             |      |

| • | Added text "1 kΩ pulldown resistor " to the Connect values in Table 9-1                                                                                                                                                             |      |

| • | Changed From: 0 $\Omega$ resistors To: 1 k $\Omega$ resistors, and a noise filter (capacitor) for the no connect in Figure 9                                                                                                        |      |

| • | Changed the Application Information paragraph                                                                                                                                                                                       | . 39 |

| • | Added paragraph to the Application and Implementation section: "TDP158 is designed"                                                                                                                                                 |      |

| • | Changed the Default setting in Table 8-9 From: TBD To: 00000001                                                                                                                                                                     |      |

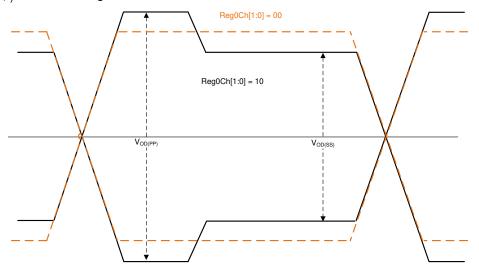

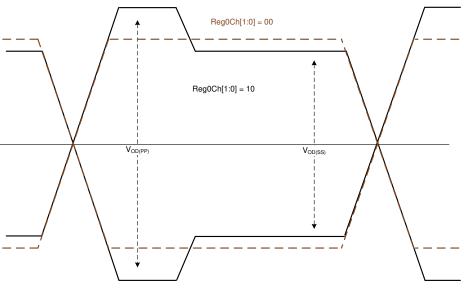

| • | Changed From: Reg0Ch[1:0] = 01 To: Reg0Ch[1:0] = 10 in Figure 8-7                                                                                                                                                                   |      |

| • | Changed the title of Figure 8-6 From: 3.5 dB pre-emphasis in Normal Operation To: 6 dB pre-emphasis Setting in Normal Operation                                                                                                     | 26   |

| • | Changed the last two sentences of the paragraph in the <i>pre-emphasis</i> section                                                                                                                                                  | . 26 |

| • | Changed Note 1 of Table 8-3                                                                                                                                                                                                         |      |

|   | row of the SWAP column                                                                                                                                                                                                              |      |

| • | Added column Pin Number to Table 8-2, Changed IN_CLK $\rightarrow$ OUT_CLK To: IN_D2 $\rightarrow$ OUT_D2 in the last                                                                                                               |      |

| • | Changed the paragraph in the Operation Timing section                                                                                                                                                                               | 21   |

| • | Changed Rvsdj max value to 8 k $\Omega$ in Figure 6-1                                                                                                                                                                               |      |

| • | table                                                                                                                                                                                                                               |      |

| • | Added text to pin NC in the <i>Pin Functions</i> table: "Optionally connect 0.1 µF to GND to reduce noise"<br>V <sub>SADJ</sub> : Added Note "Reducing resistor", and Changed values in the <i>Recommended Operating Conditions</i> |      |

|   | GND, High = 1 k $\Omega$ pullup resistor to VCC, NC = Floating"                                                                                                                                                                     |      |

| • | Added text to pins 17, 23, 34, 16 in the <i>Pin Functions</i> table: "For pin control, Low = 1 k $\Omega$ pulldown resistor                                                                                                         |      |

|   |                                                                                                                                                                                                                                     |      |

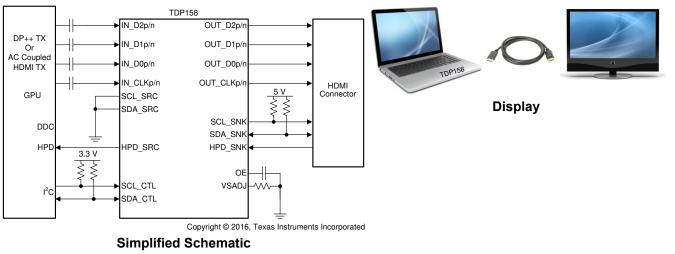

### **5** Pin Configuration and Functions

### Figure 5-1. RSB Package, 40-Pin WQFN (Top View)

| PIN        |                       | TYPE <sup>(1)</sup> | DESCRIPTION                         |

|------------|-----------------------|---------------------|-------------------------------------|

| NAME       | NO.                   | ITPE                | DESCRIPTION                         |

|            | 1                     |                     | SUPPLY AND GROUND PINS              |

| VCC        | 11, 37                | Р                   | 3.3 V Power Supply                  |

| VDD        | 12,20,31,40           | Р                   | 1.1 V Power Supply                  |

| GND        | 15, 35<br>Thermal Pad | G                   | Ground                              |

|            |                       |                     | MAIN LINK INPUT PINS                |

| IN_D2p/n   | 1, 2                  | Ι                   | Channel 2 Differential Input        |

| IN_D1p/n   | 4, 5                  | Ι                   | Channel 1 Differential Input        |

| IN_D0p/n   | 6, 7                  | I                   | Channel 0 Differential Input        |

| IN_CLKp/n  | 9, 10                 | I                   | Clock Differential Input            |

|            |                       |                     | MAIN LINK OUTPUT PINS (FAIL SAFE)   |

| OUT_D2n/p  | 29, 30                | 0                   | TMDS Data 2 Differential Output     |

| OUT_D1n/p  | 26, 27                | 0                   | TMDS Data 1 Differential Output     |

| OUT_D0n/p  | 24, 25                | 0                   | TMDS Data 0 Differential Output     |

| OUT_CLKn/p | 21, 22                | 0                   | TMDS Data Clock Differential Output |

#### Table 5-1. Pin Functions

#### Table 5-1. Pin Functions (continued)

| PIN          |                                                                                                                                                            |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME         | NO.                                                                                                                                                        | - TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|              | HOT PLUG DETECT AND DDC PINS                                                                                                                               |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| HPD_SRC      | 3                                                                                                                                                          | 0                     | Hot Plug Detect Output to source side                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| HPD_SNK      | 28                                                                                                                                                         | I                     | Hot Plug Detect Input from sink side                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SDA_SNK      | 33                                                                                                                                                         | I/O                   | Sink Side Bidirectional DDC Data Line                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| SCL_SNK      | 32                                                                                                                                                         | I/O                   | Sink Side Bidirectional DDC Clock Line                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| SDA_SRC      | 39                                                                                                                                                         | I/O                   | Source Side Bidirectional DDC Data Line                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| SCL_SRC      | 38                                                                                                                                                         | I/O                   | Source Side Bidirectional DDC Clock Line                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|              |                                                                                                                                                            |                       | CONTROL PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| OE           | 36 I Operation Enable/Reset Pin<br>OE = L: Power Down Mode<br>OE = H: Normal Operation<br>Internal weak pullup: Resets device when transitions from H to L |                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| I2C_EN       | 8                                                                                                                                                          | I                     | I2C_EN = High; Puts Device into I2C Control Mode<br>I2C_EN = Low; Puts Device into Pin Strap Mode                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| SDA_CTL/PRE  | 14                                                                                                                                                         | 1/0                   | I2C Data Signal: When I2C_EN = High;<br>Pre-emphasis: When I2C_EN = Low: See Section 8.3.11<br>DE = L: None 0 dB<br>DE = H: 3.5 dB                                                                                                                                                                                                                                                                                                                                     |  |  |

| SCL_CTL/SWAP | 13                                                                                                                                                         | I                     | I2C Clock Signal: When I2C_EN = High;<br>Lane SWAP: When I2C_EN = Low: See Section 8.3.4 HDMI Mode Only<br>SWAP = L: Normal Operation<br>SWAP = H: Lane Swap                                                                                                                                                                                                                                                                                                           |  |  |

| VSADJ        | 18                                                                                                                                                         | I                     | TMDS Compliant Voltage Swing Control (Nominal 6 k $\Omega$ for HDMI and DP combination; 6.49 k $\Omega$ for HDMI only)                                                                                                                                                                                                                                                                                                                                                 |  |  |

| A0/EQ1       | 17                                                                                                                                                         | l<br>3 Level          | Address Bit 1 for I2C Programming when I2C_EN = High<br>EQ1 Pin Setting when I2C_EN = Low; Works in conjunction with A1/EQ2; See Section<br>8.3.5 for settings. For pin control, Low = 1 k $\Omega$ pulldown resistor to GND, High = 1 k $\Omega$<br>pullup resistor to VCC, NC = Floating.                                                                                                                                                                            |  |  |

| A1/EQ2       | 23                                                                                                                                                         | l<br>3 Level          | Address Bit 2 for I2C Programming when I2C_EN = High<br>EQ2 Pin Setting when I2C_EN = Low; Works in conjunction with A0/EQ1; See Section<br>8.3.5 for settings. For pin control, Low = 1 k $\Omega$ pulldown resistor to GND, High = 1 k $\Omega$<br>pullup resistor to VCC, NC = Floating.                                                                                                                                                                            |  |  |

| SLEW         | 34                                                                                                                                                         | l<br>3 Level          | Clock Slew Rate Control: See Section 8.3.10<br>SLEW = L: Slowest $\cong$ 203 ps<br>SLEW = NC (Default): Mid-range 1 $\cong$ 180 ps<br>SLEW = H: Fastest $\cong$ 122 ps<br>For pin control, L = 1 k $\Omega$ pulldown resistor to GND, H = 1 k $\Omega$ pullup resistor to VCC, NC =<br>Floating.                                                                                                                                                                       |  |  |

| TERM         | 16                                                                                                                                                         | l<br>3 Level          | Source Termination Cotnrol: See Section 8.3.8<br>TERM = H, 75 $\Omega \cong 150 \Omega$<br>TERM = L, Transmit Termination impedance in 150 $\Omega \cong 300 \Omega$<br>TERM = NC, No transmit Termination<br>Note: When TMDS_CLOCK_RATIO_STATUS bit = 1 the TDP158 sets source termination<br>to 75 $\Omega \cong 150 \Omega$ Automatically<br>For pin control, L = 1 k $\Omega$ pulldown resistor to GND, H = 1 k $\Omega$ pullup resistor to VCC, NC =<br>Floating. |  |  |

| NC           | 19                                                                                                                                                         | NA                    | No Connect. Optionally connect 0.1 $\mu$ F to GND to reduce noise.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

(1) I= Input, O = Output, P = Power, G = Ground

# 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup> (2)

|                                                                                          |                                                                                                           | MIN  | MAX           | UNIT |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|------|---------------|------|

|                                                                                          | VCC                                                                                                       | -0.3 | 4             | V    |

| Supply Voltage Range <sup>(3)</sup>                                                      | VDD                                                                                                       | -0.3 | 1.4           | V    |

|                                                                                          | Main Link Input Differential Voltage (IN_Dx)                                                              | 0    | 1.56          | V    |

| Voltage Range TMDS Output ( OU<br>HPD_SRC, VSADJ<br>A1/EQ2, A0/EQ1, T<br>SCL_CTL/SWAP, S | Main Link Input Single Ended on Pin                                                                       | -0.3 | 1.4           | V    |

|                                                                                          | TMDS Output ( OUT_Dx)                                                                                     | -0.3 | 4             | V    |

|                                                                                          | HPD_SRC, VSADJ, SDA_CTL/PRE, OE,<br>A1/EQ2, A0/EQ1, TERM, I2C_EN, SLEW,<br>SCL_CTL/SWAP, SDA_SRC, SCL_SRC | -0.3 | 4             | V    |

|                                                                                          | HDP_SNK, SDA_SNK, SCL_SNK                                                                                 | -0.3 | 6             | V    |

| Continuous power dissipation                                                             |                                                                                                           |      | See Section 6 | .4   |

| Storage temperature, T <sub>stg</sub>                                                    |                                                                                                           | -65  | 150           | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values, except differential voltages, are with respect to network ground terminal.

(3) Tested in accordance with JEDEC Standard 22, Test Method A114-B.

### 6.2 ESD Ratings

|   |                    |                         |                                                                                | VALUE | UNIT |

|---|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|   |                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 |      |

| ľ | V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                      |                                                                                                                                             |                                                         | MIN  | NOM MAX | UNIT |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|---------|------|

| V <sub>CC</sub>      | Supply Voltage Nomi                                                                                                                         | nal Value 3.3 V for DP mode                             | 3    | 3.6     | V    |

|                      | Supply Voltage Nomin                                                                                                                        | nal Value 3.3 V for HDMI mode                           | 3.13 | 3.47    | V    |

| V <sub>DD</sub>      | Supply Voltage Nomin                                                                                                                        | nal Value 1.1 V                                         | 1    | 1.27    | V    |

| TJ                   | T <sub>J</sub> Junction temperature                                                                                                         |                                                         | 0    | 105     | °C   |

| T <sub>A</sub>       |                                                                                                                                             |                                                         | 0    | 85      | °C   |

| MAIN LIN             | K DIFFERENTIAL PINS                                                                                                                         |                                                         |      |         |      |

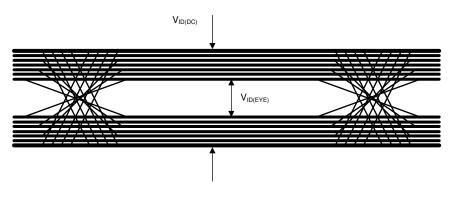

| V <sub>ID(EYE)</sub> | Peak-to-peak input di                                                                                                                       | fferential voltage See Figure 7-14                      | 75   | 1200    | mV   |

| V <sub>ID(DC)</sub>  | The input differential                                                                                                                      | voltage Peak-to peak DC level, See Figure 7-14          | 200  | 1200    | mV   |

| V <sub>IC</sub>      | Input Common Mode                                                                                                                           | Voltage (Internally Biased)                             | 0.5  | 0.9     | V    |

| d <sub>R</sub>       | Data rate                                                                                                                                   |                                                         | 0.25 | 6       | Gbps |

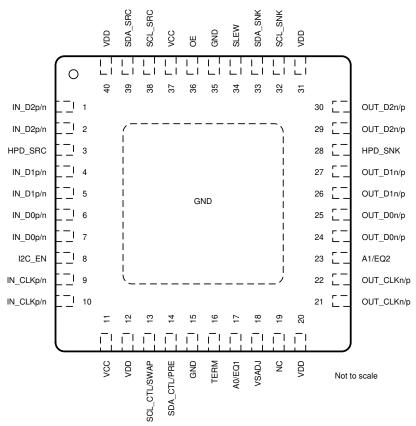

| V <sub>SADJ</sub>    | TMDS compliant swing voltage bias resistor (Nominal 6 k $\Omega$ for HDMI and DP combination; 6.49 k $\Omega$ for HDMI only) <sup>(1)</sup> |                                                         | 4.5  | 8       | kΩ   |

| DDC, I2C,            | HPD, AND CONTROL F                                                                                                                          | PINS                                                    |      |         |      |

| V <sub>I(DC)</sub>   | DC Input Voltage                                                                                                                            | HDP_SNK, SDA_SNK, SCL_SNK,                              | -0.3 | 5.5     | V    |

|                      |                                                                                                                                             | SDA_SRC, SCL_SRC; All other Local I2C, and control pins | -0.3 | 3.6     | V    |

### 6.3 Recommended Operating Conditions (continued)

over operating free-air temperature range (unless otherwise noted)

|                        |                                                                                                        | MIN                   | NOM MAX               | UNIT |

|------------------------|--------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>IL</sub>        | Low-level input voltage at DDC                                                                         |                       | 0.3 x V <sub>CC</sub> | V    |

|                        | Low-level input voltage at HPD                                                                         |                       | 0.8                   | V    |

|                        | Low-level input voltage at SDA_CTL/PRE, OE, A1/EQ2, A0/EQ1, TERM, I2C_EN, SLEW, SCL_CTL/SWAP pins only |                       | 0.3                   | V    |

| V <sub>IM</sub>        | Mid-Level input voltage at A1/EQ2, A0/EQ1, TERM, SLEW pins only                                        | 1.2                   | 1.6                   | V    |

| V <sub>IH</sub>        | High-level input voltage at OE, A1/EQ2, A0/EQ1, TERM, I2C_EN, SLEW pins only                           | 0.7 x V <sub>CC</sub> |                       | V    |

|                        | High-level input voltage at SDA_SRC, SCL_SRC, SDA_CTL/PRE, SCL_CTL/SWAP                                | 0.7 x V <sub>CC</sub> |                       | V    |

|                        | High-level input voltage at SDA_SNK, SCL_SNK                                                           | 3.2                   |                       | V    |

|                        | High-level input voltage at HPD                                                                        | 2                     |                       | V    |

| V <sub>OL</sub>        | Low-level output voltage                                                                               |                       | 0.4                   | V    |

| V <sub>OH</sub>        | High-level output voltage                                                                              | 2.4                   |                       | V    |

| f <sub>SCL</sub>       | SCL clock frequency fast I <sup>2</sup> C mode for local I2C control                                   |                       | 400                   | kHz  |

| C <sub>(bus,DDC)</sub> | Total capacitive load for each bus line supporting 400 kHz (DDC terminals)                             |                       | 400                   | pF   |

| C <sub>(bus,I2C)</sub> | Total capacitive load for each bus line (local I2C terminals)                                          |                       | 100                   | pF   |

| d <sub>R(DDC)</sub>    | DDC Data rate                                                                                          |                       | 400                   | Kbps |

| I <sub>IH</sub>        | High level input current                                                                               | -30                   | 30                    | μA   |

| IIM                    | Mid level input current                                                                                | -20                   | 20                    | μA   |

| IIL                    | Low level input current                                                                                | -10                   | 10                    | μA   |

| I <sub>OZ</sub>        | High impedance outpupt current                                                                         |                       | 10                    | μA   |

| R <sub>(OEPU)</sub>    | Pull up resistance on OE pin                                                                           | 150                   | 250                   | kΩ   |

(1) Reducing resistor in  $V_{SADJ}$  will increase  $V_{OD}$ , care should be taking since resistors below  $\cong 6 \text{ k}\Omega$  may lead to compliance failures.

#### 6.4 Thermal Information

|                       |                                              | TDP158     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RSB (WQFN) | UNIT |

|                       |                                              | 40 PINS    |      |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 3.7        | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 23.1       | °C/W |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 9.9        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.3        | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 3.8        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 3.2        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics, Power Supply

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                 | TEST CONDITIO                                                                                         | NS                         | MIN | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|---------------------|-------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------|-----|--------------------|--------------------|------|

|                     |                                           | OE = H, <sub>VCC</sub> = 3.3 V/3.6 V, V <sub>D</sub><br>V                                             | <sub>D</sub> = 1.1 V/1.27  |     |                    |                    |      |

| P <sub>D1</sub>     | Device power Dissipation                  | IN_Dx: VID_PP = 1200 mV, 6<br>TMDS pattern, V <sub>I</sub> = 3.3 V, I20<br>SDA_CTL/PRE = L, EQ1/EQ2   | _EN = L,                   |     | 200                | 350                | mW   |

|                     |                                           | OE = H, V <sub>CC</sub> = 3.3 V/3.6 V, V <sub>I</sub>                                                 | <sub>DD</sub> = 1.1 V/1.27 |     | 330                | 680                | mW   |

| P <sub>D2</sub>     | Device power Dissipation in DP-<br>Mode   | IN_Dx: VID_PP = 400 mV, 5.4<br>pattern, I2C_EN = H, V <sub>OD</sub> = 4<br>= 0 dB                     |                            |     |                    |                    |      |

| 7                   | Stage 1: Standby Power                    | OE = H, V <sub>CC</sub> = 3.3 V/3.6 V, V<br>V , HPD = H, No input Signal:<br>Section 10.2             |                            |     |                    | 34                 | mW   |

| O(STBY1)            | Stage 2: Standby Power                    | OE = H, V <sub>CC</sub> = 3.3 V/3.6 V, V<br>1.27 V , HPD = H, Noise on ir<br>Stage 2 See Section 10.2 |                            |     |                    | 60                 | mW   |

| P <sub>(SD1)</sub>  | Device power in PowerDown                 | OE = L, V <sub>CC</sub> = 3.3 V/3.6 V, V <sub>E</sub><br>V                                            | <sub>DD</sub> = 1.1 V/1.27 |     | 8                  | 34                 | mW   |

| P <sub>(SD2)</sub>  | Device power in PowerDown in DP-<br>Mode  | OE = L, V <sub>CC</sub> = 3.3 V/3.6 V, V <sub>E</sub><br>V                                            | <sub>DD</sub> = 1.1 V/1.27 |     | 8                  | 34                 | mW   |

|                     |                                           | OE = H, V <sub>CC</sub> = 3.3 V/3.6 V, V                                                              | <sub>DD</sub> = 1.1 V/1.27 |     | 8                  | 20                 | mA   |

| CC1                 | V <sub>CC</sub> Supply current            | VIN_Dx: VID_PP = 1200 mV, 6<br>pattern<br>I2C_EN = L, SDA_CTL/PRE =<br>= H,                           |                            |     |                    |                    |      |

|                     |                                           | OE = H, V <sub>CC</sub> = 3.3 V/3.6 V, V <sub>1</sub>                                                 | <sub>DD</sub> = 1.1 V/1.27 |     | 45                 | 110                | mA   |

| CC2                 | V <sub>CC</sub> Supply current in DP-Mode | V<br>IN_Dx: VID_PP = 400 mV, 5.4<br>pattern, I2C_EN = H, V <sub>OD</sub> = 4<br>= 0 dB                |                            |     |                    |                    |      |

|                     |                                           | OE = H, V <sub>CC</sub> = 3.3 V/3.6 V, V <sub>1</sub>                                                 | <sub>DD</sub> = 1.1 V/1.27 |     | 160                | 220                | mA   |

| I <sub>DD1</sub>    | V <sub>DD</sub> Supply current            | IN_Dx: VID_PP = 1200 mV, 6<br>pattern<br>I2C_EN = L, SDA_CTL/PRE =<br>= H                             |                            |     |                    |                    |      |

|                     |                                           | OE = H, V <sub>CC</sub> = 3.3 V/3.6 V, V <sub>I</sub>                                                 | <sub>DD</sub> = 1.1 V/1.27 |     | 160                | 220                | mA   |

| I <sub>DD2</sub>    | V <sub>DD</sub> Supply current DP-Mode    | V<br>IN_Dx: VID_PP = 400 mV, 5.4<br>pattern, I2C_EN = H, V <sub>OD</sub> = 4<br>dB                    |                            |     |                    |                    |      |

|                     | Stage 1: Standby current See              | OE = H, V <sub>CC</sub> = 3.3 V/3.6 V,<br>V <sub>DD</sub> = 1.1 V/1.27 V , HPD =                      | 3.3 V Rail                 |     |                    | 7                  | mA   |

|                     | Section 10.2                              | H: No signal on IN_CLK                                                                                | 1.1 V Rail                 |     |                    | 7                  | mA   |

| (STBY1)             | Stage 2: Standby current See              | OE = H, V <sub>CC</sub> = 3.3 V/3.6<br>V, V <sub>DD</sub> = 1.1 V/1.27 V ,                            | 3.3 V Rail                 |     |                    | 7<br>27            | mA   |

|                     | Section 10.2                              | HPD = H: No valid signal on<br>IN_CLK                                                                 | 1.1 V Rail                 |     |                    | 21                 | mA   |

| I <sub>(SD11)</sub> | PowerDown current – HDMI Mode             | OE = L, V <sub>CC</sub> = 3.3 V/3.6 V,<br>V <sub>DD</sub> = 1.1 V/1.27 V , or OE =                    | 3.3 V Rail                 |     | 1                  | 7                  | mA   |

| (3011)              |                                           | H, HPD = L                                                                                            | 1.1 V Rail                 |     | 4                  | 7                  | mA   |

| (SD2)               | PowerDown current in DP-Mode              | $OE = L, V_{CC} = 3.3 V/3.6 V,$                                                                       | 3.3 V Rail                 |     | 1                  | 7                  | mA   |

| 、                   |                                           | V <sub>DD</sub> = 1.1 V/1.27 V                                                                        | 1.1 V Rail                 |     | 4                  | 7                  | mA   |

The maximum rating is simulated at 3.6 V V<sub>CC</sub> and 1.27 V V<sub>DD</sub> and at 85°C temperature unless otherwise noted. The typical rating is simulated at 3.3 V V<sub>CC</sub> and 1.1 V V<sub>DD</sub> and at 27°C temperature unless otherwise noted. (1)

(2)

### 6.6 Electrical Characteristics, Differential Input

over operating free-air temperature range (unless otherwise noted)

|                         | PARAMETER                                | TEST CONDITIONS | MIN  | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|-------------------------|------------------------------------------|-----------------|------|--------------------|--------------------|------|

| D <sub>R(RX_DATA)</sub> | TMDS data lanes data rate                |                 | 0.25 |                    | 6                  | Gbps |

| D <sub>R(RX_CLK)</sub>  | TMDS clock lanes clock rate              |                 | 25   |                    | 340                | Mhz  |

| t <sub>RX_DUTY</sub>    | Input clock duty circle                  |                 | 40%  | 50%                | 60%                |      |

| R <sub>(INT)</sub>      | Input differential termination impedance |                 | 80   | 100                | 120                | Ω    |

| V <sub>(TERM)</sub>     | Input Common Mode Voltage                | OE = H          |      | 0.7                |                    | V    |

(1) The maximum rating is simulated at 3.6 V V<sub>CC</sub> and 1.27 V V<sub>DD</sub> and at 85°C temperature unless otherwise noted.

(2) The typical rating is simulated at 3.3 V V<sub>CC</sub> and 1.1 V V<sub>DD</sub> and at 27°C temperature unless otherwise noted.

### 6.7 Electrical Characteristics, TMDS Differential Output

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                               | TEST CONDITIONS                                                  | MIN | <b>TYP</b> <sup>(2)</sup> <b>MAX</b> <sup>(1)</sup> | UNIT |

|---------------------|-------------------------------------------------------------------------|------------------------------------------------------------------|-----|-----------------------------------------------------|------|

| V <sub>OD(PP)</sub> | Output differential voltage before pre-<br>emphasis; See Section 8.3.11 | $V_{SADJ}$ = 6 k $\Omega$ ; SDA_CTL/PRE = H:<br>See Figure 7-4   | 600 | 1400                                                | mV   |

| V                   | Steady state output differential voltage<br>See Section 8.3.11          | $V_{SADJ}$ = 6 k $\Omega$ ; SDA_CTL/PRE = H,<br>See Figure 7-4   | 350 | 720                                                 | mV   |

| V <sub>OD(SS)</sub> |                                                                         | $V_{SADJ}$ = 5.5 k $\Omega$ ; SDA_CTL/PRE = L,<br>See Figure 7-3 | 350 | 1000                                                | mV   |

| I <sub>OS</sub>     | Short circuit current limit                                             | Main link output shorted to GND                                  |     | 50                                                  | mA   |

| R <sub>(TERM)</sub> | Source Termination resistance for HDMI 2.0                              |                                                                  | 75  | 150                                                 | Ω    |

### 6.8 Electrical Characteristics, DDC, I2C, HPD, and ARC

#### over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                           | TEST CONDITIONS                                                                           | MIN                   | <b>TYP</b> <sup>(2)</sup> <b>MAX</b> <sup>(1)</sup> | UNIT |  |  |  |  |

|----------------------|-----------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------|------|--|--|--|--|

| DDC and I2C          |                                                     |                                                                                           |                       |                                                     |      |  |  |  |  |

| V <sub>IL</sub>      | SCL/SDA_CTL, SCL/SDA_SRC low<br>level input voltage |                                                                                           |                       | 0.3 x V <sub>CC</sub>                               | V    |  |  |  |  |

| V <sub>IH</sub>      | SCL/SDA_CTL, input voltage                          |                                                                                           | 0.7 x V <sub>CC</sub> | V <sub>CC</sub> + 0.5                               | V    |  |  |  |  |

| V                    | SCL/SDA_CTL, SCL/SDA_SRC low                        | $I_{O}$ = 3 mA and $V_{CC}$ > 2 V                                                         |                       | 0.4                                                 | V    |  |  |  |  |

| V <sub>OL</sub>      | level output voltage                                | $I_{O}$ = 3 mA and $V_{CC}$ > 2 V                                                         |                       | 0.2 x V <sub>CC</sub>                               | V    |  |  |  |  |

| HPD                  |                                                     |                                                                                           |                       |                                                     |      |  |  |  |  |

| V <sub>IH</sub>      | High-level input voltage                            | HPD_SNK                                                                                   | 2.1                   |                                                     | V    |  |  |  |  |

| V <sub>IL</sub>      | Low-level input voltage                             | HPD_SNK                                                                                   |                       | 0.8                                                 | V    |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                           | <sub>IOH</sub> = –500 μA; HPD_SRC,                                                        | 2.4                   | 3.6                                                 | V    |  |  |  |  |

| V <sub>OL</sub>      | Low-level output voltage                            | I <sub>OL</sub> = 500 μA; HPD_SRC,                                                        | 0                     | 0.4                                                 | V    |  |  |  |  |

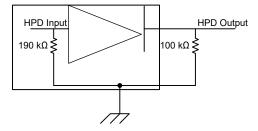

| I <sub>LKG</sub>     | Failsafe condition leakage current                  | V <sub>CC</sub> = 0 V; V <sub>DD</sub> = 0 V;<br>HPD_SNK = 5 V;                           |                       | 40                                                  | μA   |  |  |  |  |

| 1                    | Link lavel innut eurrent                            | Device powered; $V_{IH}$ = 5 V; $I_{H(HPD)}$<br>includes $R_{(pdHPD)}$ resistor current   |                       | 40                                                  | μA   |  |  |  |  |

| I <sub>H(HPD)</sub>  | High level input current                            | Device powered; $V_{IL}$ = 0.8 V; $I_{L(HPD)}$<br>includes $R_{(pdHPD)}$ resistor current |                       | 30                                                  | μA   |  |  |  |  |

| R <sub>(pdHPD)</sub> | HPD input termination to GND                        | V <sub>CC</sub> = 0 V                                                                     | 150                   | 190 220                                             | kΩ   |  |  |  |  |

(1) The maximum rating is simulated at 3.6 V  $V_{CC}$  and 1.27 V  $V_{DD}$  and at 85°C temperature unless otherwise noted.

(2) The typical rating is simulated at 3.3 V V<sub>CC</sub> and 1.1 V V<sub>DD</sub> and at 27°C temperature unless otherwise noted.

### 6.9 Electrical Characteristics, TMDS Differential Output in DP-Mode

|                               | PARAMETER                                        | TEST CONDITIONS                                                      | MIN | TYP | MAX <sup>(1)</sup> | UNIT |

|-------------------------------|--------------------------------------------------|----------------------------------------------------------------------|-----|-----|--------------------|------|

| V <sub>(TX_DIFFPP_LVL0)</sub> | Differential peak-to-peak output voltage level 0 | Based on default state of V0_P0_VOD register                         |     | 415 |                    | V    |

| V <sub>(TX_DIFFPP_LVL1)</sub> | Differential peak-to-peak output voltage level 1 | Based on default state of V1_P0_VOD register                         |     | 660 |                    | V    |

| V <sub>(TX_DIFFPP_LVL2)</sub> | Differential peak-to-peak output voltage level 2 | Based on default state of V2_P0_VOD register                         |     | 880 |                    | V    |

| $\Delta V_{OD(L0L1)}$         | Output peak-to-peak differential                 | $\Delta V_{ODn} = 20 \times \log(V_{ODL(n+1)})$                      | 1   |     | 6                  | dB   |

| $\Delta V_{OD(L1L2)}$         | voltage delta                                    | V <sub>ODL(n</sub> )) measured in compliance with latest PHY CTS 1.2 | 1   |     | 5                  | dB   |

| V <sub>(TX_PRE_RATIO_0)</sub> | Pre-emphasis level 0                             | RBR, HBR and HBR2                                                    |     | 0   |                    | dB   |

| V <sub>(TX_PRE_RATIO_1)</sub> | Pre-emphasis level 1                             | RBR, HBR and HBR2                                                    | 2   |     | 4.2                | dB   |

| V <sub>(TX_PRE_RATIO_2)</sub> | Pre-emphasis level 2                             | RBR, HBR and HBR2                                                    | 5   |     | 7.2                | dB   |

| $\Delta V_{PRE(L1L0)}$        | Pre-emphasis delta                               | Measured in compliance with                                          | 2   |     |                    | dB   |

| $\Delta V_{PRE(L2L1)}$        |                                                  | latest PHY CTS 1.2                                                   | 1.6 |     |                    | dB   |

over operating free-air temperature range (unless otherwise noted)

(1) Does not support Level 3 swing or pre-emphasis.

#### 6.10 Switching Characteristics, TMDS

|                       | PARAMETER                                                                                          | TEST CONDITIONS             | MIN | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|-----------------------|----------------------------------------------------------------------------------------------------|-----------------------------|-----|--------------------|--------------------|------|

| d <sub>R</sub>        | Data rate                                                                                          |                             | 250 |                    | 6000               | Mbps |

|                       |                                                                                                    | Reg0Ah[1:0] = 11 (default)  |     | 60                 |                    | ps   |

| +                     |                                                                                                    | Reg0Ah[1:0] = 10            |     | 80                 |                    | ps   |

| t <sub>T(DATA)</sub>  | Transition time (rise and fall time);<br>measured at 20% and 80%.<br>SDA CTL = L, OE = H, All Data | Reg0Ah[1:0] = 01            |     | 95                 |                    | ps   |

|                       |                                                                                                    | Reg0Ah[1:0] = 00            |     | 110                |                    | ps   |

|                       | Rates                                                                                              | TERM = H; Reg0Bh[7:6] = 11  |     | 122                |                    | ps   |

| t <sub>T(CLOCK)</sub> | Note: Data lane control by I2C only:<br>See Section 8.3.10                                         | Reg0Bh[7:6] = 10            |     | 150                |                    | ps   |

|                       |                                                                                                    | TERM = L; Reg0Bh[7:6] = 00  |     | 180                |                    | ps   |

|                       |                                                                                                    | TERM = NC; Reg0Bh[7:6] = 01 |     | 203                |                    | ps   |

The maximum rating is simulated at 3.6 V V<sub>CC</sub> and 1.27 V V<sub>DD</sub> and at 85°C temperature unless otherwise noted. The typical rating is simulated at 3.3 V V<sub>CC</sub> and 1.1 V V<sub>DD</sub> and at 27°C temperature unless otherwise noted. (1)

(2)

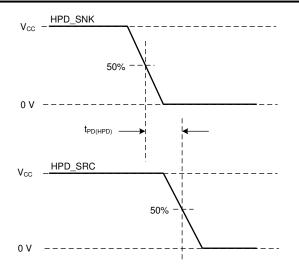

#### 6.11 Switching Characteristics, HPD

over operating free-air temperature range (unless otherwise noted)

|                      | PARAMETER                                                                     | TEST CONDITIONS                                 | MIN | TYP <sup>(2)</sup> | MAX <sup>(1)</sup> | UNIT |

|----------------------|-------------------------------------------------------------------------------|-------------------------------------------------|-----|--------------------|--------------------|------|

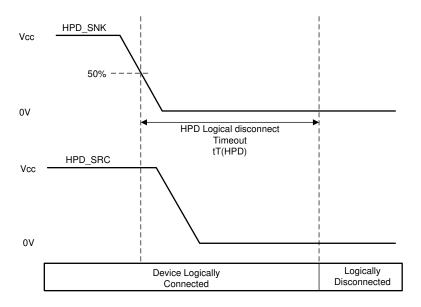

| t <sub>PD(HPD)</sub> | Propagation delay from HPD_SNK to<br>HPD_SRC; rising edge and falling<br>edge | see Figure 7-8; not valid during switching time |     | 40                 | 120                | ns   |

| t <sub>T(HPD)</sub>  | HPD logical disconnected timeout                                              | see Figure 7-9                                  | 2   |                    |                    | ms   |

The Maximum rating is simulated at 3.6 V V<sub>CC</sub> and 1.27 V V<sub>DD</sub> and at 85°C temperature unless otherwise noted The Typical rating is simulated at 3.3 V V<sub>CC</sub> and 1.1 V V<sub>DD</sub> and at 27°C temperature unless otherwise noted (1)

(2)

### 6.12 Switching Characteristics, DDC and I<sup>2</sup>C

over operating free-air temperature range (unless otherwise noted)

| PARAMETER            |                                                | TEST CONDITIONS                          | MIN | TYP | MAX | UNIT |

|----------------------|------------------------------------------------|------------------------------------------|-----|-----|-----|------|

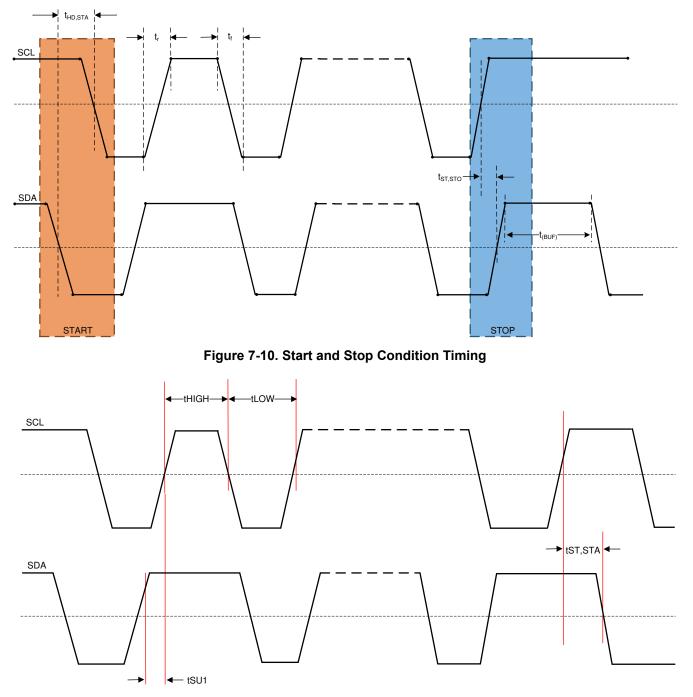

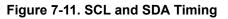

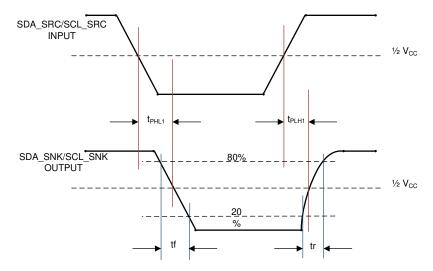

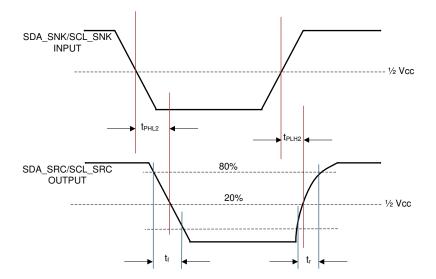

| t <sub>r</sub>       | Rise time of both SDA and SCL signals          | V <sub>CC</sub> = 3.3 V; See Figure 7-12 |     |     | 300 | ns   |

| t <sub>f</sub>       | Fall time of both SDA and SCL signals          | See Figure 7-12                          |     |     | 300 | ns   |

| t <sub>HIGH</sub>    | Pulse duration, SCL high                       | See Figure 7-11                          | 0.6 |     |     | μs   |

| t <sub>LOW</sub>     | Pulse duration , SCL low                       | See Figure 7-11                          | 1.3 |     |     | μs   |

| t <sub>SU1</sub>     | Setup time, SDA to SCL                         | See Figure 7-11                          | 100 |     |     | ns   |

| t <sub>ST, STA</sub> | Setup time, SCL to start condition             | See Figure 7-11                          | 0.6 |     |     | μs   |

| t <sub>HD,STA</sub>  | Hold time, start condition to SCL              | See Figure 7-10                          | 0.6 |     |     | μs   |

| t <sub>HD,DAT</sub>  | Data Hold Time                                 |                                          | 0   |     |     | ns   |

| t <sub>VD,DAT</sub>  | Data valid time                                |                                          | 0.9 |     |     | μs   |

| t <sub>VD,ACK</sub>  | Data valid acknowledge time                    |                                          | 0.9 |     |     | μs   |

| t <sub>ST,STO</sub>  | Setup time, SCL to stop condition              | See Figure 7-10                          | 0.6 |     |     | μs   |

| t <sub>(BUF)</sub>   | Bus free time between stop and start condition | See Figure 7-10                          | 1.3 |     |     | μs   |

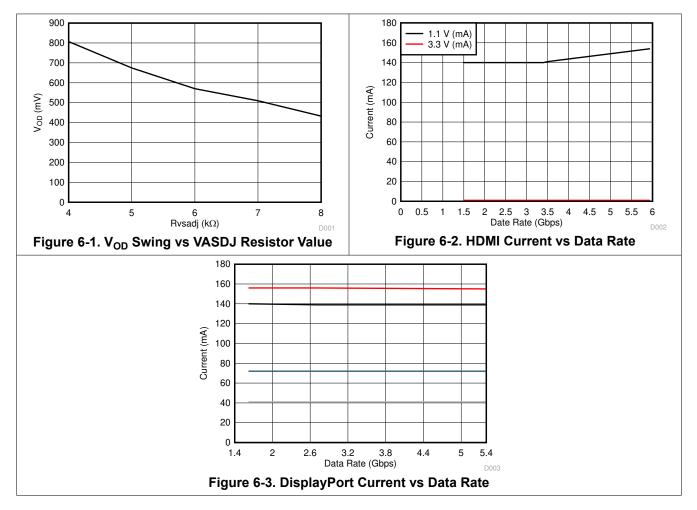

### 6.13 Typical Characteristics

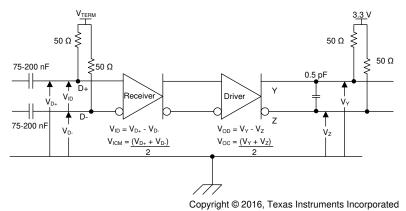

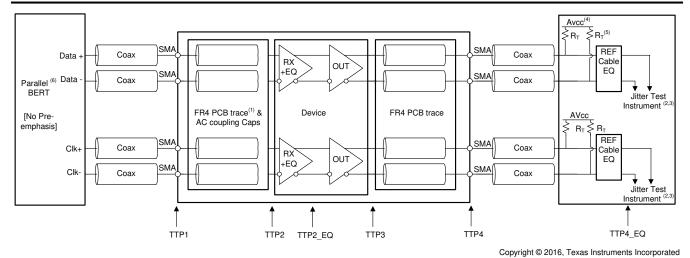

### 7 Parameter Measurement Information

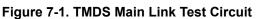

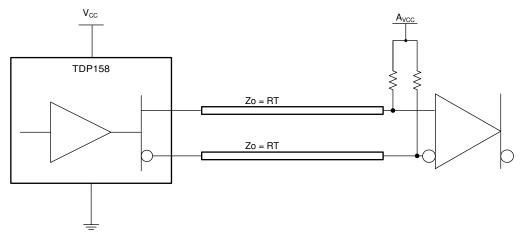

Figure 7-2. Input or Output Timing Measurements

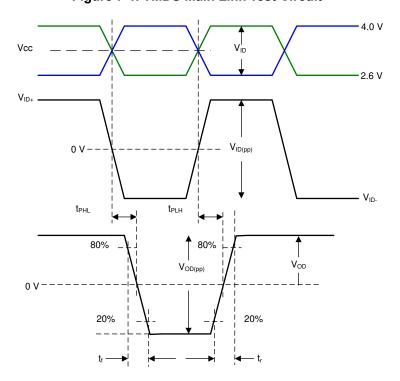

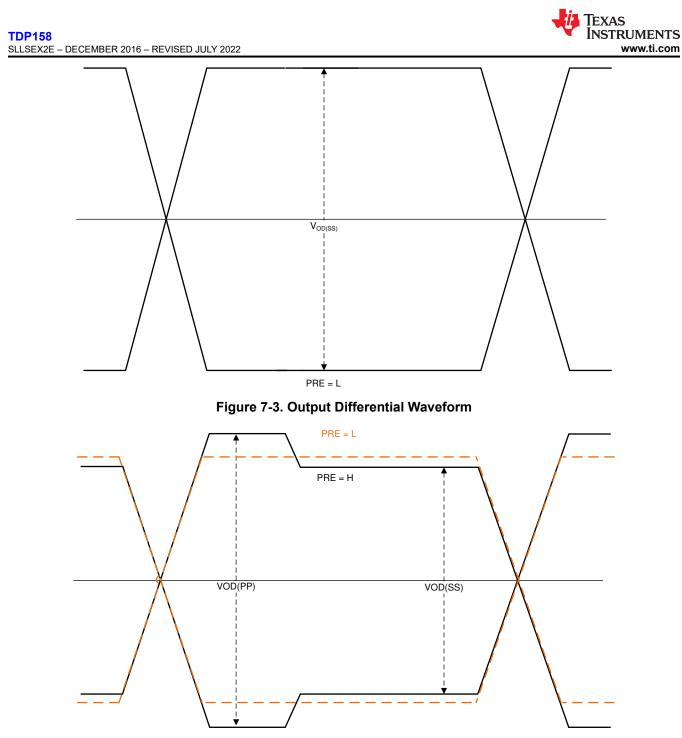

Figure 7-4. Output Differential Waveform with De-Emphasis

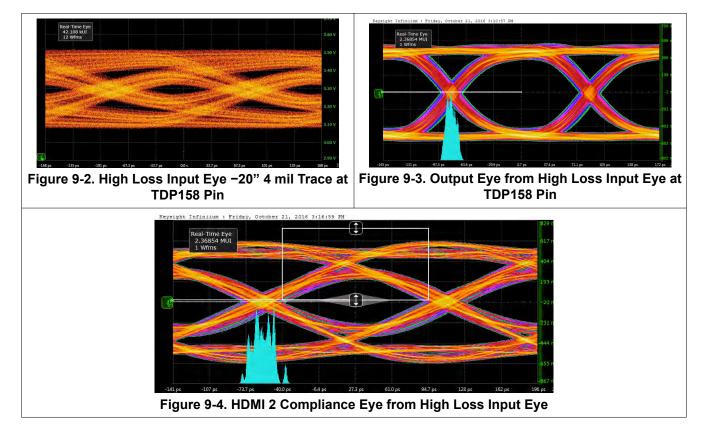

- A. The FR4 trace between TTP1 and TTP2 is designed to emulate 1-8" of FR4, AC coupling cap, connector and another 1-8" of FR4. Trace width 4 mils. 100  $\Omega$  differential impedance.

- B. All Jitter is measured at a BER of 10<sup>9</sup>

- C. Residual jitter reflects the total jitter measured at TTP4 minus the jitter measured at TTP

- D. AVCC = 3.3 V

- E. R<sub>T</sub> = 50 Ω

- F. The input signal from parallel Bert does not have any pre-emphasis. Refer to Recommended Operating Conditions.

#### Figure 7-5. HDMI Output Jitter Measurement

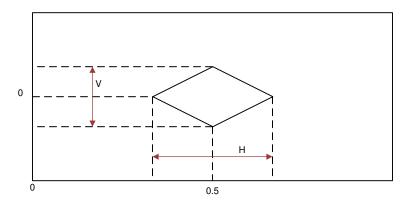

Figure 7-6. Output Eye Mask at TTP4\_EQ for HDMI 2.0

| TMDS Data Rate (Gbps) | H (Tbit)                                                    | V (mV)                                                    |

|-----------------------|-------------------------------------------------------------|-----------------------------------------------------------|

| 3.4 < DR < 3.712      | 0.6                                                         | 335                                                       |

| 3.712 < DR < 5.94     | -0.0332Rbit <sup>2</sup> + 0.2312 R <sub>bit</sub> + 0.1998 | –19.66Rbit <sup>2</sup> + 106.74R <sub>bit</sub> + 209.58 |

| 5.94 ≤ DR ≤ 6.0       | 0.4                                                         | 150                                                       |

Figure 7-7. HPD Test Circuit

Figure 7-8. HPD Timing Diagram No. 1

Figure 7-9. HPD Logic Disconnect Timeout

Figure 7-12. DDC Propagation Delay – Source to Sink

Figure 7-13. DDC Propagation Delay – Sink to Source

### 8 Detailed Description

#### 8.1 Overview

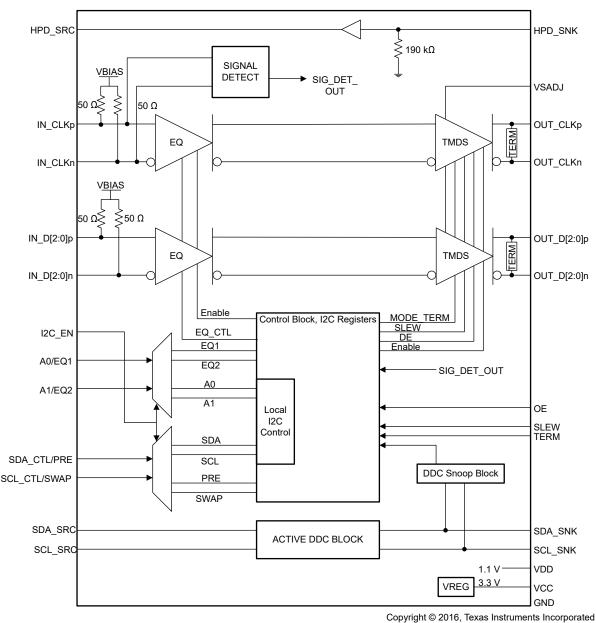

The TDP158 is an AC-coupled digital video interface (DVI) or high-definition multimedia interface (HDMI) signal input to Transition Minimized Differential Signal (TMDS) level shifting Redriver. The TDP158 supports four TMDS channels, Hot Plug Detect, and a Digital Display Control (DDC) interfaces. The TDP158 supports signaling rates up to 6 Gbps to allow for the highest resolutions of 4k2k60p 24 bits per pixel and up to WUXGA 16-bit color depth or 1080p with higher refresh rates. For passing compliance and reducing system level design issues, several features have been included such as TMDS output amplitude adjust using an external resistor on the VSADJ pin, source termination selection, pre-emphasis, and output slew rate control. Device operation and configuration can be programmed by pin strapping or I<sup>2</sup>C. Four TDP158 devices can be used on one I<sup>2</sup>C bus when I2C\_EN is high with device address set by A0/A1.

To reduce active power the TDP158 supports dual power supply rails of 1.1 V on VDD and 3.3 V on VCC. There are several methods of power management such as going into power down mode using three methods:

- 1. HPD is low

- 2. Writing a 1 to register 09h[3]

- 3. De-asserting OE

De-asserting OE clears the I<sup>2</sup>C registers, thus once re-asserted, the device must be reprogrammed if I<sup>2</sup>C was used for device setup. The TDP158 requires the source to write a 1 to the TMDS\_CLOCK\_RATIO\_STATUS register for the TDP158 to resume 75  $\Omega$  to 150  $\Omega$  source termination upon return to normal active operation from re-asserted, OE, or re-asserted HPD. If this bit is already set as a one during the source to sink read, then the TDP158 automatically sets this bit to 1. The SIG\_EN register enables the signal detect circuit that provides an automatic power-management feature during normal operation. When no valid signal is present on the clock input, the device enters Standby mode. DDC link supports the HDMI 2.0b SCDC communication, 100 Kbps data rate default and 400 Kbps adjustable by software.

TDP158 supports fixed EQ gain control to compensate for different lengths of input cables or board traces. The EQ gain can be software adjusted by I<sup>2</sup>C control or pin strapping EQ1 and EQ2 pins. Customers can use the TERM to change to one of three source termination impedances for better output performance when working in HDMI 1.4b or HDMI 2.0b. When the TMDS\_CLOCK\_RATIO\_STATUS bit is set to 1, the TDP158 automatically switches in 75  $\Omega$  to 150  $\Omega$  source termination. To assist in ease of implementation, the TDP158 supports lanes swapping, see Section 8.3.3. The device's available extended commercial temperature range is 0°C to 85°C.

#### 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Reset Implementation

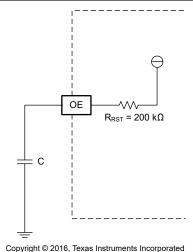

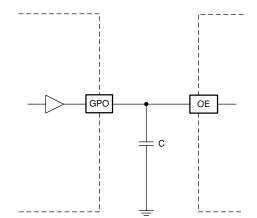

When OE is low, control signal inputs are ignored; the HDMI inputs and outputs are high impedance. It is critical to transition the OE from a low level to high after the  $V_{CC}$  supply has reached the minimum recommended operating voltage. This is achieved by a control signal to the OE input, or by an external capacitor connected between OE and GND. To ensure the TDP158 is properly reset, the OE pin must be de-asserted for at least 100 µs before being asserted. When OE is re-asserted the TDP158 must be reprogrammed if it was programmed by I<sup>2</sup>C and not pin strapping. When implementing the external capacitor, the size of the external capacitor depends on the power up ramp of the  $V_{CC}$  supply, where a slower ramp-up results in a larger value external capacitor. Refer to the latest reference schematic for TDP158; consider approximately 0.1 µF capacitor as a reasonable first estimate for the size of the external capacitor. Both OE implementations are shown in Figure 8-1 and Figure 8-2.

Copyright © 2016, Texas Instruments Incorporated

Figure 8-2. OE Input from Active Controller

#### 8.3.2 Operation Timing

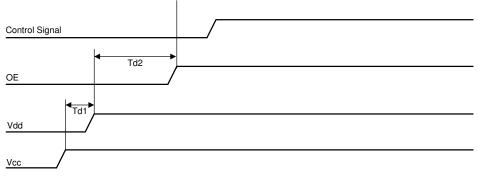

TDP158 starts to operate after the OE signal is properly set after power up timing is complete. See Figure 8-3 and Table 8-1. Keeping OE low until  $V_{DD}$  and  $V_{CC}$  becomes stable avoids any timing requirements as shown in Figure 8-3.

| PARAMETER DESCRIPTION                                         |                                                                                   | MIN | ТҮР | MAX | UNIT |  |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------|-----|-----|-----|------|--|

| t <sub>d1</sub> V <sub>CC</sub> stable before V <sub>DD</sub> |                                                                                   | 0   |     | 200 | μs   |  |

| t <sub>d1</sub>                                               | t <sub>d1</sub> V <sub>DD</sub> and V <sub>CC</sub> stable before OE de-assertion |     |     |     | μs   |  |

| V <sub>DD(ramp)</sub>                                         | V <sub>DD(ramp)</sub> V <sub>DD</sub> supply ramp up requirements                 |     |     | 100 | ms   |  |

| V <sub>CC(ramp)</sub>                                         | V <sub>CC</sub> supply ramp up requirements                                       | 0.2 |     | 100 | ms   |  |

#### Table 8-1. Power Up and Operation Timing Requirements

#### 8.3.3 Lane Control

The TDP158 has various lane control features. By default the high speed lanes are globally controlled. Pin strapping can globally control features like receiver equalization,  $V_{OD}$  swing and pre-emphasis. I<sup>2</sup>C programming performs the same global programming using default configurations. Through I2C a method to control receive equalization, transmitter swing ( $V_{OD}$ ) and pre-emphasis on each individual lane. Setting reg09h[5] = 1 puts the device into independent lane configuration mode.

Reg31h[7:3] controls the clock lane, reg32h[7:3] controls lane D0, reg33h[7:3] controls lane D1 and reg34h[7:3] controls lane D2 while Reg4E and Reg4F control the individual lane EQ control.

Note

If the swap function is enabled and individual lane control has been implemented, then it is recommended to reprogram the lanes to make sure they match the expected results. Registers are mapped to the pin name convention.

#### 8.3.4 Swap

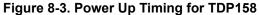

TDP158 incorporates a swap function which can swap the lanes, see Figure 8-4. The EQ, Pre-emphasis, termination, and slew setup will follow the new mapping. This function can be used with the SCL\_CTL/SWAP pin 13 when I2C\_EN pin 8 is low or can be implemented using control the register 0x09h bit 7 and is only valid for HDMI mode.

| Normal Operation               | SWAP = L or CSR 0x09h bit 7 is 1'b1 | Pin Numbers        |  |  |  |  |  |  |  |

|--------------------------------|-------------------------------------|--------------------|--|--|--|--|--|--|--|

| $IN_D2 \rightarrow OUT_D2$     | $IN\_CLK \rightarrow OUT\_CLK$      | [1, 2] → [30, 29]  |  |  |  |  |  |  |  |

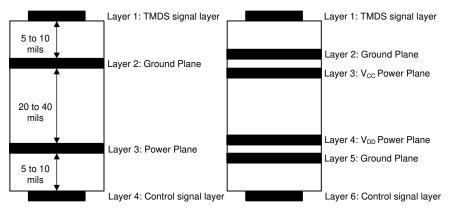

| $IN_D1 \rightarrow OUT_D1$     | $IN_D0 \rightarrow OUT_D0$          | [4, 5] → [27, 26]  |  |  |  |  |  |  |  |