# **Combination Power Factor Correction Controller and Flyback Controller for Flat Panel TVs**

This combination IC integrates the primary side control blocks – power factor correction (PFC) and flyback controllers with sequencing circuitry – necessary to implement a compact highly efficient Flat Panel TV Switched Mode Power Supply.

The PFC controller exhibits near-unity power factor while operating in Critical Conduction Mode (CrM) with an internal frequency clamp. The circuit incorporates all the features necessary for building a robust and compact PFC stage while minimizing the number of external components.

The fixed-frequency current-mode flyback controller features a proprietary Soft-Skip<sup>TM</sup> mode combined with frequency foldback enabling excellent efficiency during light load conditions while achieving very low standby power consumption. Soft-Skip dramatically reduces the risk of acoustic noise, therefore enabling the use of inexpensive transformers and capacitors in the clamping network. Frequency jittering and ramp compensation make this controller an excellent fit for converters where ruggedness and component cost are the key constraints.

# **Common General Features**

- Wide  $V_{CC}$  Range from 10 V to 30 V

- Very Low Startup Current Consumption (≤ 20 μA MAX)

- Inverter Enable Output

- Shutdown Pin to Disable IC

- Go To Standby Input

- This is a Pb–Free Device

# **PFC Controller Features**

- Critical Conduction Mode (CrM) with Constant On Time Control

- Internal Frequency Clamp

- Skip Mode Operation During Light Load Conditions

- Fast Line / Load Transient Compensation

- Accurate and Programmable Maximum On Time Control

- Negative Current Sensing

- Programmable Overvoltage/Undervoltage Protection

- 800 mA Source / 1200 mA Sink Gate Drive

# **ON Semiconductor®**

http://onsemi.com

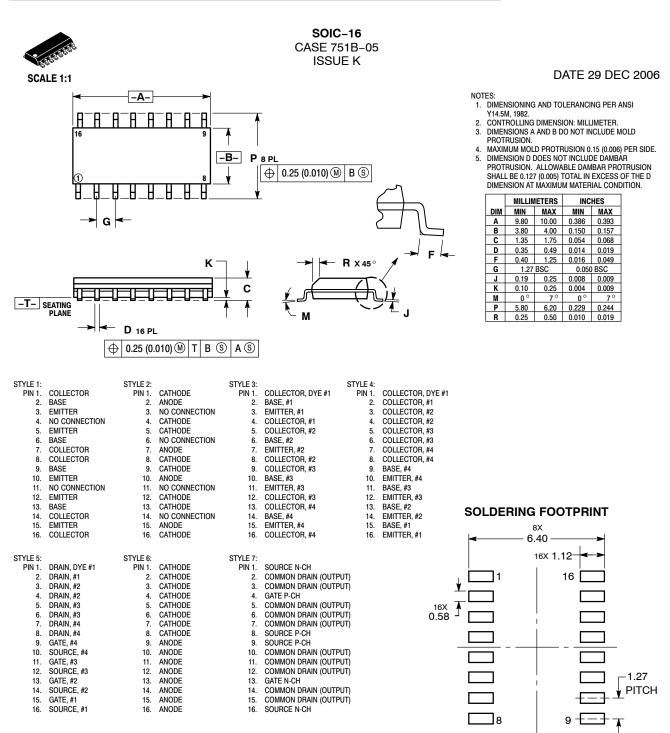

# **ORDERING INFORMATION**

= Pb-Free Package

| Device      | Package              | Shipping <sup>†</sup> |

|-------------|----------------------|-----------------------|

| NCP1927DR2G | SOIC-16<br>(Pb-Free) | 2500 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# **Flyback Controller Features**

- 65 kHz Fixed–Frequency Operation with Built–In Ramp Compensation

- Frequency Jittering for Softened EMI Signature

- Frequency Foldback then Soft-Skip for Improved Performance in Standby

- Timer-Based Overload Protection with Auto-Recovery

- Protection Against Winding Short-Circuit

- 4 ms Soft-Start Timer

- 800 mA Source / 1200 mA Sink Gate Drive

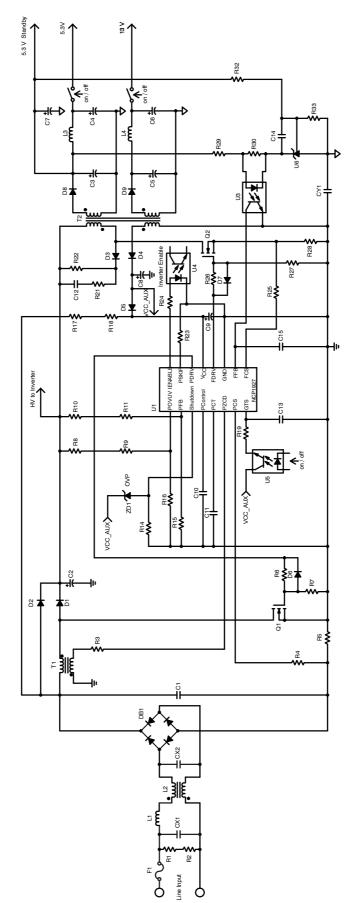

Figure 1. Typical Application Example

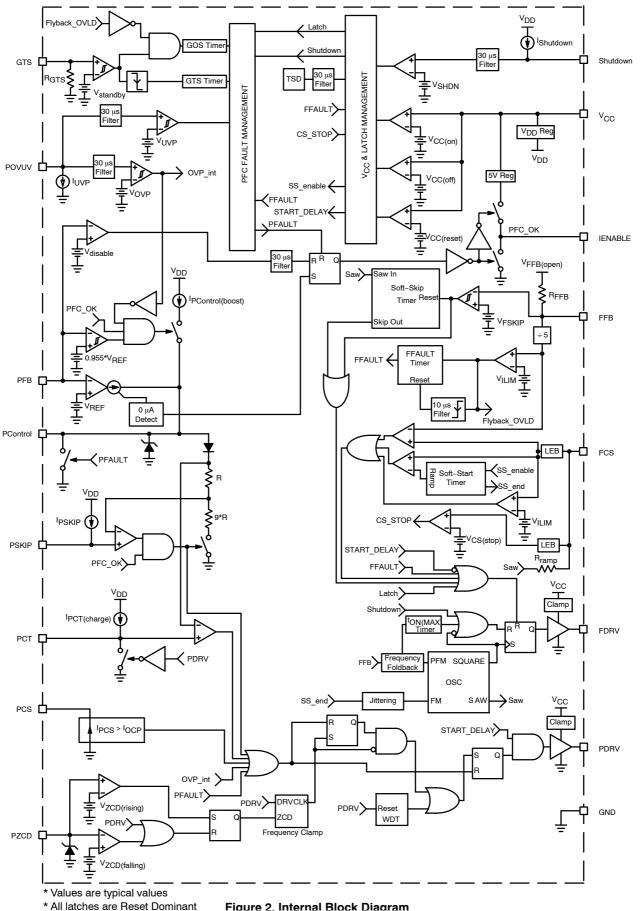

Figure 2. Internal Block Diagram

# PIN FUNCTION DESCRIPTION

| Pin No. | Pin Name        | Pin Description                                                                                                                                                                                                                                                                                                                                        |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

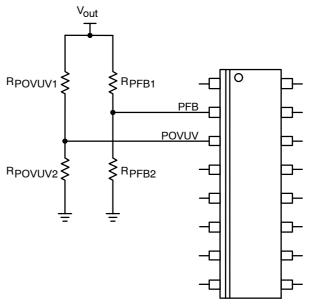

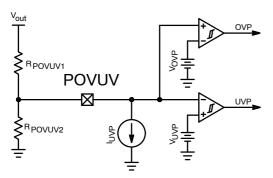

| 1       | POVUV           | The gate drive is disabled while $V_{POVUV}$ is below $V_{UVP}$ (300 mV typ) or above $V_{OVP}$ (2.5 V typ).                                                                                                                                                                                                                                           |

| 2       | PFB             | This pin receives a portion of the pre-converter output voltage. This information is used for the regulation and the "output low" detection that speeds up the loop response when the output voltage drops below 95.5% (typ) of the programmed level.                                                                                                  |

| 3       | Shutdown        | Pull this pin above 1.0 V (typ) to disable the part. Ground this pin when not in use.                                                                                                                                                                                                                                                                  |

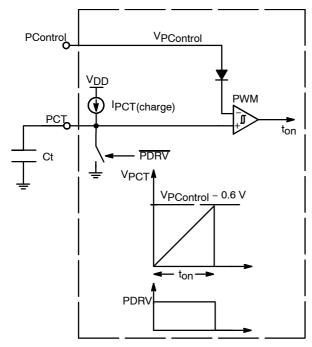

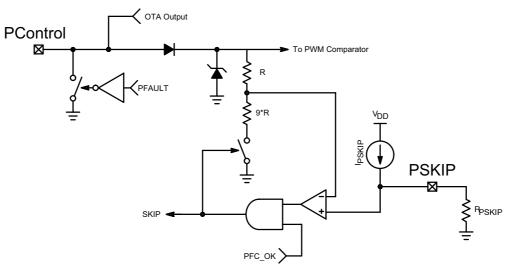

| 4       | PControl        | The error amplifier output is available on this pin. The capacitor connected between this pin and ground adjusts the regulation loop bandwidth that is typically set below 20 Hz to achieve a high power factor. This pin is internally grounded when the circuit is off so that when it starts operation, the power increases gradually (soft-start). |

| 5       | PCT             | The PCT pin sources a 210 $\mu$ A (typ) current to charge an external timing capacitor. The circuit controls the power switch on time by comparing the PCT voltage to an internal voltage derived from the regulation block.                                                                                                                           |

| 6       | PZCD            | The voltage of an auxiliary winding is applied to this pin to detect when the inductor is demagnetized for operation in critical conduction mode.                                                                                                                                                                                                      |

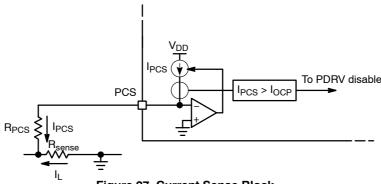

| 7       | PCS             | This pin monitors a negative voltage proportional to the coil current. This signal is sensed to limit the maximum coil current and protect the PFC stage during overload conditions.                                                                                                                                                                   |

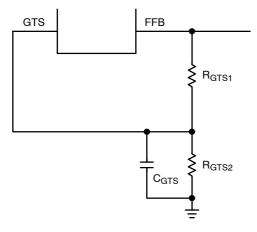

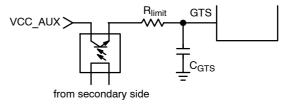

| 8       | GTS             | Pull this pin low to disable the PFC controller during standby mode. Standby mode can also be entered by monitoring the feedback voltage of the flyback stage with an external resistor divider.                                                                                                                                                       |

| 9       | FCS             | This pin senses the primary current for current-mode operation of the flyback stage. Ramp compensation can be added with an external resistor.                                                                                                                                                                                                         |

| 10      | FFB             | Connecting this pin to ground through an optocoupler allows regulation of the flyback stage.                                                                                                                                                                                                                                                           |

| 11      | GND             | This is the the controller ground.                                                                                                                                                                                                                                                                                                                     |

| 12      | FDRV            | This is the driver's output to an external MOSFET gate of the flyback power stage.                                                                                                                                                                                                                                                                     |

| 13      | V <sub>CC</sub> | This pin is connected to an external auxiliary voltage.                                                                                                                                                                                                                                                                                                |

| 14      | PDRV            | This is the driver's output to an external MOSFET gate of the PFC power stage.                                                                                                                                                                                                                                                                         |

| 15      | PSKIP           | To adjust the power level below which the PFC stage will enter skip mode, connect a resistor between this pin and ground. To disable skip mode, connect this pin directly to ground.                                                                                                                                                                   |

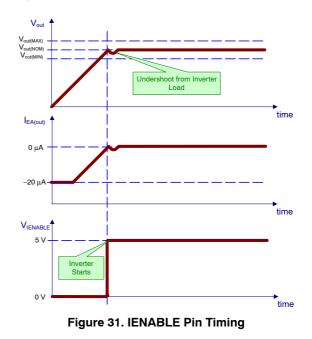

| 16      | IENABLE         | This pin voltage is high (5 V) when the output of the PFC stage is in steady state regulation and low at all other times. This signal serves to "inform" the backlight inverter that the PFC output is ready and that it can start operation. It can also be used as a stable 5 V reference.                                                           |

#### MAXIMUM RATINGS (Note 1)

| Rating                                                                                 | Symbol                                           | Value                     | Unit    |

|----------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------|---------|

| Supply Pin (pin 13) (Note 2)<br>Voltage Range<br>Current Range                         | V <sub>CC(MAX)</sub><br>I <sub>CC(MAX)</sub>     | -0.3 to 30<br>±30         | V<br>mA |

| PFC Drive Pin (pin 14) (Note 2)<br>Voltage Range<br>Current Range                      | Vpdrv(max)<br>Ipdrv(max)                         | -0.3 to 20<br>-800, +1200 | V<br>mA |

| Flyback Drive Pin (pin 12) (Note 2)<br>Voltage Range<br>Current Range                  | VFDRV(MAX)<br>IFDRV(MAX)                         | -0.3 to 20<br>-800, +1200 | V<br>mA |

| Inverter Enable Pin (pin 16) (Note 2)<br>Voltage Range<br>Current Range                | Vienable(max)<br>Iienable(max)                   | -0.3 to 6<br>±20          | V<br>mA |

| Control Pin (pin 4) (Note 2)<br>Voltage Range<br>Current Range                         | VPControl(MAX)<br>IPControl(MAX)                 | −0.3 to 6<br>±10          | V<br>mA |

| PFC Current Sense Pin (pin 7) (Note 2)<br>Voltage Range<br>Current Range               | VPCS(MAX)<br>IPCS(MAX)                           | −0.3 to 3<br>±10          | V<br>mA |

| ZCD Pin (pin 6) (Note 2)<br>Voltage Range<br>Current Range                             | V <sub>PZCD(MAX)</sub><br>I <sub>PZCD(MAX)</sub> | -0.9 to 12<br>±10         | V<br>mA |

| All Other Pins (Note 2)<br>Voltage Range<br>Current Range                              | V <sub>MAX</sub><br>I <sub>MAX</sub>             | −0.3 to 10<br>±10         | V<br>mA |

| Thermal Resistance<br>Junction-to-Air, 100 mm <sup>2</sup> Single Layer of 1 oz Copper | R <sub>θJA</sub>                                 | 140                       | °C/W    |

| Temperature Range<br>Storage Temperature<br>Operating Junction Temperature             | T <sub>JSTRG</sub> (MAX)<br>T <sub>J</sub> (MAX) | -60 to 150<br>-25 to 125  | °C      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

This device series contains ESD protection and exceeds the following tests: Charged Device Model 2000 V per JEDEC Standard JESD22-C101D Human Body Model 2000 V per JEDEC Standard JESD22-A114E Machine Model 200 V per JEDEC Standard JESD22-A115A

2. This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 12 V,  $V_{PFB}$  = 2.4 V,  $V_{POVUV}$  = 2.3 V,  $V_{PControl}$  = 4 V,  $V_{PZCD}$  = 0 V,  $V_{PCS}$  = 0 V,  $V_{GTS}$  = 1 V,  $V_{PSKIP}$  = 0 V,  $V_{FFB}$  = 2.4 V,  $V_{FCS}$  = 0 V,  $V_{Shutdown}$  = 0 V,  $V_{IENABLE}$  = open,  $C_{PCT}$  = 1 nF,  $C_{PDRV}$  = 1 nF,  $C_{FDRV}$  = 1 nF, for typical values  $T_J$  = 25°C, for min/max values,  $T_J$  is – 25°C to 125°C, unless otherwise noted)

| Characteristics                                                                                                               | Test Condition                                                                                                                                                           | Symbol                                                                   | Min                      | Тур                      | Max                      | Unit                 |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------|--------------------------|--------------------------|----------------------|

| SUPPLY CIRCUIT                                                                                                                | •                                                                                                                                                                        |                                                                          | -                        |                          |                          |                      |

| Supply Voltage<br>Startup Threshold<br>Minimum Operating Voltage<br>Internal latch reset level                                | $\begin{array}{l} V_{CC} \text{ increasing, } dV/dt = 1.25 \ mV/\mu s \\ V_{CC} \text{ decreasing, } dV/dt = 125 \ \mu V/\mu s \\ V_{CC} \text{ decreasing} \end{array}$ | V <sub>CC</sub> (on)<br>V <sub>CC</sub> (off)<br>V <sub>CC</sub> (reset) | 16<br>8<br>5.0           | 17<br>9<br>6.5           | 18<br>10<br>8.0          | V                    |

| Supply Current<br>PFC is switching at 70kHz<br>PFC is switching at 70kHz<br>Flyback Switching, PFC is in GTS<br>During Faults | $C_{FDRV}$ = open, $C_{PDRV}$ = open<br>$V_{FFB}$ = $V_{fold}$ – 0.2 V, $C_{FDRV}$ = open,<br>$V_{FCS}$ = 0.8 V                                                          | ICC1<br>ICC2<br>ICC3<br>ICC4                                             | 2.4<br>3.8<br>1.0<br>1.0 | 3.3<br>5.1<br>1.5<br>1.5 | 4.2<br>6.4<br>2.0<br>2.5 | mA<br>mA<br>mA<br>mA |

| Startup                                                                                                                       | $V_{CC} = V_{CC(on)} - 0.2 V$                                                                                                                                            | I <sub>CC5</sub>                                                         | -                        | _                        | 20                       | μA                   |

| FLYBACK FEEDBACK                                                                                                              |                                                                                                                                                                          |                                                                          |                          |                          |                          |                      |

| Equivalent Internal Pull-Up Resistor                                                                                          |                                                                                                                                                                          | R <sub>FFB</sub>                                                         | 14                       | 20                       | 31                       | kΩ                   |

| V <sub>FFB</sub> to Internal Current Setpoint<br>Division Ratio                                                               |                                                                                                                                                                          | K <sub>FFB</sub>                                                         | 4.8                      | 5.0                      | 5.2                      |                      |

| Overload Detection Filter                                                                                                     |                                                                                                                                                                          | t <sub>delay(FOVLD)</sub>                                                | -                        | 10                       | -                        | μs                   |

| Flyback Fault Timer                                                                                                           | V <sub>FFB</sub> = 4.5 V to FDRV turn-off                                                                                                                                | t <sub>FOVLD</sub>                                                       | 60                       | 80                       | 100                      | ms                   |

| FFB Pin Voltage                                                                                                               | V <sub>FFB</sub> = open                                                                                                                                                  | V <sub>FFB(open)</sub>                                                   | 4.5                      | 5.0                      | 5.5                      | V                    |

| FLYBACK CURRENT SENSE                                                                                                         |                                                                                                                                                                          |                                                                          |                          |                          | -                        |                      |

| Current Sense Voltage Threshold                                                                                               | V <sub>FFB</sub> = 4.5 V                                                                                                                                                 | V <sub>ILIM</sub>                                                        | 0.655                    | 0.700                    | 0.725                    | V                    |

| Leading Edge Blanking Duration                                                                                                |                                                                                                                                                                          | t <sub>LEB</sub>                                                         | 190                      | 250                      | 310                      | ns                   |

| Propagation Delay<br>Current Sense Voltage Threshold<br>Immediate Fault Protection                                            | Step V <sub>FCS</sub> 0 V to 2 V, to FDRV<br>falling edge                                                                                                                | t <sub>delay(ILIM)</sub><br>t <sub>CS(stop)</sub>                        |                          | 80<br>80                 | 110<br>110               | ns<br>ns             |

| Immediate Fault Protection Threshold                                                                                          | $V_{FFB}$ = 3 V, $V_{FCS}$ dV/dt = 500 $\mu$ V/ $\mu$ s                                                                                                                  | V <sub>CS(stop)</sub>                                                    | 0.95                     | 1.05                     | 1.15                     | V                    |

| Leading Edge Blanking Duration for<br>I <sub>CS(stop)</sub>                                                                   |                                                                                                                                                                          | t <sub>LEB(stop)</sub>                                                   | 90                       | 120                      | 150                      | ns                   |

| Input Bias Current                                                                                                            | V <sub>FCS</sub> = V <sub>ILIM</sub>                                                                                                                                     | I <sub>FCS(bias)</sub>                                                   | -1                       | -                        | +1                       | μA                   |

| Current Sourced by the FCS Pin                                                                                                | V <sub>FCS</sub> = 0 V, 80% Duty Ratio                                                                                                                                   | I <sub>ramp(MAX)</sub>                                                   | 100                      | 150                      | 200                      | μA                   |

| FLYBACK SOFT-START                                                                                                            |                                                                                                                                                                          |                                                                          |                          |                          |                          |                      |

| Soft-Start Period                                                                                                             | $1^{st}$ FDRV pulse to $V_{FCS} = V_{ILIM}$                                                                                                                              | <sup>t</sup> SSTART                                                      | 2.8                      | 4.0                      | 5.2                      | ms                   |

| OSCILLATOR                                                                                                                    |                                                                                                                                                                          |                                                                          |                          |                          |                          |                      |

| Base Oscillator Frequency                                                                                                     |                                                                                                                                                                          | fosc                                                                     | 60                       | 65                       | 70                       | kHz                  |

| Maximum Duty Ratio                                                                                                            |                                                                                                                                                                          | D <sub>MAX</sub>                                                         | 76                       | 80                       | 84                       | %                    |

| Frequency Modulation in Percentage of $f_{\mbox{OSC}}$                                                                        |                                                                                                                                                                          | f <sub>MOD</sub>                                                         | -                        | ±6                       | -                        | %                    |

| Frequency Modulation Frequency                                                                                                |                                                                                                                                                                          | f <sub>jitter</sub>                                                      | -                        | 125                      | -                        | Hz                   |

| Oscillator Frequency Voltage Stability                                                                                        | $V_{CC(MIN)} < V_{CC} < V_{CC(MAX)}$                                                                                                                                     | f <sub>OSC(VSTAB)</sub>                                                  | -1                       | -                        | +1                       | %                    |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 12 V$ ,  $V_{PFB} = 2.4 V$ ,  $V_{POVUV} = 2.3 V$ ,  $V_{PControl} = 4 V$ ,  $V_{PZCD} = 0 V$ ,  $V_{PCS} = 0 V$ ,  $V_{GTS} = 1 V$ ,  $V_{PSKIP} = 0 V$ ,  $V_{FFB} = 2.4 V$ ,  $V_{FCS} = 0 V$ ,  $V_{Shutdown} = 0 V$ ,  $V_{IENABLE} = open$ ,  $C_{PCT} = 1 nF$ ,  $C_{PDRV} = 1 nF$ ,  $C_{FDRV} = 1 nF$ , for typical values  $T_J = 25^{\circ}C$ , for min/max values,  $T_J$  is  $- 25^{\circ}C$  to  $125^{\circ}C$ , unless otherwise noted)

| Characteristics                               | Test Condition                                                                                                          | Symbol                                             | Min  | Тур        | Max  | Unit                 |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|------------|------|----------------------|

| FLYBACK GATE DRIVE                            |                                                                                                                         |                                                    |      |            |      |                      |

| FDRV Impedance<br>Sink<br>Source              | V <sub>FDRV</sub> = 10 V<br>V <sub>FDRV</sub> = 2 V                                                                     | R <sub>FDRV</sub> (snk)<br>R <sub>FDRV</sub> (src) |      | 12.5<br>14 |      | Ω<br>Ω               |

| FDRV Rise Time (10% to 90%)                   |                                                                                                                         | t <sub>FDRV(r)</sub>                               | 15   | 30         | 80   | ns                   |

| FDRV Fall Time (90% to 10%)                   |                                                                                                                         | t <sub>FDRV(f)</sub>                               | 12   | 25         | 70   | ns                   |

| FDRV Low Voltage                              | I <sub>FDRV</sub> = 0 mA                                                                                                | V <sub>FDRV(low)</sub>                             | -    | 0.06       | 0.5  | V                    |

| FDRV Voltage Drop                             | $\label{eq:V_CC} \begin{split} V_{CC} &= V_{CC(off)} + 0.2 \text{ V}, \\ R_{FDRV} &= 33 \text{ k}\Omega \end{split}$    | V <sub>FDRV(drop)</sub>                            | -    | -          | 1    | V                    |

| FDRV Clamp Voltage                            | $V_{CC}$ = 30 V, $I_{FDRV}$ = 0 mA                                                                                      | V <sub>FDRV(clamp)</sub>                           | 11   | 13.5       | 16   | V                    |

| FLYBACK SKIP MODE/FREQ FOLDB                  | ACK                                                                                                                     |                                                    |      |            |      |                      |

| Skip Threshold                                | V <sub>FFB</sub> Decreasing                                                                                             | V <sub>FSKIP</sub>                                 | 630  | 700        | 770  | mV                   |

| Skip Comparator Hysteresis                    |                                                                                                                         | V <sub>FSKIP(HYS)</sub>                            | 65   | 100        | 135  | mV                   |

| Soft-Skip Duration                            | $1^{st}$ Pulse to $V_{FCS} = V_{fold}/K_{FFB}$                                                                          | t <sub>SSKIP</sub>                                 | 50   | 100        | 140  | μs                   |

| Frequency Foldback Threshold                  | $V_{FFB}$ Decreasing, dV/dt = 500 $\mu$ V/ $\mu$ s                                                                      | V <sub>fold</sub>                                  | 1.26 | 1.40       | 1.54 | V                    |

| Minimum Switching Frequency                   | V <sub>FFB</sub> = V <sub>FSKIP</sub> + 150 mV                                                                          | f <sub>OSC(MIN)</sub>                              | 21   | 26         | 31   | kHz                  |

| Maximum On Time                               | Frequency Foldback or Skip Mode                                                                                         | t <sub>on(MAX)</sub>                               | 10.0 | 13.0       | 16.0 | μs                   |

| PFC CURRENT SENSE                             |                                                                                                                         |                                                    |      |            |      |                      |

| PCS Pin Voltage                               | $R_{PCS}$ = 2.5 kΩ, $I_{PCS}$ = 265 µA                                                                                  | V <sub>PCS</sub>                                   | -20  | 0          | 20   | mV                   |

| Overcurrent Protection Threshold              | $R_{PCS} = 2.5 \text{ k}\Omega$                                                                                         | I <sub>OCP</sub>                                   | 230  | 250        | 265  | μA                   |

| Propagation Delay                             | step I <sub>PCS</sub> 0 μA to 400 μA<br>I <sub>OCP</sub> to PDRV falling edge<br>R <sub>PCS</sub> = 1 kΩ                | t <sub>OCP</sub>                                   | -    | 100        | 210  | ns                   |

| PFC RAMP CONTROL                              | ·                                                                                                                       | •                                                  | 1    |            |      |                      |

| PCT Charge Current                            | V <sub>PCT</sub> = 1.5 V                                                                                                | I <sub>PCT(charge)</sub>                           | 189  | 210        | 231  | μA                   |

| C <sub>PCT</sub> Discharge Time               | $V_{PControl} = open, C_{PControl} = 10 \text{ nF}$ $V_{PCT} = V_{PCT(MAX)} - 100 \text{ mV to}$ $600 \text{ mV}$       | <sup>t</sup> CPCT(discharge)                       | _    | _          | 500  | ns                   |

| Maximum PCT Level Before PDRV<br>Switches Off | V <sub>PControl</sub> = open, C <sub>PControl</sub> = 10 nF                                                             | V <sub>PCT(MAX)</sub>                              | 4.7  | 5.0        | 5.3  | V                    |

| Propagation Delay of the PWM<br>Comparator    | step V <sub>PCT</sub> from 3.5 V to 5.0 V                                                                               | t <sub>PWM</sub>                                   | -    | 150        | 200  | ns                   |

| PFC Frequency Clamp                           |                                                                                                                         | f <sub>clamp</sub>                                 | 330  | 385        | 440  | kHz                  |

| PFC GATE DRIVE                                |                                                                                                                         |                                                    |      |            |      |                      |

| PDRV Impedance                                | )/ 10)/                                                                                                                 | B                                                  |      | 10 5       |      | 0                    |

| Sink<br>Source                                | V <sub>PDRV</sub> = 10 V<br>V <sub>PDRV</sub> = 2 V                                                                     | R <sub>PDRV(SNK)</sub><br>R <sub>PDRV(SRC)</sub>   | _    | 12.5<br>14 | -    | $\Omega$<br>$\Omega$ |

| PDRV Rise Time (10 % to 90 %)                 |                                                                                                                         | t <sub>PDRV(r)</sub>                               | 15   | 30         | 80   | ns                   |

| PDRV Fall Time (90 % to 10 %)                 |                                                                                                                         | t <sub>PDRV(f)</sub>                               | 12   | 25         | 70   | ns                   |

| PDRV Low Voltage                              | I <sub>PDRV</sub> = 0 mA                                                                                                | V <sub>PDRV(low)</sub>                             | -    | 0.06       | 0.5  | V                    |

| PDRV Voltage Drop                             | $\label{eq:V_CC} \begin{split} V_{CC} &= V_{CC(off)} + 0.2 \text{ V}, \\ R_{PDRV} &= 33  \mathrm{k} \Omega \end{split}$ | V <sub>PDRV(drop)</sub>                            | _    | -          | 1    | V                    |

| PDRV Clamp Voltage                            | V <sub>CC</sub> = 30 V, I <sub>PDRV</sub> = 0 mA                                                                        | V <sub>PDRV(clamp)</sub>                           | 11   | 13.5       | 16   | V                    |

| ELECTRICAL CHARACTERISTICS (V <sub>CC</sub> = 12 V, V <sub>PFB</sub> = 2.4 V, V <sub>POVUV</sub> = 2.3 V, V <sub>PControl</sub> = 4 V, V <sub>PZCD</sub> = 0 V, V <sub>PCS</sub> = 0 V, V <sub>GTS</sub> =                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 V, V <sub>PSKIP</sub> = 0 V, V <sub>FFB</sub> = 2.4 V, V <sub>FCS</sub> = 0 V, V <sub>Shutdown</sub> = 0 V, V <sub>IENABLE</sub> = open, C <sub>PCT</sub> = 1 nF, C <sub>PDRV</sub> = 1 nF, C <sub>FDRV</sub> = 1 nF, for typical |

| values $T_J = 25^{\circ}C$ , for min/max values, $T_J$ is – 25°C to 125°C, unless otherwise noted)                                                                                                                                  |

| Characteristics                                                                      | Test Condition                                                                                           | Symbol                                                | Min          | Тур          | Max          | Unit                     |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------|--------------|--------------|--------------------------|

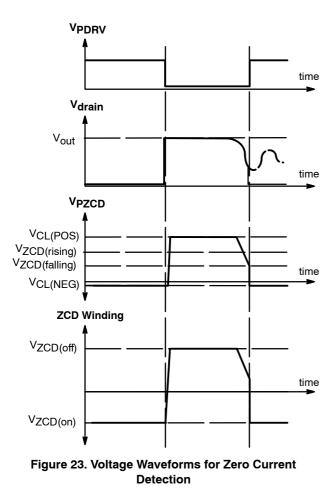

| PFC ZERO CURRENT DETECTION                                                           | -                                                                                                        | •                                                     | -            | -            | •            | -                        |

| Zero Current Detection Threshold<br>Rising<br>Falling                                |                                                                                                          | V <sub>ZCD(rising)</sub><br>V <sub>ZCD(falling)</sub> | 1.12<br>0.56 | 1.40<br>0.70 | 1.68<br>0.84 | V                        |

| Hysteresis on Voltage Threshold                                                      | V <sub>ZCD(rising)</sub> - V <sub>ZCD(falling)</sub>                                                     | V <sub>ZCD(HYS)</sub>                                 | 560          | 700          | 840          | mV                       |

| Propagation Delay                                                                    | Step V <sub>PZCD</sub> from 2 V to 0 V                                                                   | t <sub>ZCD</sub>                                      | -            | 100          | 170          | ns                       |

| Clamp Voltage<br>Upper Clamp<br>Negative Clamp                                       | I <sub>PZCD</sub> = 3 mA<br>I <sub>PZCD</sub> = −2 mA                                                    | V <sub>CL(POS)</sub><br>V <sub>CL(NEG)</sub>          | 8<br>-0.9    | 10<br>-0.7   | 12<br>0      | V                        |

| Minimum detectable ZCD pulse width                                                   |                                                                                                          | t <sub>SYNC</sub>                                     | -            | 70           | 100          | ns                       |

| Maximum Off Time                                                                     | PDRV off = 10% to PDRV on = 90%                                                                          | t <sub>start</sub>                                    | 75           | 180          | 300          | μs                       |

| Input Bias Current                                                                   | V <sub>PZCD</sub> = 5 V<br>V <sub>PZCD</sub> = -0.2 V                                                    | I <sub>PZCD(bias)</sub><br>I <sub>PZCD(bias)</sub>    | -2<br>-2     | -            | 2<br>2       | μ <b>Α</b><br>μ <b>Α</b> |

| PFC SKIP MODE                                                                        |                                                                                                          |                                                       |              |              |              |                          |

| Skip Pin Internal Current Source                                                     |                                                                                                          | I <sub>PSKIP</sub>                                    | 27           | 30           | 33           | μA                       |

| Hysteresis of the skip cycle detection level                                         | V <sub>PSKIP</sub> = 1 V                                                                                 | V <sub>PSKIP(HYS)</sub>                               | 10           | 12           | 16           | %                        |

| PFC REGULATION BLOCK                                                                 | -                                                                                                        |                                                       |              |              | -            |                          |

| Voltage Reference                                                                    |                                                                                                          | V <sub>REF</sub>                                      | 2.463        | 2.500        | 2.537        | V                        |

| Error Amplifier Current Capability<br>Maximum Source Current<br>Maximum Sink Current | V <sub>PFB</sub> = 2.4 V, V <sub>POVUV</sub> = 3 V<br>V <sub>PFB</sub> = 2.6 V, V <sub>POVUV</sub> = 3 V | I <sub>EA(SRC)</sub><br>I <sub>EA(SNK)</sub>          | 16<br>16     | 20<br>20     | 24<br>24     | μΑ<br>μΑ                 |

| Error Amplifier Transconductance                                                     | $V_{PFB}$ = $V_{REF}$ ± 100 mV,<br>$V_{POVUV}$ = 3 V                                                     | gm                                                    | 100          | 200          | 300          | μS                       |

| PFB Bias Current                                                                     | V <sub>PFB</sub> = 2.5 V                                                                                 | I <sub>PFB(bias)</sub>                                | -0.5         | -            | 0.5          | μA                       |

| Maximum EA Output Voltage                                                            | V <sub>PFB</sub> = 2 V<br>V <sub>PControl</sub> = open, C <sub>PControl</sub> = 10 nF                    | V <sub>PControl(MAX)</sub>                            | 5.05         | 5.6          | 6.1          | V                        |

| Minimum EA Output Voltage                                                            | V <sub>PFB</sub> = 3 V<br>V <sub>PControl</sub> = open, C <sub>PControl</sub> = 10 nF                    | V <sub>PControl</sub> (MIN)                           | 0.35         | 0.6          | 0.8          | V                        |

| EA Output Regulation Voltage Swing                                                   | V <sub>PControl(MAX)</sub> - V <sub>PControl(MIN)</sub>                                                  | $\Delta V_{PControl}$                                 | 4.7          | 5.0          | 5.3          | V                        |

| Ratio (V <sub>out</sub> Low Detect Threshold / V <sub>REF</sub> )                    |                                                                                                          | V <sub>OLOW</sub> /V <sub>REF</sub>                   | 95.0         | 95.5         | 96.0         | %                        |

| $V_{out}$ Low Detect / $V_{REF}$ Hysteresis                                          |                                                                                                          | V <sub>OLOW(HYS)</sub> /<br>V <sub>REF</sub>          | -            | -            | 1.0          | %                        |

| Source Current During V <sub>OUT</sub> Low<br>Detect                                 |                                                                                                          | I <sub>PControl(boost)</sub>                          | 190          | 240          | 290          | μA                       |

| GO TO STANDBY (GTS)                                                                  |                                                                                                          |                                                       |              |              |              |                          |

| Internal Pull-Down Resistor                                                          |                                                                                                          | R <sub>GTS</sub>                                      | 80           | 200          | 320          | kΩ                       |

| Standby Threshold                                                                    | V <sub>GTS</sub> Decreasing                                                                              | V <sub>standby</sub>                                  | 270          | 300          | 330          | mV                       |

| Standby Hysteresis                                                                   |                                                                                                          | V <sub>standby(HYS)</sub>                             | 85           | 100          | 125          | mV                       |

| Go To Standby Timer                                                                  | Step V <sub>GTS</sub> from 1 V to 0 V<br>Step V <sub>GTS</sub> from 0 V to 1 V                           | t <sub>GTS(off)</sub><br>t <sub>GTS(on)</sub>         | 37.5<br>30   | 50.0<br>50   | 62.5<br>70   | ms<br>μs                 |

| ELECTRICAL CHARACTERISTICS (V <sub>CC</sub> = 12 V, V <sub>PFB</sub> = 2.4 V, V <sub>POVUV</sub> = 2.3 V, V <sub>PControl</sub> = 4 V, V <sub>PZCD</sub> = 0 V, V <sub>PCS</sub> = 0 V, V <sub>GTS</sub> =                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 V, V <sub>PSKIP</sub> = 0 V, V <sub>FFB</sub> = 2.4 V, V <sub>FCS</sub> = 0 V, V <sub>Shutdown</sub> = 0 V, V <sub>IENABLE</sub> = open, C <sub>PCT</sub> = 1 nF, C <sub>PDRV</sub> = 1 nF, C <sub>FDRV</sub> = 1 nF, for typical |

| values $T_J = 25^{\circ}C$ , for min/max values, $T_J$ is – 25°C to 125°C, unless otherwise noted)                                                                                                                                  |

| Characteristics                                | Test Condition                                                                                             | Symbol                                            | Min             | Тур              | Max               | Unit         |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------|------------------|-------------------|--------------|

| PFC FAULT PROTECTION                           |                                                                                                            |                                                   | -               |                  |                   |              |

| Overvoltage Protection Threshold               |                                                                                                            | V <sub>OVP</sub>                                  | 2.450           | 2.500            | 2.550             | V            |

| Overvoltage Protection Hysteresis              |                                                                                                            | V <sub>OVP(HYS)</sub>                             | 20              | 40               | 60                | mV           |

| Overvoltage Protection Filter Delay            |                                                                                                            | t <sub>delay(OVP)</sub>                           | -               | 30               | -                 | μs           |

| Undervoltage Protection Threshold              |                                                                                                            | V <sub>UVP</sub>                                  | 285             | 300              | 315               | mV           |

| Undervoltage Protection Hysteresis             |                                                                                                            | V <sub>UVP(HYS)</sub>                             | 20              | 40               | 60                | mV           |

| Undervoltage Protection Filter Delay           |                                                                                                            | t <sub>delay(UVP)</sub>                           | -               | 30               | -                 | μs           |

| UVP Pull Down Current Source                   |                                                                                                            | I <sub>UVP</sub>                                  | 0.7             | 1.0              | 1.3               | μA           |

| Ratio Between $V_{OVP}$ and $V_{REF}$ (Note 3) |                                                                                                            | V <sub>OVP</sub> /V <sub>REF</sub>                | 99.5            | 100.0            | 100.5             | %            |

| INVERTER ENABLE/REFERENCE                      |                                                                                                            |                                                   |                 |                  |                   |              |

| Disable Threshold                              |                                                                                                            | V <sub>disable</sub>                              | 1.809           | 1.865            | 1.921             | V            |

| Disable Filter Delay                           |                                                                                                            | t <sub>delay(disable)</sub>                       | -               | 30               | -                 | μs           |

| Voltage Reference                              | I <sub>IENABLE(SRC)</sub> = 8 mA<br>I <sub>IENABLE(SRC)</sub> = 1 mA<br>I <sub>IENABLE(SNK)</sub> = 250 μA | VIENABLE(high)<br>VIENABLE(high)<br>VIENABLE(low) | 4.5<br>4.7<br>- | 5.0<br>5.0<br>60 | 5.4<br>5.4<br>120 | V<br>V<br>mV |

| Reference Pin Decoupling Capacitor             |                                                                                                            | C <sub>REF</sub>                                  | 0               | -                | 1                 | μF           |

| THERMAL PROTECTION                             |                                                                                                            |                                                   |                 |                  |                   |              |

| Thermal Shutdown                               |                                                                                                            | T <sub>TSHDN</sub>                                | -               | 150              | -                 | °C           |

| Thermal Shutdown Delay                         |                                                                                                            | t <sub>delay(TSHDN)</sub>                         | -               | 30               | -                 | μs           |

| SHUTDOWN PIN                                   |                                                                                                            |                                                   |                 |                  |                   |              |

| Shutdown Threshold                             | V <sub>Shutdown</sub> Increasing                                                                           | V <sub>SHDN</sub>                                 | 0.90            | 1.00             | 1.10              | V            |

| Shutdown Filter Delay                          | V <sub>Shutdown</sub> Increasing                                                                           | t <sub>delay(SHDN)</sub>                          | -               | 30               | -                 | μs           |

| Pull Up Current Source                         |                                                                                                            | I <sub>Shutdown</sub>                             | 2.3             | 3.3              | 4.3               | μA           |

3. Guaranteed by design

#### DETAILED OPERATING DESCRIPTION

#### INTRODUCTION

The NCP1927 is a combination power factor correction (PFC) and flyback controller optimized for use in Flat Panel TVs. This device includes all the features needed to implement a highly efficient and compact power supply. It integrates a critical conduction mode (CrM) PFC controller and a fixed-frequency current mode flyback controller with proper sequencing for simplified system design.

This device includes frequency jittering, a shutdown input, an inverter enable output, a go to standby input, and a dedicated pin for under/overvoltage protection.

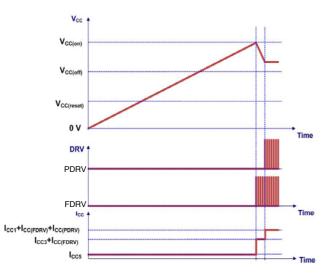

#### SUPPLY SEQUENCING

The flyback controller of the NCP1927 is enabled once  $V_{CC}$  reaches  $V_{CC(on)}$ , provided it is not in thermal shutdown and has not been latched off or shutdown. Once the flyback controller is enabled, a soft–start timer is activated, and it begins switching. The soft–start timer provides a ramp signal that increases over t<sub>SSTART</sub> (typically 4.0 ms). This ensures that the peak current gradually increases to minimize power component stress and limit output voltage overshoot. Frequency jittering is disabled while the soft–start timer is running.

Once the flyback controller detects regulation on the output (it is no longer in overload), the PFC controller can be enabled. As soon as the PFC controller is enabled, the error amplifier begins to source its maximum output current,  $I_{EA(MAX)}$ , (typically 20 µA) to linearly charge the PControl pin capacitor ( $C_{PControl}$ ). Soft–start is achieved as  $C_{PControl}$  charges. An internal grounding switch on the PControl pin is turned on each time the PFC controller is disabled, and turned off when it is enabled. This ensures that  $C_{PControl}$  is always fully discharged at the beginning of soft–start.

As the PFC stage approaches regulation on the output, the error amplifier output current,  $I_{EA}$ , gradually reduces to 0  $\mu$ A. Once the output is in regulation and  $I_{EA}$  reaches 0  $\mu$ A, the IENABLE pin is set to  $V_{IENABLE(high)}$  (typically 5 V).

#### **V<sub>CC</sub> MANAGEMENT**

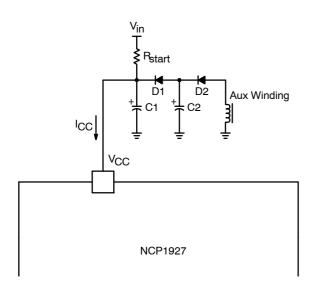

When power is initially applied to the application, the  $V_{CC}$  capacitor ( $C_{VCC}$ ) begins charging through a resistor connected to the high voltage line ( $V_{in}$ ). The resistor value must be chosen so that the charging current is greater than the IC bias current during startup. The maximum value for the startup resistor is calculated using Equation 1.

$$R_{start} = \frac{V_{in}}{I_{CC5}}$$

(eq. 1)

where  $V_{in}$  is the rectified dc input voltage and  $I_{CC5}$  is the IC bias current during startup (20  $\mu$ A maximum).

When  $V_{CC}$  reaches  $V_{CC(reset)}$  (typically 6.5 V), a Power On Reset occurs. This resets all logic states on the device. As  $V_{CC}$  continues to rise, the IC bias current remains at  $I_{CC5}$ until  $V_{CC}$  reaches  $V_{CC(on)}$  (typically 17 V). Once  $V_{CC}$ reaches  $V_{CC(on)}$ , the flyback controller is enabled and the IC bias current increases to  $I_{CC3}$  (1.5 mA typical). However, the total  $I_{CC}$  current is greater than this due to the gate charge load at the flyback drive output (FDRV). Once the flyback is in regulation, the PFC controller can be enabled. When the PFC is enabled, the  $I_{CC}$  current increases further due to the gate charge load at the PFC drive output (PDRV). The increase in  $I_{CC}$  per MOSFET is calculated using Equation 2.

$$I_{CC(x)} = f_{OSC} \cdot Q_{G(x)}$$

(eq. 2)

where,  $f_{OSC}$  is the switching frequency and  $Q_{G(X)}$  is the gate charge of the external MOSFET *X*.

$C_{VCC}$  must be sized such that a  $V_{CC}$  voltage greater than  $V_{CC(off)}$  (9 V typical) is maintained while the auxiliary supply voltage increases during startup. If  $C_{VCC}$  is too small,  $V_{CC}$  falls below  $V_{CC(off)}$  and the controller turns off before the auxiliary winding powers up the controller. The total  $I_{CC}$  current after the flyback controller is enabled ( $I_{CC3}$  plus  $I_{CC(FDRV)}$ ) must be considered to correctly size  $C_{VCC}$ . It is often useful to connect a small  $V_{CC}$  capacitor (C1) directly to the  $V_{CC}$  pin, while a larger capacitor (C2) is connected to the  $V_{CC}$  pin through a diode and charged by the aux winding. This allows minimum startup time while providing enough  $V_{CC}$  capacitance to operate during light load conditions. This implementation is shown in Figure 3 and the startup sequence is shown in Figure 4.

Figure 3. Operation with Dual  $V_{\mbox{CC}}$  Capacitors

Figure 4. Startup Sequence of the NCP1927

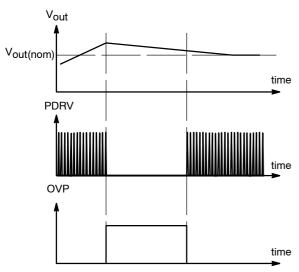

# FAULT MANAGEMENT

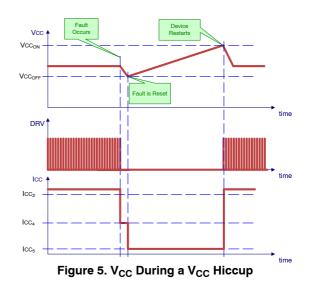

When the NCP1927 detects a non-latching fault (Shutdown Mode, TSD, and Flyback Overload), the drivers are disabled, and  $V_{CC}$  falls towards  $V_{CC(off)}$  due to the IC internal current consumption. Once  $V_{CC}$  falls below  $V_{CC(off)}$ , the fault is reset and the IC internal current consumption is reduced to the startup current,  $I_{CC5}$ .  $V_{CC}$  begins to rise as if power was initially applied and the device resumes normal operation once  $V_{CC}$  reaches  $V_{CC(on)}$ . This cycle between  $V_{CC(on)}$  and  $V_{CC(off)}$  is commonly referred to as a  $V_{CC}$  hiccup and is shown in Figure 5.

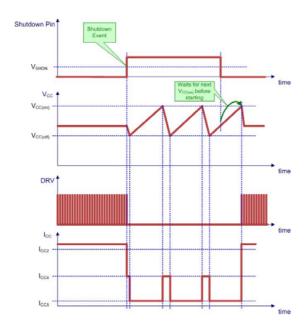

# SHUTDOWN PIN

The Shutdown pin allows for external disabling of the NCP1927. When V<sub>Shutdown</sub> is pulled above the shutdown threshold, V<sub>SHDN</sub> (typically 1.0 V), both the flyback and PFC drive outputs are immediately turned off, and a V<sub>CC</sub> hiccup occurs (see Figure 5). When V<sub>CC</sub> reaches V<sub>CC(on)</sub>, the cycle repeats unless the NCP1927 is taken out of shutdown. This is achieved when V<sub>Shutdown</sub> becomes less than V<sub>SHDN</sub>. The NCP1927 leaves shutdown mode and will start when V<sub>CC</sub> reaches V<sub>CC(on)</sub> according to the initial power–on sequence. The V<sub>CC</sub> behavior during shutdown mode is shown in Figure 6.

Figure 6. V<sub>CC</sub> Behavior During Shutdown Mode

#### THERMAL SHUTDOWN

When the junction temperature exceeds  $T_{TSHDN}$  (140°C minimum), a temperature sensing circuit disables the gate drives and a  $V_{CC}$  hiccup occurs (see Figure 5). When  $V_{CC}$  reaches  $V_{CC(on)}$ , the cycle repeats unless the junction temperature drops below  $T_{TSHDN}$ .

#### **CLAMPED DRIVERS**

The NCP1927 includes two powerful MOSFET drivers capable of sourcing 800 mA and sinking 1200 mA each. Since  $V_{CC}$  is rated at 30 V (maximum), each driver output is internally clamped to 16 V (maximum) to allow the use of 20 V MOSFETs.

# FLYBACK CONTROLLER

The NCP1927 flyback stage implements a standard current mode architecture where the switch-off event is dictated by the peak current setpoint.

# Oscillator with Maximum Duty Ratio and Frequency Jittering

The NCP1927 flyback controller includes an oscillator that sets the switching frequency with an accuracy of  $\pm 7.7\%$ . The maximum duty ratio of the FDRV pin is 80% (typical).

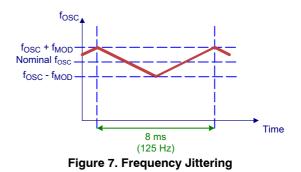

In order to improve the EMI signature, the switching frequency jitters at  $f_{MOD}$  (±6% typical) around its nominal value, with a triangle–wave shape and at a frequency of  $f_{jitter}$

(125 Hz typical). The frequency jittering is fully disabled during soft–start and frequency foldback. Figure 7 depicts the jittering operation.

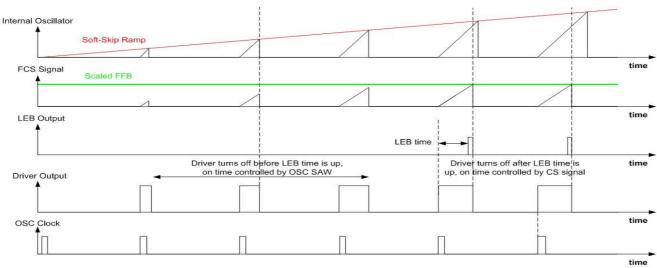

### **Current Sensing**

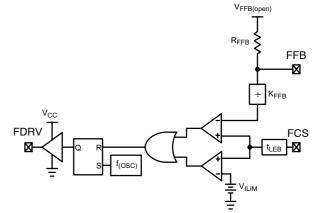

NCP1927 is a current-mode controller, which means that the feedback voltage sets the peak current flowing in the transformer and the MOSFET. This is done through the PWM comparator. The switch current is sensed across a resistor and the resulting voltage is applied to the FCS pin. It is then applied to one input of the PWM comparator through a 250 ns leading edge blanking (LEB) block. On the other input, the feedback voltage divided by K<sub>FFB</sub> (typically 5) sets the current limit threshold. When the current reaches this threshold, the output driver is turned off. A dedicated comparator monitors the current sense voltage, and if it reaches the maximum value, V<sub>ILIM</sub> (typically 0.7 V), the output driver is turned off immediately. This occurs even if the limit imposed by the feedback voltage is higher than VILIM. Figure 8 shows the schematic of the current sense circuit.

Figure 8. Current Sense Block Schematic

#### **Short–Winding Protection**

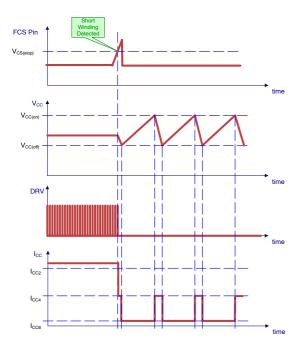

Under some conditions, like a transformer winding or output diode short-circuit, the primary current increases above  $V_{ILIM}$  before the LEB timer expires. To prevent dangerously high current from flowing, an additional comparator senses when  $V_{FCS}$  reaches  $V_{CS(stop)}$ . Once this comparator toggles, the controller immediately latches off.

The effect of latching off the IC is identical to shutdown mode, however, the  $V_{CC}$  cycle repeats indefinitely until the input power is removed and  $C_{VCC}$  is allowed to discharge below  $V_{CC(reset)}$ . When input power is reapplied, the NCP1927 operates according to the initial power-on sequence. The  $V_{CC}$  behavior during short winding protection is shown in Figure 9.

Figure 9. V<sub>CC</sub> Behavior During Short Winding Protection

#### Feedback

The ratio from the feedback voltage to the current limit threshold,  $K_{FFB}$  (typically 5), determines the peak current limit threshold. This means that the feedback voltage when the current limit threshold equals  $V_{ILIM}$  is 3.5 V (typical).

The FFB pin is connected to the internal  $V_{DD}$  rail through a resistor divider. To ease system design, the FFB pin is represented by a Thevenin equivalent circuit containing a voltage source and series resistor,  $V_{FFB(open)}$  (typically 5 V) and  $R_{FFB}$  (typically 20 k $\Omega$ ).

#### Soft-Start

The NCP1927 flyback controller features an internal soft-start circuit. Every time the controller starts (i.e. the controller was off and starts, or restarts due to a fault), a

soft-start is applied when  $V_{CC}$  reaches  $V_{CC(on)}$ . The current limit threshold is linearly increased from 0 until it reaches  $V_{ILIM}$  (in 4.0 ms), or until the feedback loop imposes a setpoint lower than the one imposed by the soft-start (the 2 comparator outputs are OR'ed together). Figure 10 shows a typical startup sequence.

Figure 10. Soft-Start Timing

#### **Ramp Compensation**

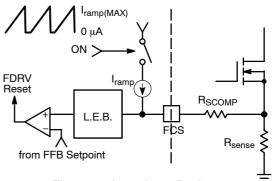

Ramp compensation is a known method for preventing subharmonic oscillations. These oscillations take place at half the switching frequency and occur only during continuous conduction mode (CCM) when the duty ratio is greater than 50%. To prevent these oscillations, one typically lowers the current loop gain by injecting between 50% and 75% of the inductor downslope. This is done by inserting a resistor ( $R_{SCOMP}$ ) between the FCS pin and the current sense resistor. Figure 11 shows an example of this. The ramp signal is disconnected from the FCS pin during the off time.

Figure 11. Inserting a Resistor

When calculating the proper value for  $R_{SCOMP}$ , it is necessary to express the internal ramp signal in terms of its slope (dI<sub>OSC</sub>/dt). This is done using Equation 3.

$$\frac{\mathrm{dI}_{\mathrm{OSC}}}{\mathrm{dt}} = \frac{\mathrm{I}_{\mathrm{ramp}(\mathrm{MAX})} \cdot f_{\mathrm{OSC}}}{\mathrm{D}_{\mathrm{MAX}}} \qquad (\mathrm{eq.}\ 3)$$

The inductor downslope  $(dV_{P(off)}/dt)$  projected across the current sense resistor  $(R_{sense})$  is then calculated using Equation 4.

$$\frac{dV_{P(off)}}{dt} = R_{sense} \cdot \frac{\left(V_{out} + V_{D}\right) \cdot \frac{N_{S}}{N_{P}}}{L_{P}} \qquad (eq. 4)$$

where  $V_D$  is the forward drop of the output rectifier,  $N_S/N_P$  is the turns ratio, and  $L_P$  is the primary inductance.

Using the results from Equations 3 and 4,  $R_{SCOMP}$  can be calculated using Equation 5.

$$\mathsf{R}_{\mathsf{SCOMP}} = \frac{\alpha \cdot \frac{d^{\mathsf{VP}}(\mathsf{off})}{dt}}{\frac{d^{\mathsf{I}} \mathsf{OSC}}{dt}} \tag{eq. 5}$$

where  $\alpha$  is the percentage of dV<sub>P(off)</sub>/dt to be injected.

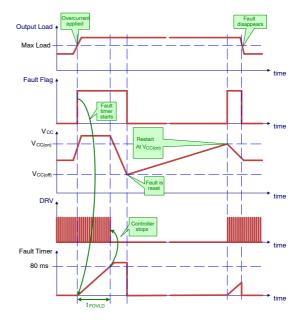

#### **Overload Protection with Fault Timer**

When an overload occurs on the output of the power supply, the feedback loop asks for more power than the controller can deliver, and the current limit threshold reaches  $V_{ILIM}$ . When this event occurs, a fault timer (t<sub>FOVLD</sub>) is enabled.

When the timer expires, FDRV pulses are stopped, the PFC is disabled, and a  $V_{CC}$  hiccup occurs. When  $V_{CC}$  reaches  $V_{CC(on)}$ , the controller starts according to the initial power–on sequence. If the overload is still present, the fault timer continues to run and the cycle repeats when it expires. The fault timer is reset if the current limit threshold goes back below  $V_{ILIM}$ . A short delay,  $t_{delay(FOVLD)}$ , is added to prevent the fault timer from resetting due to noise. This autorecovery operation is depicted in Figure 12.

Figure 12. Operation During Overload

#### **Frequency Foldback**

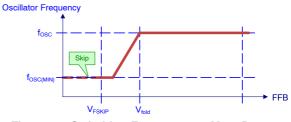

In order to improve the efficiency at light load conditions, the frequency of the internal oscillator is linearly reduced from its nominal value down to  $f_{OSC(MIN)}$  (typically 26 kHz). The frequency foldback starts when the voltage on the FFB pin goes below  $V_{fold}$ , and is completed before  $V_{FFB}$  reaches  $V_{FSKIP}$ . The current-mode control remains active while the oscillator frequency decreases. This is shown in Figure 13.

Figure 13. Switching Frequency as V<sub>FFB</sub> Decreases

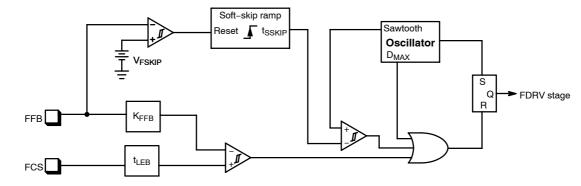

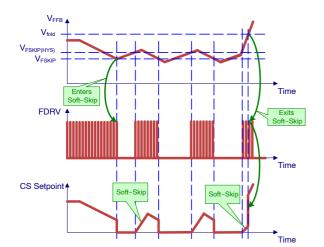

#### Skip Cycle Mode with Soft-Skip

When the feedback voltage reaches  $V_{FSKIP}$  while decreasing, skip mode is activated and the driver stops switching. While the driver is disabled,  $V_{FFB}$  begins to rise. As soon as  $V_{FFB}$  rises above  $V_{FSKIP} + V_{FSKIP(HYS)}$ , the driver starts to switch again, but the duty ratio is gradually increased from nearly 0% over a short Soft–Skip duration ( $t_{SSKIP}$ ). This is accomplished by comparing the current sense signal to an internal ramp generated by the Soft–Skip timer instead of the feedback voltage. Since the LEB of the FCS Pin prevents operation at nearly 0% duty ratio, the controller instead compares the soft–skip ramp to an internal sawtooth signal generated by the oscillator (not subjected to LEB). This causes the controller to operate briefly in voltage

mode instead of current mode. Once the CS signal reaches the feedback voltage, the controller resumes normal operation in current mode. The skip mode block diagram is shown in Figure 14. The ramp timing and overall timing diagrams are shown in Figures 15 and 16.

During the Soft-Skip duration if the feedback voltage

This transient load detection feature avoids large output drops if a load transient occurs while the controller is in skip

goes above V<sub>fold</sub>, the Soft-Skip ends instantaneously

allowing the controller to operate in current mode.

Figure 14. Skip Cycle with Soft-Skip Architecture

mode.

Figure 15. Skip Cycle with Soft-Skip Timing Diagram

Figure 16. Soft–Skip Timing Diagram

# PFC CONTROLLER

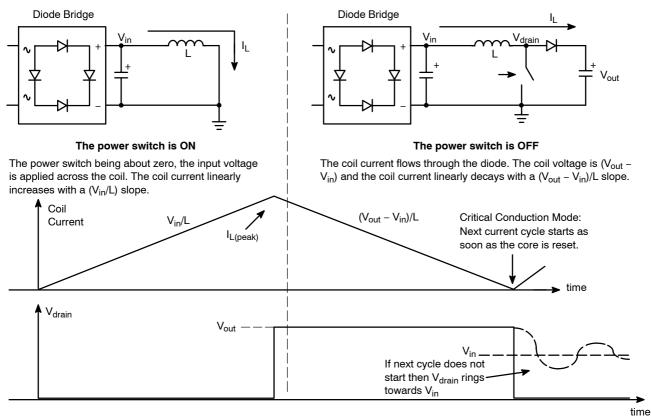

The PFC stage operates in critical conduction mode (CrM). CrM occurs at the boundary between discontinuous conduction mode (DCM) and continuous conduction mode (CCM). In CrM, the driver on time is initiated when the boost inductor current reaches zero. CrM operation is an

ideal choice for medium power PFC boost stages because it combines the lower peak currents of CCM operation with the zero current switching of DCM operation. The operation and waveforms in a PFC boost converter are illustrated in Figure 17.

Figure 17. Schematic and Waveforms of an Ideal CrM Boost Converter

When the switch is closed, the inductor current increases linearly to its peak value. When the switch opens, the inductor current linearly decreases to zero. At this point, the drain voltage of the switch ( $V_{drain}$ ) begins to drop. If the next switching cycle does not start, the voltage rings with a dampened frequency around Vin. A simple derivation of equations (such as those found in AND8123) leads to the result that good power factor correction in CrM operation is achieved when the on time is constant across a single ac cycle. Equation 6 shows the relationship between on time and system operating conditions.

$$t_{on} = \frac{2 \cdot P_{out} \cdot L}{\eta \cdot Vac^2}$$

(eq. 6)

where  $P_{out}$  is the output power, L is the boost inductor inductance and  $\eta$  is the system efficiency.

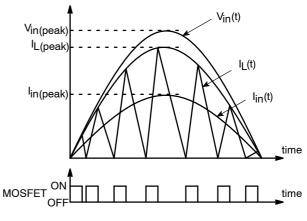

A plot of the MOSFET on/off time over an ac line cycle is illustrated in Figure 18. The MOSFET off time varies based on the instantaneous line voltage, but the on time is constant. This causes the peak inductor current  $(I_{L(peak)})$  to follow the ac line voltage. The NCP1927 implements

constant on time CrM control in a cost-effective and robust manner.

Figure 18. Inductor Waveform During CrM Operation

#### **Output Regulation**

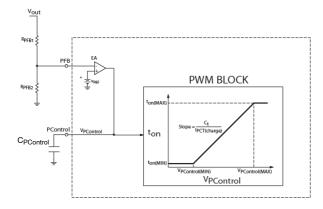

The NCP1927 error amplifier (EA) consists of an operational transconductance amplifier (OTA) with the inverting input connected to the PFB pin and the output connected to the PControl pin to regulate the output voltage. It features a typical transconductance (gm) of 200  $\mu$ S and a maximum output (I<sub>EA(SRC)</sub> and I<sub>EA(SNK)</sub>) of  $\pm 20 \,\mu$ A (typical). The non–inverting input is connected internally to a voltage reference (V<sub>REF</sub>) with a typical value of 2.5 V  $\pm 1.5\%$  over process and temperature. During normal operation, the voltage on the PControl pin varies between V<sub>PControl(MIN)</sub> (typically 0.6 V) and V<sub>PControl(MAX)</sub> (typically 5.6 V). A simplified diagram of the OTA circuit is shown in Figure 19.

Figure 19. Error Amplifier and On Time Regulation Circuits

A resistor divider from the boost output to the PFB pin provides a scaled–down representation of the output voltage (V<sub>out</sub>) to the EA. When V<sub>out</sub> is in regulation, V<sub>PFB</sub> equals V<sub>REF</sub>. If V<sub>out</sub> drops below regulation, the feedback voltage (V<sub>PFB</sub>) drops and the EA sources current until V<sub>PFB</sub> returns towards V<sub>REF</sub>. This increases the control voltage (V<sub>PControl</sub>) and the on time of the driver (t<sub>on</sub>), which in turn increases the power delivered to the load and brings V<sub>out</sub> back into regulation. Alternatively, if V<sub>out</sub> (and also V<sub>PFB</sub>) is too high, the EA sinks current and V<sub>PControl</sub> decreases, thus shortening t<sub>on</sub> until V<sub>out</sub> returns to regulation. The output voltage is calculated using Equation 7.

$$V_{out} = V_{REF} \cdot \frac{R_{PFB1} + R_{PFB2}}{R_{PFB2}}$$

(eq. 7)

where  $R_{PFB1}$  is the upper resistor of the resistor divider, and  $R_{PFB2}$  is the lower resistor.

The impedance of the feedback network determines its noise immunity and power dissipation. While a lower impedance provides better noise immunity, it also increases power dissipation. Once the divider current is chosen,  $R_{PFB1}$  is determined using Equation 8.

$$\mathsf{R}_{\mathsf{PFB1}} = \frac{\mathsf{V}_{\mathsf{out}}}{\mathsf{I}_{\mathsf{divider}}} \tag{eq. 8}$$

where I<sub>divider</sub> is the resistor divider current.

Using R<sub>PFB1</sub>, R<sub>PFB2</sub> is calculated with Equation 9.

$$R_{PFB2} = \frac{R_{PFB1} \cdot V_{REF}}{V_{out} - V_{REF}}$$

(eq. 9)

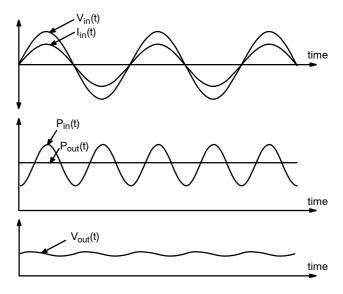

#### Compensation

A compensation network must be connected between the PControl pin and ground due to the nature of an active PFC circuit. The PFC stage generates a sinusoidal current from the ac line voltage and provides the load with a power that matches the average demand. When the input voltage is at its peak, the PFC stage delivers more power than the load requires, and the output capacitor charges. Conversely, when the input voltage is at a valley, the load requires more power than the PFC stage can deliver, and the output capacitor discharges. The situation is depicted in Figure 20.

#### Figure 20. Output Voltage Ripple for a Constant Output Power

This creates a ripple on the output with frequency equal to twice the line frequency ( $f_{line}$ ). Since the on time must remain constant during each ac line cycle to maintain good power factor correction, the EA must reject the output ripple. This is commonly achieved by setting the regulation bandwidth below 20 Hz. A type 1 compensation network is typically used for simplicity, as it only requires a single capacitor ( $C_{PControl}$ ) connected between the PControl pin and ground (see Figure 19). For a type 1 network,  $C_{PControl}$ is calculated using Equation 10.

$$C_{\text{PControl}} = \frac{\text{gm}}{2\pi \cdot f_{\text{c}}} \qquad (\text{eq. 10})$$

where gm is the transconductance of the EA (typically 200  $\mu$ S), and f<sub>c</sub> is the desired crossover frequency (typically less than 20 Hz).

#### **Transient Load Detection**

Due to the low bandwidth of the regulation loop, fast load transients may result in output voltage over and undershoots. Overshoots are limited by the overvoltage protection (see OVP section). To control the undershoots, an internal comparator monitors the ratio between V<sub>PFB</sub> and V<sub>REF</sub>. When it is lower than V<sub>OLOW</sub>/V<sub>REF</sub> (95.5% typical), I<sub>PControl(boost)</sub> (240  $\mu$ A typical) is connected to the PControl pin to speed up the charging of C<sub>PControl</sub>. This has the effect of increasing the EA gain by a factor of approximately 13.

The transient load detection circuit is disabled during the startup sequence of the PFC stage to prevent it from interfering with the operation of the soft–start circuit.

#### **On Time Control**

Since the NCP1927 is designed to control a CrM boost converter, the switching pattern consists of constant on times and variable off times. The on time is set via an external capacitor (C<sub>t</sub>) connected to the PCT pin. At the beginning of each switching cycle, C<sub>t</sub> is charged linearly by  $I_{PCT(charge)}$  (210 µA typical). An internal comparator monitors the voltage on the PCT pin (V<sub>PCT</sub>) and compares it to an internal regulation limit set by V<sub>PControl</sub>. The internal limit is determined by shifting V<sub>PControl</sub> down by a voltage equal to one diode drop (0.6 V typical) to account for the offset of the control voltage range. Once this level is exceeded, the drive is turned off. C<sub>t</sub> is then discharged within t<sub>CPCT(discharge</sub>) (maximum 500 ns) and held low until the beginning of the next switching cycle. This sequence is shown in Figure 21.

Figure 21. On Time Generation

Since  $V_{PControl}$  varies with the RMS line voltage and output load, this naturally satisfies Equation 6. If the values of compensation components are sufficient to filter out the bulk capacitor voltage ripple, the on time remains constant over the entire ac line cycle.

The maximum on time of the controller occurs when  $V_{PControl}$  is at its maximum value. Therefore,  $C_t$  must be sized to ensure that the required on time can be achieved at maximum output power and minimum input voltage. The maximum on time is calculated using Equation 11.

$$t_{\text{on(MAX)}} = \frac{C_{\text{t}} \cdot V_{\text{PCT(MAX)}}}{I_{\text{PCT(charge)}}} \tag{eq. 11}$$

where  $V_{PCT(MAX)} = 5 V$  (typical) and  $I_{PCT(charge)} = 210 \mu A$  (typical).

Combining Equation 11 with Equation 6, results in Equation 12.

$$C_{t} = \frac{2 \cdot P_{out} \cdot L \cdot I_{PCT(charge)}}{\eta \cdot Vac_{LL}^{2} \cdot V_{PCT(MAX)}}$$

(eq. 12)

Where, Vac<sub>LL</sub> is the minimum ac rms input voltage.

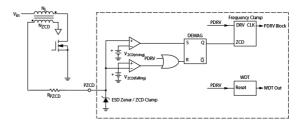

#### **Off Time Control**

The off time varies with the instantaneous line voltage and is adjusted every cycle so that the inductor is demagnetized before the next switching cycle begins. The inductor is demagnetized once its current reaches zero. When this happens, the drain voltage begins to drop. This is detected by sensing the voltage across an inductor auxiliary winding. This winding, commonly known as a zero crossing detection (ZCD) winding, provides the NCP1927 with a scaled version of the inductor voltage. Figure 22 shows a typical ZCD winding arrangement.

Figure 22. ZCD Winding Implementation