# PRODUCT/PROCESS CHANGE NOTIFICATION

PCN IPG/14/8545 Dated 24 Jun 2014

Assembly and Testing transfer from the ST plant of Longgang to ST Shenzhen for the products housed in TO-247 and DO-247 packages

#### Table 1. Change Implementation Schedule

| Forecasted implementation date for<br>change                                                    | 17-Jun-2014 |

|-------------------------------------------------------------------------------------------------|-------------|

| Forecasted availability date of samples for customer                                            | 17-Jun-2014 |

| Forecasted date for <b>STMicroelectronics</b><br>change Qualification Plan results availability | 17-Jun-2014 |

| Estimated date of changed product first shipment                                                | 22-Dec-2014 |

#### Table 2. Change Identification

| Product Identification<br>(Product Family/Commercial Product) | see attached list                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type of change                                                | Package assembly location change, Package assembly process change, Testing location change                                                                                                                                                                                                                                                                                                                                                                              |

| Reason for change                                             | To improve service to ST Automotive Customers and standardize manufacturing                                                                                                                                                                                                                                                                                                                                                                                             |

| Description of the change                                     | Continuing in the already announced plan of consolidating the<br>assembly and testing activities for the products housed in TO-247<br>and DO247 packages, ST is glad to announce the transfer of the<br>production lines from the ST plant of Longgang to the ST plant of<br>Shenzhen. The change will also benefit of the standardization for<br>those packages of the electroplating pro-cess already massively used<br>for all the others automotive power packages. |

| Change Product Identification                                 | "GK" marked on the package                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Manufacturing Location(s)                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### **Table 3. List of Attachments**

| Customer Part numbers list |  |

|----------------------------|--|

| Qualification Plan results |  |

| Customer Acknowledgement of Receipt                       | PCN IPG/14/8545   |

|-----------------------------------------------------------|-------------------|

| Please sign and return to STMicroelectronics Sales Office | Dated 24 Jun 2014 |

| Qualification Plan Denied                                 | Name:             |

| Qualification Plan Approved                               | Title:            |

|                                                           | Company:          |

| Change Denied                                             | Date:             |

| Change Approved                                           | Signature:        |

| Remark                                                    |                   |

|                                                           |                   |

|                                                           |                   |

|                                                           |                   |

|                                                           |                   |

|                                                           |                   |

|                                                           |                   |

|                                                           |                   |

| · · · · · · · · · · · · · · · · · · ·                     |                   |

|                                                           |                   |

| Name                | Function          |

|---------------------|-------------------|

| Giuffrida, Antonino | Marketing Manager |

| Martelli, Nunzio    | Product Manager   |

| Vitali, Gian Luigi  | Q.A. Manager      |

## **DOCUMENT APPROVAL**

# **IPG Group**

Assembly and Testing transfer from the ST plant of Longgang to ST Shenzhen and introduction of the leads electroplating finishing for the products housed in TO-247 and DO-247 packages.

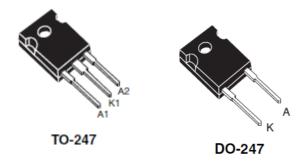

Packages typology

#### WHAT:

Continuing in the already announced plan of consolidating the assembly and testing activities for the products housed in TO-247 and DO247 packages, ST is glad to announce the transfer of the production lines from the ST plant of Longgang to the ST plant of Shenzhen. The change will also benefit of the standardization for those packages of the electroplating process already massively used for all the others automotive power packages.

For the complete list of the part numbers affected by these changes, please refer to the attached Products List.

**Samples**, of the test vehicles products manufactured in the ST plant of Shenzhen are available right now upon request for immediate customer qualification, while the full availability of products will be granted from wk xx 2014 onwards. Any other sample request will be granted upon request.

#### WHY:

To improve service to ST Automotive Customers and standardize manufacturing processes for the power packages typology.

#### HOW:

By transferring the existing equipment from the Longgang ST plant, to the ST Shenzhen assembly and testing premises.

The changed here reported will not affect the electrical, dimensional and thermal parameters, keeping unchanged all information reported on the relevant product's datasheets. There are as well neither modification in the packing modes nor in the standard delivery quantities.

#### **Qualification program and results:**

The qualification program consists in a full set of comparative electrical characterization and reliability tests. Please refer to Appendix 1 for all the details.

#### WHEN:

Production start and first shipments will occur as per the scheduling indicated in the tables below.

| Affected Product Types | Samples | 1 <sup>st</sup> Shipment |

|------------------------|---------|--------------------------|

| Power MOSFET           | Now     | Wk 52-14                 |

| Power Bipolar          | Now     | Wk 52-14                 |

| IGBT                   | Now     | Wk 52-14                 |

| Rectifier              | Now     | Wk 52-14                 |

# Marking and traceability:

Unless otherwise stated by customer specific requirement, the traceability of the parts produced in ST Shenzhen will be ensured by the Q.A. number and plant code identification "GK" marked on the package, as illustrated in the below picture:

Package marking example

# **Reliability Report**

# Qualification of assembly and testing transfer from Longgang ST plant to Shenzhen ST plant for rectifier products in TO247&DO247 package.

| Gen                 | eral Information | L                      | ocations                                |

|---------------------|------------------|------------------------|-----------------------------------------|

| Product Description | Rectifier        | Wafer fab              | ST TOURS (FRANCE)<br>ST AMK (SINGAPORE) |

| Product Group       | IPG              | Assembly plant         | ST SHENZHEN (CHINA)                     |

| Product division    | ASD&IPAD         | Reliability Lab        | ST Tours                                |

| Package             | TO-247<br>DO-247 |                        |                                         |

| Maturity level step | Qualified        | Reliability assessment | PASS                                    |

#### DOCUMENT INFORMATION

| Version | Date       | Pages | Prepared by | Approved by        | Comments                       |

|---------|------------|-------|-------------|--------------------|--------------------------------|

| 1.0     | 28/04/2014 | 8     | Aude DROMEL | Jean-Paul REBRASSE |                                |

| 2.0     | 22/05/2014 | 8     | Aude DROMEL | Jean-Paul REBRASSE | Automotive grade qualification |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

#### TABLE OF CONTENTS

| 1 | APPLI | CABLE AND REFERENCE DOCUMENTS | . 3 |

|---|-------|-------------------------------|-----|

| 2 | GLOS  | SARY                          | . 3 |

| 3 | RELIA | BILITY EVALUATION OVERVIEW    | . 4 |

|   | 3.1   | OBJECTIVES                    | . 4 |

|   | 3.2   | Conclusion                    | . 4 |

| 4 | DEVIC | CES CHARACTERISTICS           | . 5 |

|   | 4.1   | Devices descriptions          |     |

|   | 4.2   | Construction Note             | . 5 |

| 5 | TESTS | RESULTS SUMMARY               | . 6 |

|   | 5.1   | TEST VEHICLE                  | . 6 |

|   | 5.2   | TEST PLAN AND RESULTS SUMMARY | . 7 |

| 6 | ANNE  | XES                           |     |

| - | 6.1   | TESTS DESCRIPTION             |     |

## **1 APPLICABLE AND REFERENCE DOCUMENTS**

| Document reference | Short description                                                         |

|--------------------|---------------------------------------------------------------------------|

| AEC-Q101 rev C     | Stress test qualification for automotive grade discrete semiconductors    |

| JESD47             | Stress-Test-Driven Qualification of Integrated Circuits                   |

| JESD 94            | Application specific qualification using knowledge based test methodology |

| JESD 22            | Reliability test methods for packaged devices                             |

### 2 GLOSSARY

| DUT    | Device Under Test                |

|--------|----------------------------------|

| ΡΤν    | Product Test Vehicle             |

| РСВ    | Printed Circuit Board            |

| SS     | Sample Size                      |

| HTRB   | High Temperature Reverse Bias    |

| тс     | Temperature Cycling              |

| ТНВ    | Temperature Humidity Bias        |

| IOLT   | Intermittent Operating Life Test |

| PCT/AC | Pressure Cooker Test (Autoclave) |

| RSH    | Resistance to Solder Heat        |

| SD     | Solderability                    |

| DPA    | Destructive Physical Analysis    |

### **<u>3 RELIABILITY EVALUATION OVERVIEW</u>**

### 3.1 **Objectives**

The objective of this report is to qualify the assembly and testing transfer from the ST plant of Longgang to ST plant of Shenzhen for the rectifiers products in TO-247 and DO-247 packages.

The reliability test methodology used follows the JESD47-H: « Stress Test Driven Qualification Methodology ». Rectifier diodes perimeter is covered through 5 different test vehicles including turbo/bipolar diodes and Schottky barrier diodes. These test vehicles have been chosen to include the most critical parameters for reliability (die size, highest voltage, etc.)

The following reliability tests are:

- HTRB to evaluate the risk of contamination from the resin and the assembly process versus the die layout sensitivity.

- TC and IOLT to ensure the mechanical robustness of the products.

- THB/AC to check the robustness to corrosion and the good package hermeticity.

- RSH and Solderability

### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. Reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the robustness of the products and safe operation, which is consequently expected during their lifetime.

### **4 DEVICES CHARACTERISTICS**

### 4.1 **Devices descriptions**

All rectifiers (bipolar, turboswitch, power shottky in silicon and silicon carbide) assembled in TO-247 and DO-247 packages.

### 4.2 Construction Note

|                                                                                                                                                                                                      | STTHxxxxW & STTHxxxxWY                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Wafer/Die fab. information                                                                                                                                                                           |                                                                                                                                          |

| Wafer fab manufacturing location                                                                                                                                                                     | ST TOURS FRANCE                                                                                                                          |

| Wafer Testing (EWS) information                                                                                                                                                                      |                                                                                                                                          |

| Electrical testing manufacturing location                                                                                                                                                            | ST TOURS FRANCE                                                                                                                          |

| Assembly information                                                                                                                                                                                 |                                                                                                                                          |

| Assembly site                                                                                                                                                                                        | ST SHENZHEN -CHINA                                                                                                                       |

| Package description                                                                                                                                                                                  | TO-247 & DO-247                                                                                                                          |

| Molding compound                                                                                                                                                                                     | ECOPACK <sup>®</sup> 2 ("Halogen-free")                                                                                                  |

| Lead finishing material                                                                                                                                                                              | Tin 100%                                                                                                                                 |

| Final testing information                                                                                                                                                                            |                                                                                                                                          |

| Testing location                                                                                                                                                                                     | ST SHENZHEN CHINA                                                                                                                        |

|                                                                                                                                                                                                      |                                                                                                                                          |

|                                                                                                                                                                                                      |                                                                                                                                          |

|                                                                                                                                                                                                      | STPSxxxxW & STPSxxxxWY                                                                                                                   |

| Wafer/Die fab. information                                                                                                                                                                           | STPSxxxxW & STPSxxxxWY                                                                                                                   |

| Wafer/Die fab. information<br>Wafer fab manufacturing location                                                                                                                                       | STPSxxxxW & STPSxxxxWY ST AMK SINGAPORE or ST TOURS FRANCE                                                                               |

|                                                                                                                                                                                                      |                                                                                                                                          |

| Wafer fab manufacturing location                                                                                                                                                                     |                                                                                                                                          |

| Wafer fab manufacturing location<br>Wafer Testing (EWS) information                                                                                                                                  | ST AMK SINGAPORE or ST TOURS FRANCE                                                                                                      |

| Wafer fab manufacturing location<br>Wafer Testing (EWS) information<br>Electrical testing manufacturing location                                                                                     | ST AMK SINGAPORE or ST TOURS FRANCE                                                                                                      |

| Wafer fab manufacturing location<br>Wafer Testing (EWS) information<br>Electrical testing manufacturing location<br>Assembly information                                                             | ST AMK SINGAPORE or ST TOURS FRANCE<br>ST AMK SINGAPORE or ST TOURS FRANCE                                                               |

| Wafer fab manufacturing location<br>Wafer Testing (EWS) information<br>Electrical testing manufacturing location<br>Assembly information<br>Assembly site                                            | ST AMK SINGAPORE or ST TOURS FRANCE<br>ST AMK SINGAPORE or ST TOURS FRANCE<br>ST SHENZHEN -CHINA                                         |

| Wafer fab manufacturing locationWafer Testing (EWS) informationElectrical testing manufacturing locationAssembly informationAssembly sitePackage description                                         | ST AMK SINGAPORE or ST TOURS FRANCE         ST AMK SINGAPORE or ST TOURS FRANCE         ST SHENZHEN -CHINA         TO-247                |

| Wafer fab manufacturing location<br>Wafer Testing (EWS) information<br>Electrical testing manufacturing location<br>Assembly information<br>Assembly site<br>Package description<br>Molding compound | ST AMK SINGAPORE or ST TOURS FRANCE<br>ST AMK SINGAPORE or ST TOURS FRANCE<br>ST SHENZHEN -CHINA<br>TO-247<br>ECOPACK®2 ("Halogen-free") |

IPG (Industrial and Power Group) ASD & IPAD division Quality and Reliability

|                                           | STPSCxxxW                               |

|-------------------------------------------|-----------------------------------------|

| Wafer/Die fab. information                |                                         |

| Wafer fab manufacturing location          | ST CATANIA ITALY                        |

| Wafer Testing (EWS) information           |                                         |

| Electrical testing manufacturing location | ST CATANIA ITALY                        |

| Assembly information                      |                                         |

| Assembly site                             | ST SHENZHEN -CHINA                      |

| Package description                       | TO-247                                  |

| Molding compound                          | ECOPACK <sup>®</sup> 2 ("Halogen-free") |

| Lead finishing material                   | Tin 100%                                |

| Final testing information                 |                                         |

| Testing location                          | ST SHENZHEN -CHINA                      |

## **5 TESTS RESULTS SUMMARY**

## 5.1 Test vehicle

| Lot # | Part Number  | Package | Technology family     | Comments                                                      |

|-------|--------------|---------|-----------------------|---------------------------------------------------------------|

| 1     | STTH100W06CW | TO-247  | Rectifier Turboswitch | -Big die<br>-Ribbon bonding                                   |

| 2     | STPSC2006CW  | TO-247  | Power Shottky SiC     | -Big die SiC<br>-Dual configuration                           |

| 3     | STTH3012W    | DO-247  | Rectifier Turboswitch | -Highest voltage<br>-2-leads package                          |

| 4     | STPS80170CW  | TO-247  | Power Schottky        | -Highest voltage Schottky<br>-Big die<br>-Multi-wires bonding |

| 5     | STPS4045CWY  | TO-247  | Power Schottky        | -Low voltage Schottky<br>-Standard Al 20mils bonding          |

Detailed results in below chapter will refer to these references.

# 5.2 Test plan and results summary

| Tes<br>, Std ref. Conditions |                                  | SS                                                                 | Steps /<br>durati | Failure/SS |                |      |      |      |      |

|------------------------------|----------------------------------|--------------------------------------------------------------------|-------------------|------------|----------------|------|------|------|------|

| t                            | Sturei.                          | Conditions                                                         | 55                | on         | L1             | L2   | L3   | L4   | L5   |

| HTRB                         | JESD22<br>A-108                  | VR = 0.8xVRRM = 960V<br>Tj = 175°C for GD1 150°C<br>for other lots | 231               | 1000h      |                | 0/77 | 0/77 | 0/77 |      |

| THB                          | JESD22<br>A-101                  | 85% RH, 85°C<br>VR=100V                                            | 231               | 1000h      | 0/77           | 0/77 |      |      | 0/77 |

| DPA                          | A after TC (A                    | EC-Q101)                                                           | 2                 | N/A        | Accep<br>table |      |      |      |      |

| ŢĊ                           | JESD22<br>A-104                  | -65 / +150°C<br>2 cycles/hour                                      | 231               | 1000cy     | 0/77           | 0/77 |      | 0/77 |      |

| DPA                          | DPA after TC (AEC-Q101)          |                                                                    | 2                 | N/A        | Accep<br>table |      |      |      |      |

| AC                           | JESD22<br>A-102                  | 121°C 2bar<br>100% RH                                              | 231               | 96h        | 0/77           | 0/77 |      | 0/77 |      |

| ΙΟΓΙ                         | Mil Std<br>750<br>method<br>1037 | $\Delta Tc = 85^{\circ}C$<br>$t_{on} = t_{off} = 300s$             | 231               | 6kcy       | 0/77           | 0/77 |      |      | 0/77 |

| RSH                          | JESD22<br>B-106                  | Oil bath*<br>245°C<br>10sec/dip<br>2 dips                          | 10                | N/A        | 0/10           |      |      |      |      |

| S                            | ST<br>internal<br>0018688        | Wet ageing + Sn/Pb bath<br>Wet ageing + Sn/Ag/Cu<br>bath           | 30                |            | 0/15<br>0/15   |      |      |      |      |

\*oil bath dipping with all the package dipped is assumed to be more stressing than lead dipping in solder bath in terms if die temperature profile.

## 6 ANNEXES

# 6.1 **Tests description**

| Test name                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die Oriented                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <b>HTRB</b><br>High Temperature<br>Reverse Bias    | The device is stressed in static configuration, trying<br>to satisfy as much as possible the following<br>conditions:<br>low power dissipation;<br>max. supply voltage compatible with diffusion<br>process and internal circuitry limitations;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | To determine the effects of bias conditions and<br>temperature on solid state devices over time. It<br>simulates the devices operating condition in an<br>accelerated way.<br>To maximize the electrical field across either reverse-<br>biased junctions or dielectric layers, in order to<br>investigate the failure modes linked to mobile<br>contamination, oxide ageing, layout sensitivity to<br>surface effects.  |

| Package Oriented                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ТНВ                                                | The device is biased in static configuration minimizing its internal power dissipation, and stored at controlled conditions of ambient temperature and relative humidity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | To evaluate the package moisture resistance with electrical field applied, both electrolytic and galvanic corrosion are put in evidence.                                                                                                                                                                                                                                                                                 |

| <b>TC</b><br>Temperature Cycling                   | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | To investigate failure modes related to the thermo-<br>mechanical stress induced by the different thermal<br>expansion of the materials interacting in the die-<br>package system. Typical failure modes are linked to<br>metal displacement, dielectric cracking, molding<br>compound delamination, wire-bonds failure, die-attach<br>layer degradation.                                                                |

| PCT<br>Pressure Cooker Test<br>(Autoclave)         | The device is stored in saturated steam, at fixed and controlled conditions of pressure and temperature.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | To investigate corrosion phenomena affecting die or<br>package materials, related to chemical contamination<br>and package hermeticity.                                                                                                                                                                                                                                                                                  |

| <b>IOLT</b><br>Intermittent Operating<br>Life Test | All test samples shall be subjected to the specified<br>number of cycles. When stabilized after initial<br>warm-up cycles, a cycle shall consist of an "on"<br>period, when power is applied suddenly, not<br>gradually, to the device for the time necessary to<br>achieve a delta case temperature (delta is the high<br>minus the low mounting surface temperatures) of<br>+85°C (+60°C for thyristors) +15°C, -5°C, followed by<br>an off period, when the power is suddenly removed,<br>for cooling the case through a similar delta<br>temperature.<br>Auxiliary (forced) cooling is permitted during the off<br>period only. Heat sinks are not intended to be used<br>in this test, however, small heat sinks may be used<br>when it is otherwise difficult to control case<br>temperature of test samples, such as with small<br>package types (e.g., TO39). | The purpose of this test is to determine compliance<br>with the specified numbers of cycles for devices<br>subjected to the specified conditions. It accelerates the<br>stresses on all bonds and interfaces between the chip<br>and mounting face of devices subjected to repeated<br>turn on and off of equipment and is therefore most<br>appropriate for case mount style (e.g., stud, flange,<br>and disc) devices. |

| <b>RSH</b><br>Resistance to Solder<br>Heat         | Package is dipped by the leads 2 times in a solder bath.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | To simulate wave soldering process and verify that package will not be thermally damaged during this step.                                                                                                                                                                                                                                                                                                               |

| <b>SD</b><br>Solderability                         | Wet ageing + dipping in a solder bath. Assessment by visual inspection of the leads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | To check package ability to be soldered with no difficulty. To simulate                                                                                                                                                                                                                                                                                                                                                  |

# **Reliability Report**

Assembly and Testing transfer from the ST plant of Longgang to ST Shenzhen and introduction of the leads electroplating finishing for the AUTOMOTIVE products housed in TO-247 package.

| Genera                  | al Information                                                               |                                                    | Locations                                          |

|-------------------------|------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| Product Lines:          | M5F9 – M264 – 2F6B – 2F69                                                    | Wafer Diffusion<br>Plants:                         | Ang Mo Kio (Singapore)<br>Catania CT6/CT8 (Italy)  |

| Product Families:       | Power MOSFET                                                                 | EWS Plants:                                        | Ang Mo Kio (Singapore)<br>Catania (Italy)          |

| P/Ns:                   | STW78N65M5(M5F9)STW19NM60N(M264)STW47NM60ND(2F6B)STW55NM60ND(2F69)           | Assembly and<br>testing plant:<br>Reliability Lab: | ST Shenzhen (China)<br>IPG-PTD Catania Reliability |

| Product Group:          | IPG                                                                          | ,                                                  | Lab.                                               |

| Product division:       | Power Transistor Division                                                    |                                                    |                                                    |

| Package:                | TO-247                                                                       |                                                    |                                                    |

| Silicon Process techn.: | MDmesh™ V Power MOSFET<br>MDmesh™ II Power MOSFET<br>FDmesh™ II Power MOSFET |                                                    |                                                    |

#### **DOCUMENT INFORMATION**

| Version | Date      | Pages | Prepared by   | Approved by | Comment     |

|---------|-----------|-------|---------------|-------------|-------------|

| 1.0     | June 2014 | 16    | A. Settinieri | C. Cappello | First issue |

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

### TABLE OF CONTENTS

| 1 | APPLICABLE AND REFERENCE DOCUMENTS | 3  |

|---|------------------------------------|----|

| 2 | GLOSSARY                           | 3  |

| 3 | RELIABILITY EVALUATION OVERVIEW    | 3  |

|   | 3.1 OBJECTIVES                     | 3  |

|   | 3.2 CONCLUSION                     | 3  |

| 4 | DEVICE CHARACTERISTICS             | 4  |

|   | 4.1 DEVICE DESCRIPTION             | 4  |

|   | 4.2 CONSTRUCTION NOTE              | 4  |

| 5 | TESTS RESULTS SUMMARY              | 8  |

|   | 5.1 TEST VEHICLE                   | 8  |

|   | 5.2 RELIABILITY TEST PLAN SUMMARY  | 8  |

| 6 | ANNEXES 6.0                        | 10 |

|   | 6.1Tests Description               | 10 |

## **1 APPLICABLE AND REFERENCE DOCUMENTS**

| Document reference | Short description                                                      |

|--------------------|------------------------------------------------------------------------|

| AEC-Q101 rev.C     | Stress test qualification for automotive grade discrete semiconductors |

|                    |                                                                        |

### 2 GLOSSARY

| DUT | Device Under Test |  |

|-----|-------------------|--|

| SS  | Sample Size       |  |

| HF  | Halogen Free      |  |

## **<u>3 RELIABILITY EVALUATION OVERVIEW</u>**

#### 3.1 Objectives

Reliability evaluation for assembly and testing transfer from the ST plant of Longgang to ST Shenzhen and introduction of the leads electroplating finishing for the automotive products housed in TO-247 package.

### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. It is stressed that reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the ruggedness of the products and safe operation, which is consequently expected during their lifetime.

## **<u>4 DEVICE CHARACTERISTICS</u>**

### 4.1 **Device description**

N-channel Power MOSFET

## 4.2 Construction note

### D.U.T.: STW78N65M5 LINE: M5F9 PACKAGE: TO-247

| Wafer/Die fab. Information       |                              |  |

|----------------------------------|------------------------------|--|

| Wafer fab manufacturing location | Catania CT8 (Italy)          |  |

| Technology                       | MDmesh™ V Power MOSFET       |  |

| Die finishing back side          | Ti/Ni/Ag                     |  |

| Die size                         | 10410 x 6810 µm <sup>2</sup> |  |

| Metal                            | AlCu/Ti/TiN                  |  |

| Passivation type                 | Nitride                      |  |

| Wafer Testing (EWS) information           |                     |  |

|-------------------------------------------|---------------------|--|

| Electrical testing manufacturing location | Catania CT8 (Italy) |  |

| Test program                              | WPIS                |  |

| Assembly information                |                               |  |

|-------------------------------------|-------------------------------|--|

| Assembly site                       | ST Shenzhen (China)           |  |

| Package description                 | TO-247                        |  |

| Molding compound                    | HF Epoxy Resin                |  |

| Frame material                      | Raw Copper                    |  |

| Die attach process                  | Soft Solder                   |  |

| Die attach material                 | Pb/Sn/Ag                      |  |

| Wire bonding process                | Ultrasonic                    |  |

| Wires bonding materials             | AI/Mg Gate – Source Ribbon AI |  |

| Lead finishing/bump solder material | Pure Tin                      |  |

| Final testing information |                     |

|---------------------------|---------------------|

| Testing location          | ST Shenzhen (China) |

| Tester                    | IPTEST              |

### D.U.T.: STW19NM60N LINE: M264 PACKAGE: TO-247

| Wafer/Die fab. Information       |                             |

|----------------------------------|-----------------------------|

| Wafer fab manufacturing location | Ang Mo Kio (Singapore)      |

| Technology                       | MDmesh™ II Power MOSFET     |

| Die finishing back side          | Ti/Ni/Ag                    |

| Die size                         | 4400 x 3200 μm <sup>2</sup> |

| Metal                            | Al/Si                       |

| Passivation type                 | Nitride                     |

| Wafer Testing (EWS) information           |                        |

|-------------------------------------------|------------------------|

| Electrical testing manufacturing location | Ang Mo Kio (Singapore) |

| Test program                              | WPIS                   |

| Assembly information                |                        |

|-------------------------------------|------------------------|

| Assembly site                       | ST Shenzhen (China)    |

| Package description                 | TO-247                 |

| Molding compound                    | HF Epoxy Resin         |

| Frame material                      | Raw Copper             |

| Die attach process                  | Soft Solder            |

| Die attach material                 | Pb/Sn/Ag               |

| Wire bonding process                | Ultrasonic             |

| Wires bonding materials             | AI/Mg Gate – AI Source |

| Lead finishing/bump solder material | Pure Tin               |

| Final testing information |                     |

|---------------------------|---------------------|

| Testing location          | ST Shenzhen (China) |

| Tester                    | IPTEST              |

### D.U.T.: STW47NM60ND LINE: 2F6B PACKAGE: TO-247

| Wafer/Die fab. Information       |                             |  |

|----------------------------------|-----------------------------|--|

| Wafer fab manufacturing location | Catania CT6 (Italy)         |  |

| Technology                       | FDmesh™ II Power MOSFET     |  |

| Die finishing back side          | Ti/Ni/Ag                    |  |

| Die size                         | 8800 x 5760 μm <sup>2</sup> |  |

| Metal                            | Al/Si                       |  |

| Passivation type                 | Nitride                     |  |

| Wafer Testing (EWS) information           |                     |

|-------------------------------------------|---------------------|

| Electrical testing manufacturing location | Catania CT6 (Italy) |

| Test program                              | WPIS                |

| Assembly information                |                               |

|-------------------------------------|-------------------------------|

| Assembly site                       | ST Shenzhen (China)           |

| Package description                 | TO-247                        |

| Molding compound                    | HF Epoxy Resin                |

| Frame material                      | Raw Copper                    |

| Die attach process                  | Soft Solder                   |

| Die attach material                 | Pb/Sn/Ag                      |

| Wire bonding process                | Ultrasonic                    |

| Wires bonding materials             | Al/Mg Gate – Source Ribbon Al |

| Lead finishing/bump solder material | Pure Tin                      |

| Final testing information |                     |

|---------------------------|---------------------|

| Testing location          | ST Shenzhen (China) |

| Tester                    | IPTEST              |

### D.U.T.: STW55NM60ND LINE: 2F69 PACKAGE: TO-247

| Wafer/Die fab. Information       |                              |  |

|----------------------------------|------------------------------|--|

| Wafer fab manufacturing location | Catania CT6 (Italy)          |  |

| Technology                       | FDmesh™ II Power MOSFET      |  |

| Die finishing back side          | Ti/Ni/Ag                     |  |

| Die size                         | 10390 x 6850 μm <sup>2</sup> |  |

| Metal                            | Al/Si                        |  |

| Passivation type                 | Nitride                      |  |

| Wafer Testing (EWS) information           |                     |

|-------------------------------------------|---------------------|

| Electrical testing manufacturing location | Catania CT6 (Italy) |

| Test program                              | WPIS                |

| Assembly information                |                               |

|-------------------------------------|-------------------------------|

| Assembly site                       | ST Shenzhen (China)           |

| Package description                 | TO-247                        |

| Molding compound                    | HF Epoxy Resin                |

| Frame material                      | Raw Copper                    |

| Die attach process                  | Soft Solder                   |

| Die attach material                 | Pb/Sn/Ag                      |

| Wire bonding process                | Ultrasonic                    |

| Wires bonding materials             | Al/Mg Gate – Source Ribbon Al |

| Lead finishing/bump solder material | Pure Tin                      |

| Final testing information            |  |  |  |  |

|--------------------------------------|--|--|--|--|

| Testing location ST Shenzhen (China) |  |  |  |  |

| Tester IPTEST                        |  |  |  |  |

## **5 TESTS RESULTS SUMMARY**

## 5.1 Test vehicle

| Lot # | Process/ Package | Product Line | Comments     |

|-------|------------------|--------------|--------------|

| 1     | STW78N65M5       | M5F9         |              |

| 2     | STW19NM60N       | M264         |              |

| 3     | STW47NM60ND      | 2F6B         | Power MOSFET |

| 4     | STW55NM60ND      | 2F69         |              |

### 5.2 Reliability test plan summary

| #  | Stress<br>(Abrv)           | PC | Std ref.                   | Conditions                                                                            | Sample<br>Size | Steps                             | Failure/SS                   |                              |                              |                              |  |

|----|----------------------------|----|----------------------------|---------------------------------------------------------------------------------------|----------------|-----------------------------------|------------------------------|------------------------------|------------------------------|------------------------------|--|

|    |                            |    |                            |                                                                                       | (S.S.)         |                                   | Lot 1<br>M5F9                | Lot 2<br>M264                | Lot 3<br>2F6B                | Lot 4<br>2F69                |  |

| 1  | TEST                       |    | User<br>specification      | All qualification parts tested<br>requirements of the approp<br>device specification. |                |                                   | 0/462                        | 0/462                        | 0/462                        | 0/462                        |  |

| 2  | External visual            |    | JESD22<br>B-101            | All devices submitted for te                                                          | esting         |                                   | 0/462                        | 0/462                        | 0/462                        | 0/462                        |  |

| 3  | Parametric<br>Verification |    | User<br>specification      | all parameters according to<br>user specification from -55°C<br>to 150°C              | 100            |                                   | 0/25                         | 0/25                         | 0/25                         | 0/25                         |  |

| 4  | HTRB                       | Ν  | JESD22<br>A-108            | TA=150°C<br>BIAS=520V (M5F9)<br>BIAS=480V(M264-2F69- 2F6B)<br>TIME=1000 HOURS         | 308            | 168H<br>500H<br>1000H             | 0/77<br>0/77<br>0/77         | 0/77<br>0/77<br>0/77         | 0/77<br>0/77<br>0/77         | 0/77<br>0/77<br>0/77         |  |

| 5  | HTGB                       | N  | JESD22<br>A-108            | TA=150°C<br>BIAS=25V<br>TIME=1000 HOURS                                               | 308            | 168H<br>500H<br>1000H             | 0/77<br>0/77<br>0/77         | 0/77<br>0/77<br>0/77         | 0/77<br>0/77<br>0/77         | 0/77<br>0/77<br>0/77         |  |

| 6  | тс                         | Ν  | JESD22<br>A-104            | TA=-55°C TO 150°C<br>1 HOURS / CYCLE<br>TIME=1000CYCLES                               | 308            | 100cy<br>200cy<br>500cy<br>1000cy | 0/77<br>0/77<br>0/77<br>0/77 | 0/77<br>0/77<br>0/77<br>0/77 | 0/77<br>0/77<br>0/77<br>0/77 | 0/77<br>0/77<br>0/77<br>0/77 |  |

| 7  | AC                         | Ν  | JESD22<br>A-102            | TA=121°C ; PA=2ATM<br>TIME=96H                                                        | 308            | 96H                               | 0/77                         | 0/77                         | 0/77                         | 0/77                         |  |

| 8  | H3TRB                      | Ν  | JESD22<br>A-101            | TA=85°C ; RH=85%<br>BIAS=100V<br>TIME=1000 HOURS                                      | 308            | 168H<br>500H<br>1000H             | 0/77<br>0/77<br>0/77         | 0/77<br>0/77<br>0/77         | 0/77<br>0/77<br>0/77         | 0/77<br>0/77<br>0/77         |  |

| 9  | IOL / TF                   | Ν  | MIL-STD-750<br>Method 1037 | $\Delta$ TC=105°C<br>Ton / Toff = 5min                                                | 308            | 6Kcy                              | 0/77                         | 0/77                         | 0/77                         | 0/77                         |  |

| 10 | D.P.A.                     |    | AEC-Q101-004<br>Section 4  | Devices after<br>H3TRB - TC                                                           | 16             |                                   | 0/4                          | 0/4                          | 0/4                          | 0/4                          |  |

| 11 | Physical<br>Dimension      |    | JESD22<br>B-100            |                                                                                       | 30             |                                   | 0/30                         |                              |                              |                              |  |

#### IPG (Industrial and Power Group) PTD (Power Transistor Division) Quality and Reliability

Rel 07-14

| 12 | Terminal<br>Strength            | MIL-STD-750<br>Method 2036 | 30                                         | 0/30 |      |      |      |

|----|---------------------------------|----------------------------|--------------------------------------------|------|------|------|------|

| 13 | Resistance<br>to<br>Solder Heat | JESD22<br>B-106            | 30                                         | 0/30 |      |      |      |

| 14 | Solderability                   | J-STD-002                  | 40                                         | 0/10 | 0/10 | 0/10 | 0/10 |

| 15 | Wire Bond<br>Strength           | MIL-STD-750<br>Method 2037 | 10<br>bonds<br>from min<br>of 5<br>devices | 0/10 |      |      |      |

| 16 | Wire Bond<br>Shear              | AEC-Q101-<br>003           | 10<br>bonds<br>from min<br>of 5<br>devices | 0/10 |      |      |      |

| 17 | Die Shear                       | MIL-STD-750<br>Method 2017 | 5                                          | 0/5  |      |      |      |

# 6 ANNEXES 6.0

# 6.1Tests Description

| Test name                                                                                                                                                                                                                | Description                                                                                                                                   | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Die Oriented Tests                                                                                                                                                                                                       |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| HTRB<br>High Temperature<br>Reverse Bias                                                                                                                                                                                 | The device is stressed in static configuration,<br>trying to satisfy as much as possible the<br>following conditions:                         | To determine the effects of bias conditions and<br>temperature on solid state devices over time. It<br>simulates the devices' operating condition in an<br>accelerated way.<br>To maximize the electrical field across either<br>reverse-biased junctions or dielectric layers, in<br>order to investigate the failure modes linked to<br>mobile contamination, oxide ageing, layout<br>sensitivity to surface effects. |  |  |  |  |  |

| <b>HTGB</b><br>High Temperature<br>Forward (Gate)<br>Bias                                                                                                                                                                | <ul> <li>low power dissipation;</li> <li>max. supply voltage compatible with diffusion process and internal circuitry limitations;</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| Package Oriented                                                                                                                                                                                                         |                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| AC<br>Auto Clave<br>(Pressure Pot)                                                                                                                                                                                       | The device is stored in saturated steam, at fixed and controlled conditions of pressure and temperature.                                      | To investigate corrosion phenomena affecting die or package materials, related to chemical contamination and package hermeticity.                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| <b>TC</b><br>Temperature<br>Cycling                                                                                                                                                                                      | The device is submitted to cycled<br>temperature excursions, between a hot and a<br>cold chamber in air atmosphere.                           | To investigate failure modes related to the<br>thermo-mechanical stress induced by the<br>different thermal expansion of the materials<br>interacting in the die-package system. Typical<br>failure modes are linked to metal displacement,<br>dielectric cracking, molding compound<br>delamination, wire-bonds failure, die-attach<br>layer degradation.                                                              |  |  |  |  |  |

| <b>TF / IOL</b><br>Thermal Fatigue /<br>Intermittent<br>Operating Life                                                                                                                                                   | The device is submitted to cycled<br>temperature excursions generated by power<br>cycles (ON/OFF) at T ambient.                               | To investigate failure modes related to the<br>thermo-mechanical stress induced by the<br>different thermal expansion of the materials<br>interacting in the die-package system. Typical<br>failure modes are linked to metal displacement,<br>dielectric cracking, molding compound<br>delamination, wire-bonds failure, die-attach<br>layer degradation.                                                              |  |  |  |  |  |

| H3TRB<br>Temperature<br>Humidity Bias The device is biased in static configuration<br>minimizing its internal power dissipation, and<br>stored at controlled conditions of ambient<br>temperature and relative humidity. |                                                                                                                                               | To evaluate the package moisture resistance<br>with electrical field applied, both electrolytic and<br>galvanic corrosion are put in evidence.                                                                                                                                                                                                                                                                          |  |  |  |  |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

**RESTRICTIONS OF USE AND CONFIDENTIALITY OBLIGATIONS:**

THIS DOCUMENT AND ITS ANNEXES CONTAIN ST PROPRIETARY AND CONFIDENTIAL INFORMATION. THE DISCLOSURE, DISTRIBUTION, PUBLICATION OF WHATSOEVER NATURE OR USE FOR ANY OTHER PURPOSE THAN PROVIDED IN THIS DOCUMENT OF ANY INFORMATION CONTAINED IN THIS DOCUMENT AND ITS ANNEXES IS SUBMITTED TO ST PRIOR EXPRESS AUTHORIZATION. ANY UNAUTHORIZED REVIEW, USE, DISCLOSURE OR DISTRIBUTION OF SUCH INFORMATION IS EXPRESSLY PROHIBITED.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2014 STMicroelectronics - All rights reserved.

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com