SNAS254B-OCTOBER 2006-REVISED APRIL 2017

LM98714

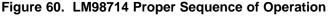

# LM98714 Three Channel, 16-Bit, 45 MSPS Analog Front End With LVDS/CMOS Output and Integrated CCD/CIS Sensor Timing Generator

#### Features 1

Texas

Instruments

- LVDS/CMOS Outputs

- LVDS/CMOS Pixel Rate Input Clock or ADC Input Clock

- CDS or S/H Processing for CCD or CIS Sensors

- Independent Gain/Offset Correction for Each Channel

- Digital Black Level Correction Loop for Each Channel

- Programmable Input Clamp Voltage

- Flexible CCD/CIS Sensor Timing Generator

- **Key Specifications**

- Maximum Input Level: 1.2 or 2.4 Volt Modes (Both with + or – Polarity Option)

- ADC Resolution: 16-Bit

- ADC Sampling Rate: 45 MSPS

- INL: ±23 LSB (Typ)

- Channel Sampling Rate: 15/22.5/30 MSPS

- PGA Gain Steps: 256 Steps

- PGA Gain Range: 0.7 to 7.84x

- Analog DAC Resolution: ±9 Bits

- Analog DAC Range: ±300 mV or ±600 mV

- Digital DAC Resolution: ±6 Bits

- Digital DAC Range: -1024 LSB to + 1008 LSB

- SNR: -74dB (at 0 dB PGA Gain)

- Power Dissipation: 505 mW (LVDS) 610 mW (CMOS)

- Operating Temp: 0 to 70°C

- Supply Voltage: 3.3 V Nominal (3.0 V to 3.6 V Range)

# 2 Applications

- **Multi-Function Peripherals** •

- **Facsimile Equipment**

- Flatbed or Handheld Color Scanners •

- **High-Speed Document Scanner**

# 3 Description

The LM98714 is a fully integrated, high performance 16-Bit, 45 MSPS signal processing solution for digital color copiers, scanners, and other image processing applications. High-speed signal throughput is achieved with an innovative architecture utilizing Correlated Double Sampling (CDS), typically employed with CCD arrays, or Sample and Hold (S/H) inputs (for Contact Image Sensors and CMOS image sensors). The signal paths utilize 8 bit Programmable Gain Amplifiers (PGA), a ±9-Bit offset correction DAC and independently controlled Digital Black Level correction loops for each input. The PGA and offset DAC are programmed independently allowing unique values of gain and offset for each of the three inputs. The signals are then routed to a 45 MHz high performance analog-to-digital converter (ADC). The fully differential processing channel shows exceptional noise immunity, having a very low noise floor of -74dB. The 16-bit ADC has excellent performance LM98714 dynamic making the transparent in the image reproduction chain.

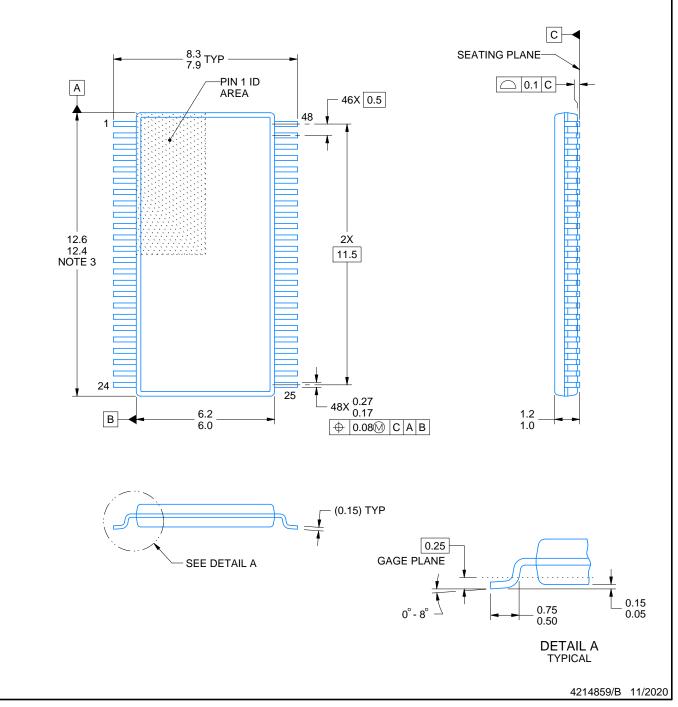

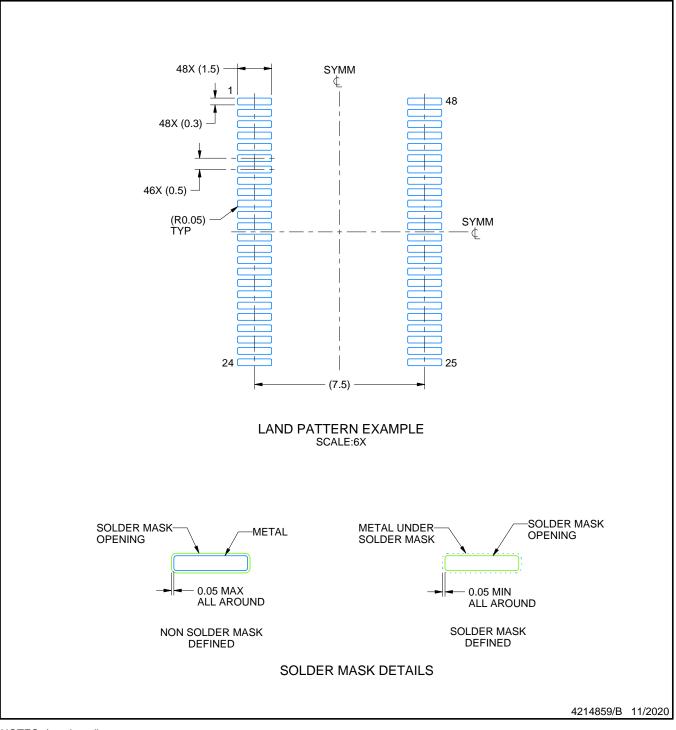

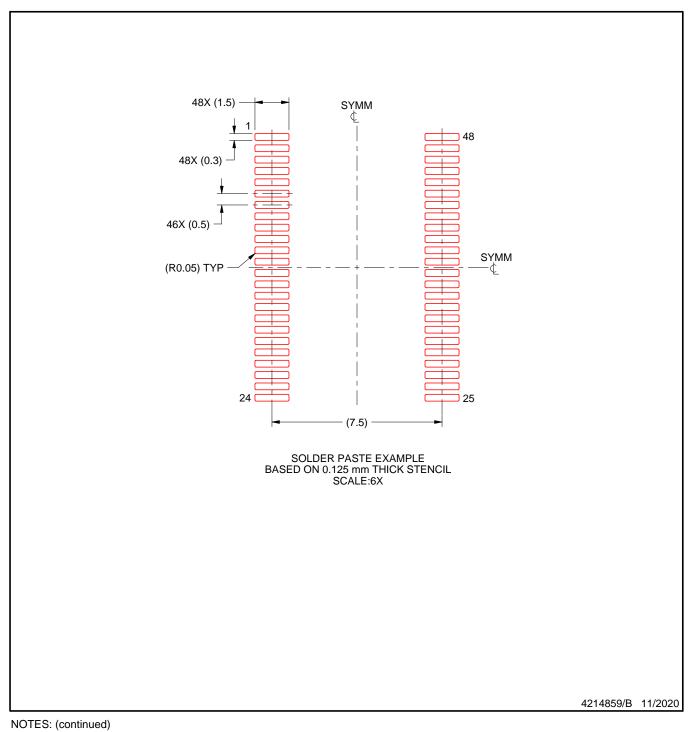

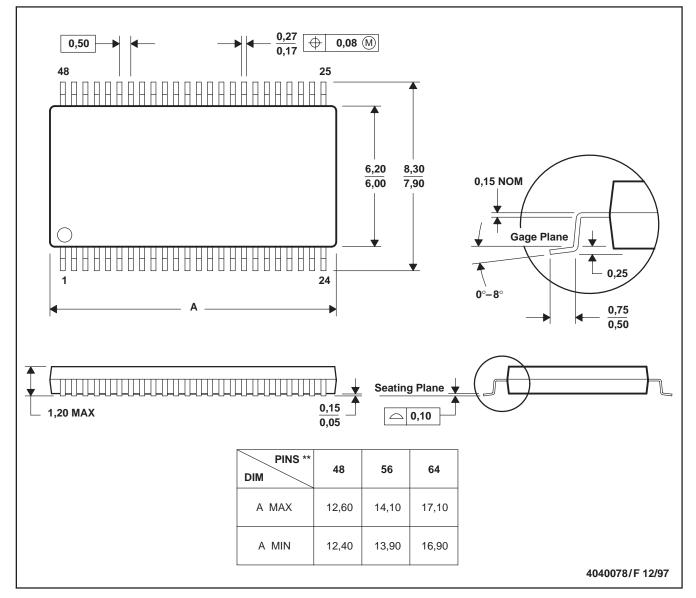

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| LM98714     | TSSOP (48) | 12.50 mm × 6.1 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

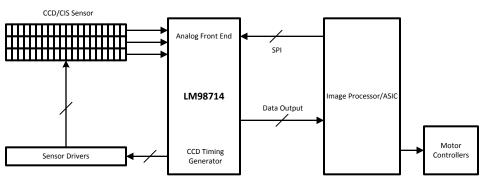

# System Block Diagram

Features ..... 1

Applications ..... 1 Description ..... 1

Revision History..... 2 Pin Configuration and Functions...... 3

6.1 Absolute Maximum Ratings ...... 5 ESD Ratings......5

6.7 Typical Characteristics ..... 11

Detailed Description ..... 12 7.1 Overview ...... 12

Recommended Operating Conditions ...... 5

1

2

3 4

5 6

7

6.2

6.3

2

# **Table of Contents**

|    | 7.2  | Functional Block Diagram                        | 12        |

|----|------|-------------------------------------------------|-----------|

|    | 7.3  | Feature Description                             | 13        |

|    | 7.4  | Device Functional Modes                         | 53        |

|    | 7.5  | Programming                                     | <b>60</b> |

|    | 7.6  | Register Maps                                   | 62        |

| 8  | Арр  | lication and Implementation                     | 87        |

|    | 8.1  | Typical Application                             | 87        |

| 9  | Dev  | ice and Documentation Support                   | 88        |

|    | 9.1  | Documentation Support                           | 88        |

|    | 9.2  | Receiving Notification of Documentation Updates | 88        |

|    | 9.3  | Community Resources                             | 88        |

|    | 9.4  | Trademarks                                      | 88        |

|    | 9.5  | Electrostatic Discharge Caution                 | 88        |

|    | 9.6  | Glossary                                        | 88        |

| 10 | Med  | hanical, Packaging, and Orderable               |           |

|    | Info | rmation                                         | 88        |

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | hanges from Revision A (January 2014) to Revision B                                                                                                                                                                                                                                                                          | Page |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • | Added Pin Configuration and Functions section, ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1    |

| • | Changed the maximum values for the CMOS clock high and low input current parameters in the <i>Electrical Characteristics</i> table                                                                                                                                                                                           | 6    |

| C | hanges from Original (October 2006) to Revision A                                                                                                                                                                                                                                                                            | Page |

| • | Added content to complete full data sheet.                                                                                                                                                                                                                                                                                   | 1    |

STRUMENTS www.ti.com

EXAS

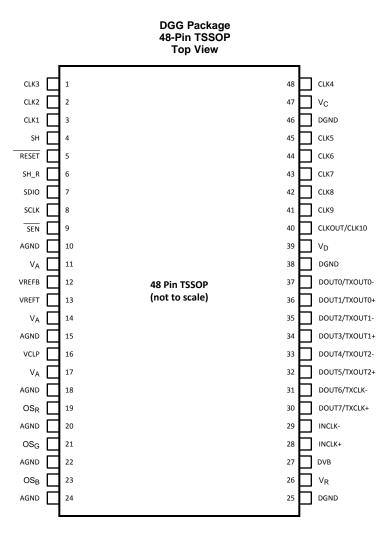

# 5 Pin Configuration and Functions

#### **Pin Functions**

|     | PIN            | I/O <sup>(1)</sup> | TYPE <sup>(1)</sup> | RES. <sup>(1)</sup> | DESCRIPTION                                                                                               |

|-----|----------------|--------------------|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------|

| NO. | NAME           | 1/0                | TTPE                | RE5.07              | DESCRIPTION                                                                                               |

| 1   | CLK3           | 0                  | D                   | PU                  | Configurable sensor control output.                                                                       |

| 2   | CLK2           | 0                  | D                   | PD                  | Configurable sensor control output.                                                                       |

| 3   | CLK1           | 0                  | D                   | PU                  | Configurable sensor control output.                                                                       |

| 4   | SH             | 0                  | D                   | PD                  | Sensor - Shift or transfer control signal for CCD and CIS sensors.                                        |

| 5   | RESET          | I                  | D                   | PU                  | Active-low master reset. NC when function not being used.                                                 |

| 6   | SH_R           | I                  | D                   | PD                  | External request for an SH pulse.                                                                         |

| 7   | SDIO           | I/O                | D                   |                     | Serial Interface Data Input                                                                               |

| 8   | SCLK           | I                  | D                   | PD                  | Serial Interface shift register clock.                                                                    |

| 9   | SEN            | I                  | D                   | PU                  | Active-low chip enable for the Serial Interface.                                                          |

| 10  | AGND           | —                  | Р                   | —                   | Analog ground return.                                                                                     |

| 11  | VA             | _                  | Р                   | —                   | Analog power supply. Bypass voltage source with $4.7\mu F$ and pin with $0.1\mu F$ to AGND.               |

| 12  | VREFB          | 0                  | А                   | —                   | Bottom of ADC reference. Bypass with a 0.1µF capacitor to ground.                                         |

| 13  | VREFT          | 0                  | Α                   | _                   | Top of ADC reference. Bypass with a $0.1 \mu F$ capacitor to ground.                                      |

| 14  | V <sub>A</sub> | _                  | Р                   | _                   | Analog power supply. Bypass voltage source with 4.7 $\mu\text{F}$ and pin with 0.1 $\mu\text{F}$ to AGND. |

| 15  | AGND           | —                  | Р                   | —                   | Analog ground return.                                                                                     |

(1) I = Input, O = Output, IO = Bi-directional, P = Power, D = Digital, A = Analog, PU = Pullup with an internal resistor, PD = Pulldown with an internal resistor.

LM98714 SNAS254B-OCTOBER 2006-REVISED APRIL 2017

www.ti.com

Texas Instruments

# Pin Functions (continued)

| NO. | PIN<br>NAME       | I/O <sup>(1)</sup> | TYPE <sup>(1)</sup> | RES. <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                 |

|-----|-------------------|--------------------|---------------------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  | VCLP              | ю                  | A                   | _                   | Input Clamp Voltage. Normally bypassed with a $0.1\mu$ F, and a $4.7\mu$ F capacitor to AGND. An external reference voltage may be applied to this pin.                     |

| 16  | VCLP              | ю                  | А                   | _                   | Input Clamp Voltage. Normally bypassed with a $0.1\mu F$ , and a $10\mu F$ capacitor to AGND. An external reference voltage may be applied to this pin.                     |

| 17  | V <sub>A</sub>    | —                  | Р                   | _                   | Analog power supply. Bypass voltage source with $4.7\mu F$ and pin with $0.1\mu F$ to AGND.                                                                                 |

| 18  | AGND              | _                  | Р                   | —                   | Analog ground return.                                                                                                                                                       |

| 19  | OS <sub>R</sub>   | I                  | А                   | —                   | Analog input signal. Typically sensor Red output AC-coupled through a capacitor.                                                                                            |

| 20  | AGND              |                    | Р                   | —                   | Analog ground return.                                                                                                                                                       |

| 21  | OS <sub>G</sub>   | I                  | А                   | —                   | Analog input signal. Typically sensor Green output AC-coupled through a capacitor.                                                                                          |

| 22  | AGND              |                    | Р                   | —                   | Analog ground return.                                                                                                                                                       |

| 23  | OS <sub>B</sub>   | I                  | А                   | —                   | Analog input signal. Typically sensor Blue output AC-coupled through a capacitor.                                                                                           |

| 24  | AGND              | _                  | Р                   | —                   | Analog ground return.                                                                                                                                                       |

| 25  | DGND              | —                  | Р                   | —                   | Digital ground return.                                                                                                                                                      |

| 26  | V <sub>R</sub>    | -                  | Р                   | _                   | Power supply input for internal voltage reference generator. Bypass this supply pin with a $0.1 \mu\text{F}$ capacitor.                                                     |

| 27  | DVB               | 0                  | D                   | —                   | Digital Core Voltage bypass. Not an input. Bypass with 0.1µF capacitor to DGND.                                                                                             |

| 28  | INCLK+            | I                  | D                   | _                   | Clock Input. Non-Inverting input for LVDS clocks or CMOS clock input. CMOS clock is selected when pin 29 is held at DGND, otherwise clock is configured for LVDS operation. |

| 29  | INCLK-            | I                  | D                   | —                   | Clock Input. Inverting input for LVDS clocks, connect to DGND for CMOS clock.                                                                                               |

| 30  | DOUT7/<br>TXCLK+  | 0                  | D                   | _                   | Bit 7 of the digital video output bus in CMOS Mode, LVDS Frame Clock+ in LVDS Mode.                                                                                         |

| 31  | DOUT6/<br>TXCLK-  | 0                  | D                   | _                   | Bit 6 of the digital video output bus in CMOS Mode, LVDS Frame Clock- in LVDS Mode.                                                                                         |

| 32  | DOUT5/<br>TXOUT2+ | 0                  | D                   |                     | Bit 5 of the digital video output bus in CMOS Mode, LVDS Data Out2+ in LVDS Mode.                                                                                           |

| 33  | DOUT4/<br>TXOUT2- | 0                  | D                   | _                   | Bit 4 of the digital video output bus in CMOS Mode, LVDS Data Out2- in LVDS Mode.                                                                                           |

| 34  | DOUT3/<br>TXOUT1+ | 0                  | D                   | _                   | Bit 3 of the digital video output bus in CMOS Mode, LVDS Data Out1+ in LVDS Mode.                                                                                           |

| 35  | DOUT2/<br>TXOUT1- | 0                  | D                   | _                   | Bit 2 of the digital video output bus in CMOS Mode, LVDS Data Out1- in LVDS Mode.                                                                                           |

| 36  | DOUT1/<br>TXOUT0+ | 0                  | D                   | _                   | Bit 1 of the digital video output bus in CMOS Mode, LVDS Data Out0+ in LVDS Mode.                                                                                           |

| 37  | DOUT0/<br>TXOUT0- | 0                  | D                   | _                   | Bit 0 of the digital video output bus in CMOS Mode, LVDS Data Out0- in LVDS Mode.                                                                                           |

| 38  | DGND              | _                  | Р                   | _                   | Digital ground return.                                                                                                                                                      |

| 39  | V <sub>D</sub>    | _                  | Р                   | _                   | Power supply for the digital circuits. Bypass this supply pin with 0.1µF capacitor. A single 4.7µF capacitor should be used between the supply and the VD, VR and VC pins.  |

| 40  | CLKOUT/<br>CLK10  | 0                  | D                   | PD                  | Output clock for registering output data when using CMOS outputs, or configurable sensor control output.                                                                    |

| 41  | CLK9              | 0                  | D                   | PD                  | Configurable sensor control output.                                                                                                                                         |

| 42  | CLK8              | 0                  | D                   | PD                  | Configurable sensor control output.                                                                                                                                         |

| 43  | CLK7              | 0                  | D                   | PD                  | Configurable sensor control output.                                                                                                                                         |

| 44  | CLK6              | 0                  | D                   | PU                  | Configurable sensor control output.                                                                                                                                         |

| 45  | CLK5              | 0                  | D                   | PD                  | Configurable sensor control output.                                                                                                                                         |

| 46  | DGND              | —                  | Р                   | _                   | Digital ground return.                                                                                                                                                      |

| 47  | Vc                | —                  | Р                   | —                   | Power supply for the sensor control outputs. Bypass this supply pin with $0.1\mu F$ capacitor.                                                                              |

| 48  | CLK4              | 0                  | D                   | PD                  | Configurable sensor control output.                                                                                                                                         |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

See  $^{\left(1\right)}$  and  $^{\left(2\right)}$

|                                                                | MIN  | MAX      | UNIT |

|----------------------------------------------------------------|------|----------|------|

| Supply voltage (VA,VR,VD,VC)                                   |      | 4.2      | V    |

| Voltage on any input pin (not to exceed 4.2 V) <sup>(3)</sup>  | -0.3 | VA + 0.3 | V    |

| Voltage on any output pin (except DVB and not to exceed 4.2 V) | -0.3 | VA + 0.3 | V    |

| DVB output pin voltage                                         |      | 2        | V    |

| Input current at any pin other than supply pins <sup>(4)</sup> |      | ±25      | mA   |

| Package input current (except supply pins) <sup>(4)</sup>      |      | ±50      | mA   |

| Package dissipation at $T_A = 25^{\circ}C^{(5)}$               |      | 1.89     | W    |

| Maximum junction temperature (T <sub>A</sub> )                 |      | 150      | °C   |

| Storage temperature, T <sub>stg</sub>                          | -65  | 150      | C°   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are measured with respect to AGND = DGND = 0 V, unless otherwise specified.

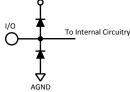

(3) The analog inputs are protected as shown below. Input voltage magnitudes beyond the supply rails will not damage the device, provided the current is limited per note 3. However, input errors will be generated If the input goes above VA and below AGND.

- (4) When the input voltage (V<sub>IN</sub>) at any pin exceeds the power supplies (V<sub>IN</sub> < GND or V<sub>IN</sub> > V<sub>A</sub> or V<sub>D</sub>), the current at that pin should be limited to 25 mA. The 50 mA maximum package input current rating limits the number of pins that can simultaneously safely exceed the power supplies with an input current of 25 mA to two.

- (5) The maximum power dissipation must be derated at elevated temperatures and is dictated by T<sub>JMAX</sub>, θ<sub>JA</sub> and the ambient temperature, T<sub>A</sub>. The maximum allowable power dissipation at any temperature is P<sub>D</sub> = (T<sub>JMAX</sub> T<sub>A</sub>)/θ<sub>JA</sub>. The values for maximum power dissipation listed above will be reached only when the device is operated in a severe fault condition (for example, when input or output pins are driven beyond the power supply voltages, or the power supply polarity is reversed). Such conditions should always be avoided.

# 6.2 ESD Ratings

|        |                         |                                                                   | VALUE | UNIT |

|--------|-------------------------|-------------------------------------------------------------------|-------|------|

| V      | Flaatrootatia diaabarga | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | 2500  | V    |

| V(ESD) | Electrostatic discharge | Machine model (MM)                                                | 250   | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

See (1)

|                       | MIN | NOM MAX | UNIT |

|-----------------------|-----|---------|------|

| All supply voltages   | 3   | 3.6     | V    |

| Operating temperature | 0   | 70      | °C   |

(1) All voltages are measured with respect to AGND = DGND = 0 V, unless otherwise specified.

SNAS254B-OCTOBER 2006-REVISED APRIL 2017

LM98714

# 6.4 Thermal Information

|                       |                                              | LM98714     |      |

|-----------------------|----------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | DGG (TSSOP) | UNIT |

|                       |                                              | 48 PINS     |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 66          | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | —           | °C/W |

| $R_{\thetaJB}$        | Junction-to-board thermal resistance         | —           | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | —           | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | —           | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | _           | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 15 MHz,  $T_A$  = 25°C, unless otherwise specified.

|                  | PARAMETER                                         | TEST CONDITIONS                                                                      | MIN  | TYP <sup>(1)</sup> | MAX  | UNIT |

|------------------|---------------------------------------------------|--------------------------------------------------------------------------------------|------|--------------------|------|------|

| CMOS I           | Digital Input DC Specifications (RESE             | rb, SH_R, SCLK, SENb)                                                                |      |                    |      |      |

| V <sub>IH</sub>  | Logical 1 input voltage                           |                                                                                      | 2    |                    |      | V    |

| V <sub>IL</sub>  | Logical 0 input voltage                           |                                                                                      |      |                    | 0.8  | V    |

|                  |                                                   | $\overline{\text{RESET}}, V_{\text{IH}} = VD$                                        |      | 235                |      | nA   |

| I <sub>IH</sub>  | Logical 1 input current                           | SH_R, SCLK, $V_{IH} = VD$                                                            |      | 70                 |      | μA   |

|                  |                                                   | SEN, V <sub>IH</sub> = VD                                                            |      | 130                |      | nA   |

|                  |                                                   | RESET, VIL = DGND                                                                    |      | 70                 |      | μA   |

| IIL              | Logical 0 input current                           | SH_R, SCLK, VIL = DGND                                                               |      | 235                |      | nA   |

|                  |                                                   | SEN, VIL = DGND                                                                      |      | 70                 |      | μA   |

| CMOS I           | Digital Output DC Specifications (SH, 0           | CLK1 to CLK10, CMOS Data Outputs)                                                    |      |                    |      |      |

| V <sub>OH</sub>  | Logical 1 output voltage                          | $I_{OUT} = -0.5 \text{ mA}$                                                          | 2.95 |                    |      | V    |

| V <sub>OL</sub>  | Logical 0 output voltage                          | I <sub>OUT</sub> = 1.6 mA                                                            |      |                    | 0.25 | V    |

|                  |                                                   | V <sub>OUT</sub> = DGND                                                              |      | 16                 |      | 0    |

| l <sub>os</sub>  | Output short circuit current                      | V <sub>OUT</sub> = VD                                                                |      | -20                |      | mA   |

|                  | CMOS output TRI-STATE current                     | V <sub>OUT</sub> = DGND                                                              |      | 20                 |      |      |

| I <sub>OZ</sub>  |                                                   | V <sub>OUT</sub> = VD                                                                |      | -25                |      | nA   |

| CMOS I           | Digital Input/Output DC Specifications            | (SDIO)                                                                               |      |                    |      |      |

| I <sub>IH</sub>  | Logical 1 input current                           | V <sub>IH</sub> = VD                                                                 |      | 90                 |      | nA   |

| IIL              | Logical 0 input current                           | V <sub>IL</sub> = DGND                                                               |      | 90                 |      | nA   |

| LVDS/C           | MOS Clock Receiver DC Specification               | s (INCLK+ and INCLK- Pins)                                                           |      |                    |      |      |

| V <sub>IHL</sub> | Differential LVDS clock<br>high threshold voltage | R <sub>L</sub> = 100 W, V <sub>CM</sub> (LVDS Input<br>Common Mode Voltage) = 1.25 V |      |                    | 100  | mV   |

| V <sub>ILL</sub> | Differential LVDS clock<br>low threshold voltage  | R <sub>L</sub> = 100 W, V <sub>CM</sub> (LVDS Input<br>Common Mode Voltage) = 1.25 V | -100 |                    |      | mV   |

| V <sub>IHC</sub> | CMOS clock<br>high threshold voltage              | INCLK- = DGND                                                                        | 2    |                    |      | V    |

| V <sub>ILC</sub> | CMOS clock<br>low threshold voltage               | INCLK- = DGND                                                                        |      |                    | 0.8  | V    |

| I <sub>IHL</sub> | CMOS clock input high current                     |                                                                                      |      |                    | 330  | μA   |

| I <sub>ILC</sub> | CMOS clock input low current                      |                                                                                      |      |                    | -160 | μA   |

| LVDS O           | Output DC Specifications                          | · · · · ·                                                                            |      |                    |      |      |

| V <sub>OD</sub>  | Differential output voltage                       | R <sub>L</sub> = 100 Ω                                                               | 180  | 328                | 450  | mV   |

(1) Typical figures are at  $T_A = 25^{\circ}$ C, and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

# **Electrical Characteristics (continued)**

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 15 MHz,  $T_A$  = 25°C, unless otherwise specified.

|                     | PARAMETER                                                             | TEST CONDITIONS                                                                                                                                                  | MIN    | TYP <sup>(1)</sup> | MAX   | UNIT |

|---------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|-------|------|

| V <sub>OS</sub>     | LVDS output offset voltage                                            | R <sub>L</sub> = 100 Ω                                                                                                                                           | 1.17   | 1.23               | 1.3   | V    |

| l <sub>os</sub>     | Output short circuit current                                          | $V_{OUT}$ = 0 V, R <sub>L</sub> = 100 $\Omega$                                                                                                                   |        | 7.9                |       | mA   |

| Power Su            | Ipply Specifications                                                  |                                                                                                                                                                  |        |                    |       |      |

| IA                  | VA analog supply current                                              | VA Normal State                                                                                                                                                  | 60     | 97                 | 125   | mA   |

|                     |                                                                       | VA Low Power State (Powerdown)                                                                                                                                   | 12     | 23                 | 32    |      |

|                     |                                                                       | VR Normal State (LVDS Outputs)                                                                                                                                   | 30     | 64                 | 75    | mA   |

| IR                  | VR digital supply current                                             | CMOS Output Data Format                                                                                                                                          | 15     | 47                 | 55    | mA   |

|                     |                                                                       | LVDS Output Data Format with Data<br>Outputs Disabled                                                                                                            |        | 47                 |       | mA   |

|                     |                                                                       | LVDS Output Data Format                                                                                                                                          |        | 0.05               |       | mA   |

| ID                  | VD digital output driver supply<br>current                            | CMOS Output Data Format<br>(ATE Loading of CMOS Outputs ><br>50 pF)                                                                                              | 12     |                    | 40    | mA   |

| IC                  | VC CCD timing generator output<br>driver supply current               | Typical sensor outputs: SH,<br>CLK1= $\Phi$ 1A, CLK2= $\Phi$ 2A, CLK3= $\Phi$ B,<br>CLK4= $\Phi$ C, CLK5=RS, CLK6=CP<br>(ATE Loading of CMOS Outputs ><br>50 pF) | 0.5    |                    | 12    | mA   |

|                     |                                                                       | LVDS Output Data Format                                                                                                                                          | 350    | 505                | 650   | mW   |

| PWR                 | Average power dissipation                                             | CMOS Output Data Format (ATE<br>Loading of CMOS Outputs > 50 pF)                                                                                                 | 380    | 610                | 700   | mW   |

| Input Sar           | npling Circuit Specifications                                         |                                                                                                                                                                  |        |                    |       |      |

| V <sub>IN</sub>     | Input voltage level                                                   | CDS Gain=1x, PGA Gain=1x                                                                                                                                         |        | 2.3                |       | Vp-р |

| VIN                 | input voltage level                                                   | CDS Gain=2x, PGA Gain= 1x                                                                                                                                        |        | 1.22               |       | vh-h |

|                     |                                                                       | Source Followers Off                                                                                                                                             | 50     |                    | 70    | μA   |

|                     |                                                                       | CDS Gain = 1x<br>OS <sub>x</sub> = VA (OS <sub>x</sub> = AGND)                                                                                                   | (-70)  |                    | (-40) |      |

|                     | Comple and hold made input                                            | Source Followers Off                                                                                                                                             | 75     |                    | 105   |      |

| I <sub>IN_SH</sub>  | Sample and hold mode input leakage current                            | CDS Gain = $2x$<br>OS <sub>X</sub> = VA (OS <sub>X</sub> = AGND)                                                                                                 | (–105) |                    | (–75) | μA   |

|                     |                                                                       | Source Followers On                                                                                                                                              | -200   | -10                | 200   | nA   |

|                     |                                                                       | CDS Gain = $2x$<br>OS <sub>x</sub> = VA (OS <sub>x</sub> = AGND)                                                                                                 | -200   | -16                | 200   |      |

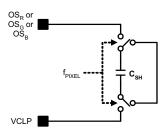

|                     | Sample/hold mode                                                      | CDS Gain = 1x                                                                                                                                                    |        | 2.5                |       |      |

| C <sub>SH</sub>     | equivalent input capacitance<br>(see Figure 5)                        | CDS Gain = 2x                                                                                                                                                    |        | 4                  |       | pF   |

|                     | (See Figure 5)                                                        |                                                                                                                                                                  | -300   | 7                  | 300   |      |

| I <sub>IN_CDS</sub> | CDS mode input leakage current                                        | Source Followers Off<br>$OS_X = VA (OS_X = AGND)$                                                                                                                | -300   | (–25)              | 300   | nA   |

| R <sub>CLPIN</sub>  | CLPIN switch resistance<br>(OS <sub>x</sub> to VCLP Node in Figure 2) |                                                                                                                                                                  |        | 16                 | 50    | Ω    |

| VCLP Re             | ference Circuit Specifications                                        | т <u> </u>                                                                                                                                                       |        |                    |       |      |

|                     | VCLP DAC resolution                                                   |                                                                                                                                                                  |        | 4                  |       | Bits |

|                     | VCLP DAC step size                                                    |                                                                                                                                                                  |        | 0.16               |       | V    |

|                     | VCLP DAC voltage minimum output                                       | VCLP Config.<br>Register = 0001 0000b                                                                                                                            | 0.14   | 0.26               | 0.43  | V    |

| V <sub>VCLP</sub>   | VCLP DAC voltage maximum output                                       | VCLP Config.<br>Register = 0001 1111b                                                                                                                            | 2.38   | 2.68               | 2.93  | V    |

|                     | Resistor ladder enabled                                               | VCLP Config.<br>Register = 0010 xxxxb                                                                                                                            | 1.54   | V <sub>A</sub> / 2 | 1.73  | V    |

| I <sub>SC</sub>     | VCLP DAC short circuit output<br>current                              | VCLP Config.<br>Register = 0001 xxxxb                                                                                                                            |        | 30                 |       | mA   |

# **Electrical Characteristics (continued)**

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 15 MHz,  $T_A$  = 25°C, unless otherwise specified.

|                                          | PARAMETER                           | TEST CONDITIONS                                      | MIN     | TYP <sup>(1)</sup> | MAX    | UNIT  |  |

|------------------------------------------|-------------------------------------|------------------------------------------------------|---------|--------------------|--------|-------|--|

| Black Le                                 | vel Offset DAC Specifications       |                                                      |         |                    |        |       |  |

|                                          | Resolution                          |                                                      |         | 10                 |        | Bits  |  |

|                                          | Monotonicity                        |                                                      | Ensured | by characteriz     | zation |       |  |

|                                          |                                     | CDS Gain = 1x                                        |         | -614               |        |       |  |

|                                          | Offset Adjustment Range Referred    | Minimum DAC Code = 0x000<br>Maximum DAC Code = 0x3FF |         | 614                |        | mV    |  |

|                                          | to AFE Input                        | CDS Gain = 2x                                        |         | -307               |        |       |  |

|                                          |                                     | Minimum DAC Code = 0x000<br>Maximum DAC Code = 0x3FF |         | 307                |        | mV    |  |

|                                          | Offset adjustment range referred to | Minimum DAC Code = 0x000                             | -16000  |                    | -18200 |       |  |

|                                          | AFE output                          | Maximum DAC Code = 0x3FF                             | 16000   |                    | 18200  | LSB   |  |

|                                          |                                     | CDS Gain = 1x                                        |         | 1.2                |        | mV    |  |

|                                          | DAC LSB step size                   | Referred to AFE Output                               |         | (32)               |        | (LSB) |  |

| DNL                                      | Differential nonlinearity           |                                                      | -0.95   |                    | 3.25   | LSB   |  |

| INL                                      | Integral nonlinearity               |                                                      | -3.1    |                    | 2.65   | LSB   |  |

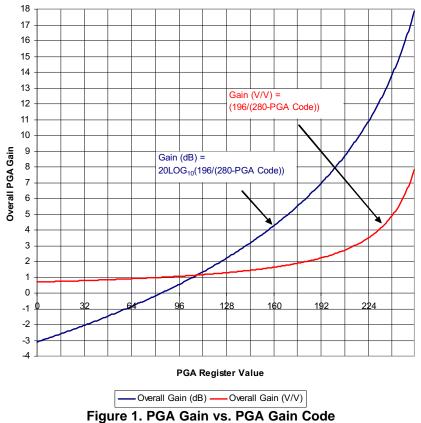

| PGA Spe                                  | cifications                         | + +                                                  |         |                    | Į      |       |  |

|                                          | Gain Resolution                     |                                                      |         | 8                  |        | Bits  |  |

|                                          | Monotonicity                        |                                                      | Ensured | by characteriz     | zation |       |  |

|                                          |                                     | CDS Gain = 1x                                        | 7.18    | 7.9                | 8.77   | V/V   |  |

|                                          | Maximum gain                        | CDS Gain = 1x                                        | 17.1    | 17.9               | 18.9   | dB    |  |

|                                          |                                     | CDS Gain = 1x                                        | 0.56    | 0.7                | 0.82   | V/V   |  |

|                                          | Minimum gain                        | CDS Gain = 1x                                        | -5      | -3                 | -1.72  | dB    |  |

|                                          |                                     | Gain (V/V) = (196/(280-PGA Code))                    |         |                    |        |       |  |

|                                          | PGA function                        | Gain (dB) = 20LOG10(196/(280-<br>PGA Code))          |         |                    |        |       |  |

|                                          |                                     | Minimum PGA Gain                                     |         | 3%                 |        |       |  |

|                                          | Channel matching                    | Maximum PGA Gain                                     |         | 12.7%              |        |       |  |

| ADC Spe                                  | cifications                         |                                                      |         |                    |        |       |  |

| V <sub>REFT</sub>                        | Top of reference                    |                                                      |         | 2.07               |        | V     |  |

| V <sub>REFB</sub>                        | Bottom of reference                 |                                                      |         | 0.89               |        | V     |  |

| V <sub>REFT</sub> -<br>V <sub>REFB</sub> | Differential reference voltage      |                                                      | 1.07    | 1.18               | 1.29   | V     |  |

| 1121 0                                   | Overrange output code               |                                                      |         | 65535              |        |       |  |

|                                          | Underrange output code              |                                                      |         | 0                  |        |       |  |

| Digital Of                               | ffset DAC Specifications            | 1 1                                                  |         |                    |        |       |  |

| -                                        | Resolution                          |                                                      |         | 7                  |        | Bits  |  |

|                                          | Digital offset DAC LSB step size    | Referred to AFE Output                               |         | 16                 |        | LSB   |  |

|                                          | <u> </u>                            | Min DAC Code =7b0000000                              |         | -1024              |        |       |  |

|                                          | Offset adjustment range             | Mid DAC Code =7b1000000                              |         | 0                  |        | LSB   |  |

|                                          | referred to AFE output              | Max DAC Code = 751111111                             |         | 1008               |        | 200   |  |

| Full Char                                | nnel Performance Specifications     |                                                      |         |                    |        |       |  |

| DNL                                      | Differential nonlinearity           |                                                      | -0.99   | 0.8 / -0.6         | 2.55   | LSB   |  |

| INL                                      | Integral nonlinearity               |                                                      | -73     | ±23                | 78     | LSB   |  |

|                                          |                                     |                                                      | 10      |                    | 10     | -00   |  |

# **Electrical Characteristics (continued)**

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 15 MHz,  $T_A$  = 25°C, unless otherwise specified.

| PARAMETER                    | TEST CONDITIONS  | MIN | TYP <sup>(1)</sup> | MAX | UNIT    |  |  |

|------------------------------|------------------|-----|--------------------|-----|---------|--|--|

|                              | Minimum DCA Cain |     | -79                |     | dB      |  |  |

|                              | Minimum PGA Gain |     | 7.2                |     | LSB RMS |  |  |

|                              |                  |     | -74                |     | dB      |  |  |

| Noise floor                  | PGA Gain = 1x    |     | 13                 | 30  | LSB RMS |  |  |

|                              | Mauimum DOA Cain |     | -56                |     | dB      |  |  |

|                              | Maximum PGA Gain |     | 104                |     | LSB RMS |  |  |

|                              | Mode 3           |     | 47                 |     | 1.00    |  |  |

| Channel-to-channel crosstalk | Mode 2           |     | 16                 |     | LSB     |  |  |

# 6.6 AC Timing Specifications

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L = 10 \text{ pF}$ , and  $f_{INCLK} = 15 \text{ MHz}$ ,  $T_A = 25^{\circ}C$ , unless otherwise specified.

|                   |                                                                       |                                            | MIN                 | TYP <sup>(1)</sup> | MAX    | UNIT             |  |

|-------------------|-----------------------------------------------------------------------|--------------------------------------------|---------------------|--------------------|--------|------------------|--|

| Input Clo         | ock Timing Specifications                                             |                                            |                     |                    |        |                  |  |

| finclk            | Input Clock Frequency                                                 | Mode 3, INCLK = PIXCLK (Pixel Rate Clock)  |                     |                    | 15     |                  |  |

|                   |                                                                       | Mode 2, INCLK = PIXCLK (Pixel Rate Clock)  |                     |                    | 22.5   | MHz              |  |

|                   |                                                                       | Mode 1, INCLK = PIXCLK (Pixel Rate Clock)  |                     |                    |        |                  |  |

|                   |                                                                       | Mode 3, INCLK = ADCCLK (ADC<br>Rate Clock) | 5                   |                    | 45     |                  |  |

|                   |                                                                       | Mode 2, INCLK = ADCCLK (ADC<br>Rate Clock) | 5                   |                    | 45     | MHz              |  |

|                   |                                                                       | Mode 1, INCLK = ADCCLK (ADC<br>Rate Clock) | 5                   |                    | 30     |                  |  |

| T <sub>dc</sub>   | Input Clock Duty Cycle                                                |                                            | 40/60%              | 50/50%             | 60/40% |                  |  |

| Full Cha          | nnel Latency Specifications                                           |                                            |                     |                    |        |                  |  |

|                   | SH out to first sampled pixel                                         | PIXPHASE0                                  |                     | 3                  |        |                  |  |

|                   | Figure 11 (Mode 3)                                                    | PIXPHASE1                                  | 3 3/7<br>4<br>4 3/7 |                    |        | T <sub>ADC</sub> |  |

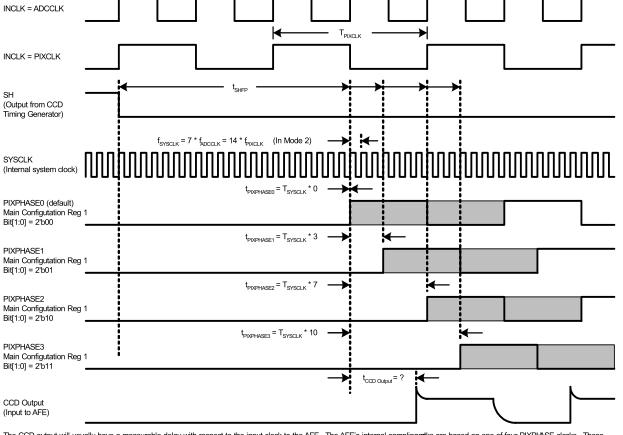

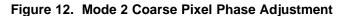

| t <sub>SHFP</sub> | Figure 12 (Mode 2)                                                    | PIXPHASE2                                  |                     |                    |        |                  |  |

|                   | Figure 13 (Mode 1)                                                    | PIXPHASE3                                  |                     |                    |        |                  |  |

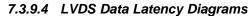

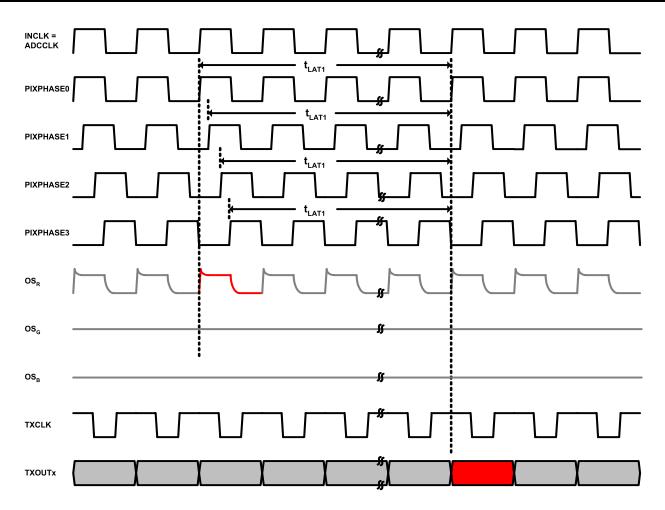

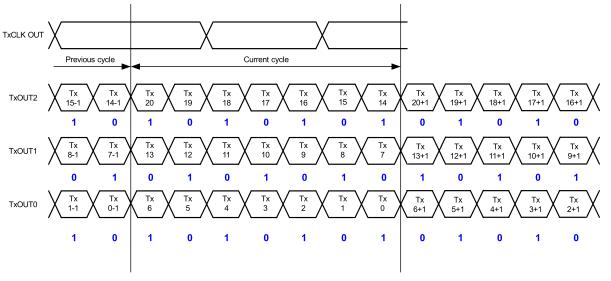

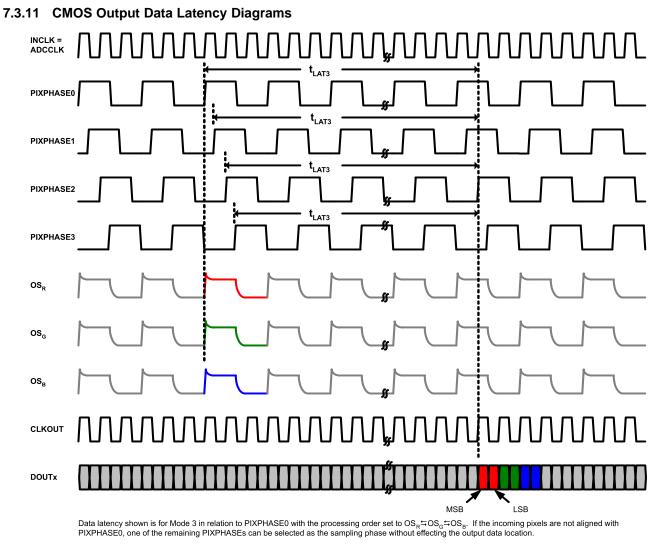

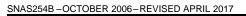

|                   | 3 channel mode pipeline delay<br>Figure 45 (LVDS)<br>Figure 50 (CMOS) | PIXPHASE0                                  |                     | 19                 |        |                  |  |

|                   |                                                                       | PIXPHASE1                                  |                     | 18 4/7             |        | -                |  |

| t <sub>LAT3</sub> |                                                                       | PIXPHASE2                                  |                     | 18                 |        | T <sub>ADC</sub> |  |

|                   |                                                                       | PIXPHASE3                                  |                     | 17 4/7             |        |                  |  |

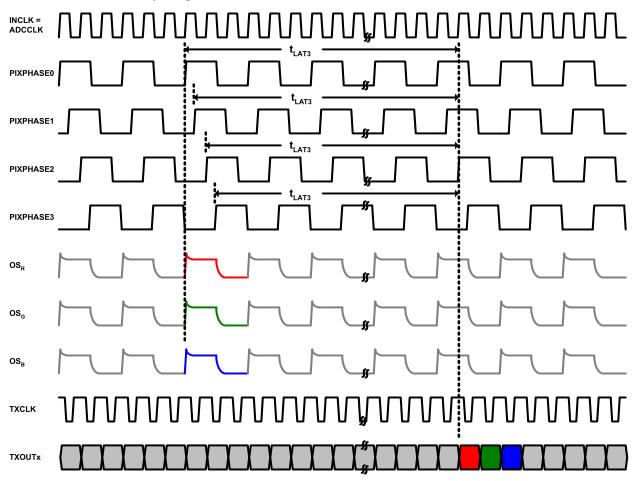

|                   | 2 channel mode pipeline delay<br>Figure 46 (LVDS)<br>Figure 51(CMOS)  | PIXPHASE0                                  |                     | 18                 |        |                  |  |

|                   |                                                                       | PIXPHASE1                                  |                     | 17 4/7             |        | -                |  |

| t <sub>LAT2</sub> |                                                                       | PIXPHASE2                                  |                     | 17                 |        | T <sub>ADC</sub> |  |

|                   |                                                                       | PIXPHASE3                                  |                     | 16 4/7             |        |                  |  |

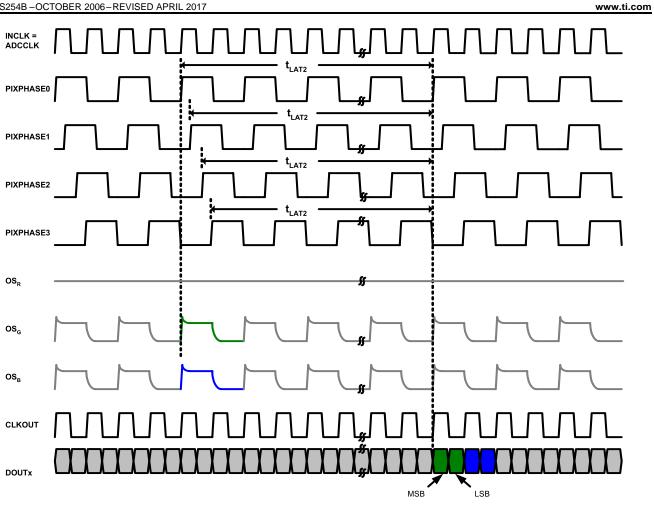

| t <sub>LAT1</sub> | 1 channel mode pipeline delay<br>Figure 47 (LVDS)<br>Figure 52(CMOS)  | PIXPHASE0                                  |                     | 16                 |        |                  |  |

|                   |                                                                       | PIXPHASE1                                  |                     | 15 4/7             |        | -                |  |

|                   |                                                                       | PIXPHASE2                                  |                     | 15                 |        | T <sub>ADC</sub> |  |

|                   |                                                                       | PIXPHASE3                                  |                     | 14 4/7             |        |                  |  |

(1) Typical figures are at  $T_A = 25^{\circ}$ C, and represent most likely parametric norms at the time of product characterization. The typical specifications are not ensured.

# AC Timing Specifications (continued)

The following specifications apply for VA = VD = VR = VC = 3.3 V,  $C_L$  = 10 pF, and  $f_{INCLK}$  = 15 MHz,  $T_A$  = 25°C, unless otherwise specified.

|                                         |                                                                        |                                                                              | MIN   | TYP <sup>(1)</sup> | MAX     | UNIT               |

|-----------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------|-------|--------------------|---------|--------------------|

|                                         | SH out to first valid data<br>(t <sub>SHFP</sub> + t <sub>LATx</sub> ) | Mode 3                                                                       |       | 22                 | 22      |                    |

| t <sub>SHFD</sub>                       |                                                                        | Mode 2                                                                       |       | 21                 |         | $T_{ADC}$          |

|                                         |                                                                        | Mode 1                                                                       |       | 19                 |         |                    |

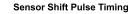

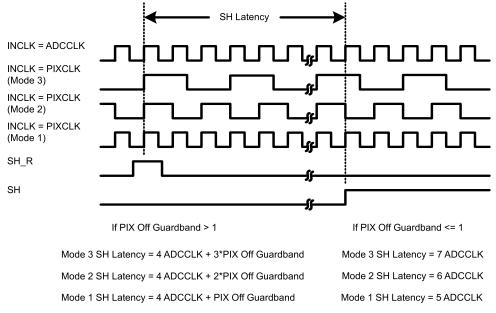

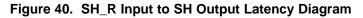

| SH_R Tir                                | ning Specifications (Figure 41)                                        |                                                                              |       |                    |         |                    |

| t <sub>SHR_S</sub>                      | SH_R setup time                                                        |                                                                              | 1.28  |                    |         | ns                 |

| t <sub>SHR_H</sub>                      | SH_R hold time                                                         |                                                                              | 2.25  |                    |         | ns                 |

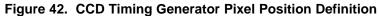

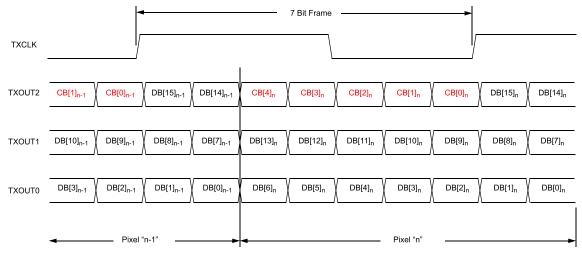

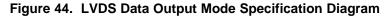

| LVDS Ou                                 | utput Timing Specifications (Figure 4                                  | 4)                                                                           |       |                    | i.      |                    |

| TX <sub>valid</sub>                     | TX output data valid window                                            | f <sub>INCLK</sub> = 45 MHz<br>INCLK = ADCCLK<br>(ADC Rate Clock)            | 2     |                    |         | ns                 |

| TX <sub>pp0</sub>                       | TXCLK to pulse position 0                                              |                                                                              |       | 0.013              |         | ns                 |

| TX <sub>pp1</sub>                       | TXCLK to pulse position 1                                              | LVDS Output                                                                  |       | 3.093              |         | ns                 |

| TX <sub>pp2</sub>                       | TXCLK to pulse position 2                                              | Specifications not tested in                                                 |       | 6.238              |         | ns                 |

| TX <sub>pp3</sub>                       | TXCLK to pulse position 3                                              | production.<br>Min/Max ensured by design,                                    |       | 9.613              |         | ns                 |

| TX <sub>pp4</sub>                       | TXCLK to pulse position 4                                              | characterization and statistical                                             |       | 12.663             |         | ns                 |

| TX <sub>pp5</sub>                       | TXCLK to pulse position 5                                              | analysis.                                                                    |       | 15.762             |         | ns                 |

| TX <sub>pp6</sub>                       | TXCLK to pulse position 6                                              |                                                                              |       | 18.982             |         | ns                 |

|                                         | utput Timing Specifications                                            | · ·                                                                          |       |                    |         |                    |

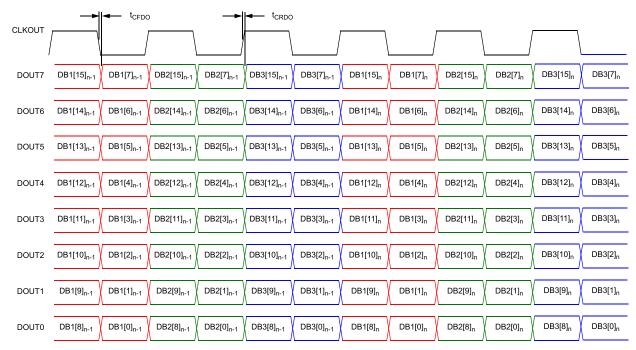

| t <sub>CRDO</sub>                       | CLKOUT rising edge to CMOS<br>output data                              | f <sub>INCLK</sub> = 45 MHz, INCLK = ADCCLK,<br>(ADC Rate Clock)             | -2.83 |                    | 2.7     | ns                 |

| t <sub>CFDO</sub>                       | CLKOUT Falling edge to CMOS output data                                | f <sub>INCLK</sub> = 45 MHz, INCLK = ADCCLK,<br>(ADC Rate Clock)             | -2.83 |                    | 2.7     | ns                 |

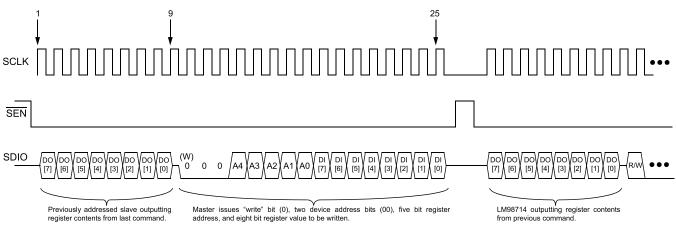

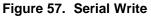

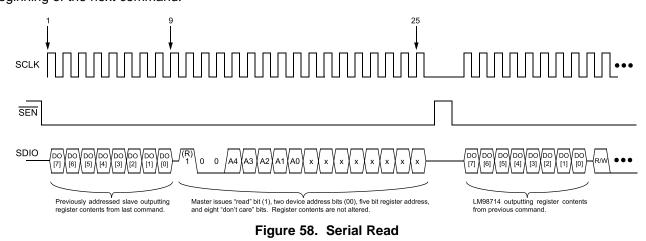

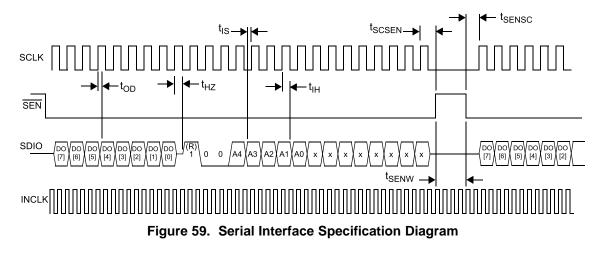

| Serial Int                              | erface Timing Specifications                                           | · · ·                                                                        |       |                    |         |                    |

| 4                                       |                                                                        | $f_{SCLK} \leq f_{INCLK}$ INCLK = PIXCLK (Pixel Rate Clock) Mode $3/2/1$     |       | 15/                | 22.5/30 | MHz                |

| f <sub>SCLK</sub> Input clock frequency | input clock nequency                                                   | $f_{SCLK} \le f_{INCLK}$<br>INCLK = ADCCLK<br>(ADC Rate Clock)<br>Mode 3/2/1 |       | 4                  | 5/45/30 | MHz                |

|                                         | SCLK duty cycle                                                        |                                                                              |       | 50/50              |         | ns                 |

| t <sub>IH</sub>                         | Input hold time                                                        |                                                                              | 1     |                    |         | ns                 |

| t <sub>IS</sub>                         | Input setup time                                                       |                                                                              | 4     |                    |         | ns                 |

| t <sub>SENSC</sub>                      | SCLK start time after SEN low                                          |                                                                              | 1.25  |                    |         | ns                 |

| t <sub>SCSEN</sub>                      | SEN high after last SCLK rising edge                                   |                                                                              | 2.82  |                    |         | ns                 |

| t <sub>SENW</sub>                       | SEN pulse width                                                        | INCLK must be active during serial interface commands.                       | 4     |                    |         | T <sub>INCLK</sub> |

| t <sub>OD</sub>                         | Output delay time                                                      |                                                                              |       | 11                 | 14.6    | ns                 |

| t <sub>HZ</sub>                         | Data output to High Z                                                  |                                                                              |       |                    | 0.5     | T <sub>SCLK</sub>  |

# 6.7 Typical Characteristics

TEXAS INSTRUMENTS

www.ti.com

# 7 Detailed Description

# 7.1 Overview

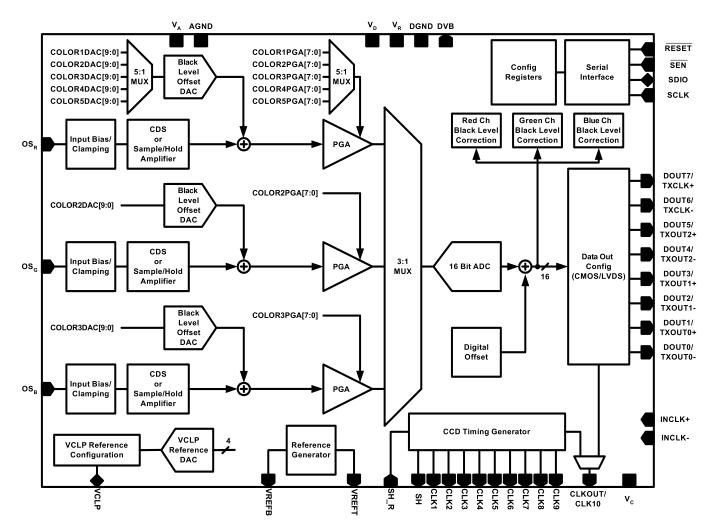

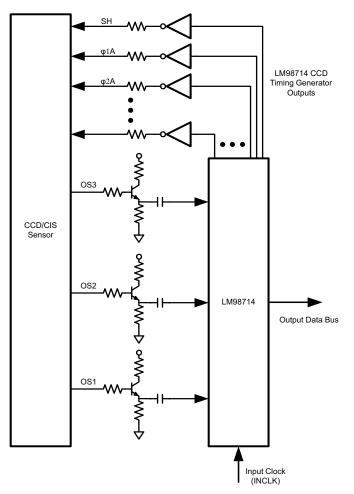

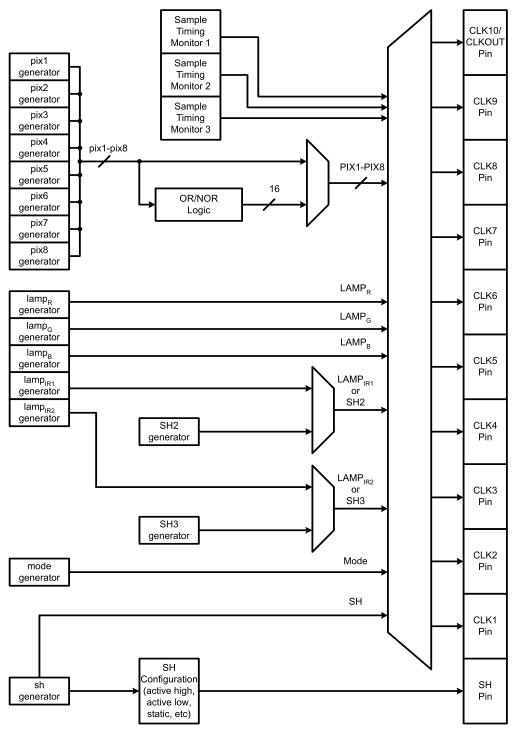

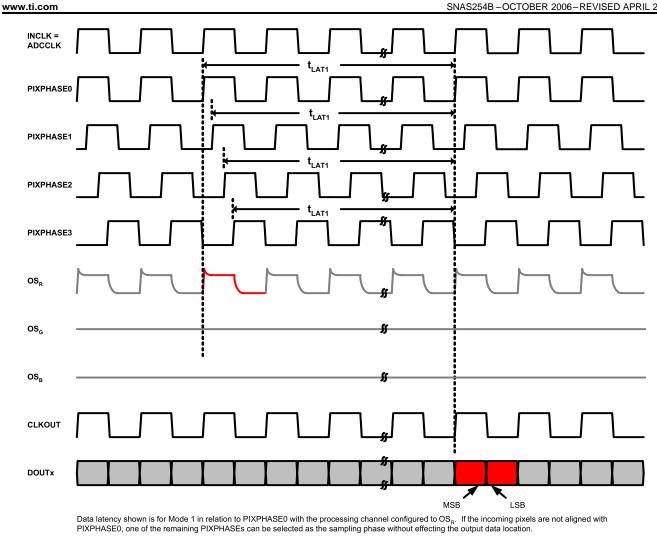

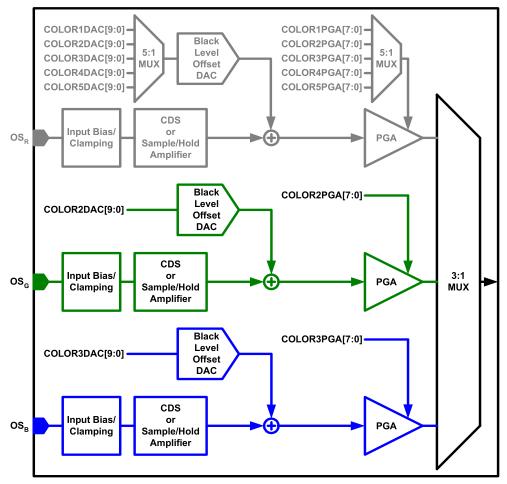

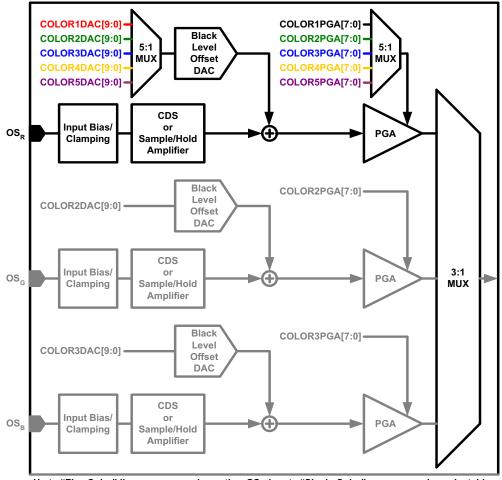

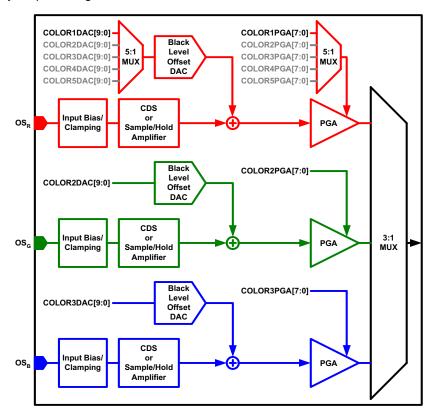

The LM98714 is a 16-bit, three-input, complete Analog Front End (AFE) for digital color copier and Multi-Function Peripheral (MFP) applications. The system block diagram of the LM98714, shown in Functional Block Diagram highlights the main features of the device. Each input has its own Input Bias and Clamping Network which are routed through a selectable Sample/Hold (S/H) or Correlated Double Sampler (CDS) amplifier. A ±9-Bit Offset DAC applies independent offset correction for each channel. A -3 to 17.9dB Programmable Gain Amplifier (PGA) applies independent gain correction for each channel. The LM98714 also provides independent Digital Black Level Correction Feedback Loops for each channel. The Black Level Correction Loop can be configured to run in Manual Mode (where the user inputs their own values of DAC offset) or in Automatic Mode where the LM98714 calculates each channel's Offset DAC value during optical black pixels and then adjusts the Offset register accordingly. The signals are routed to a single high performance 16-bit, 45 MHz analog-to-digital converter.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

# 7.3.1 Input Clock Introduction

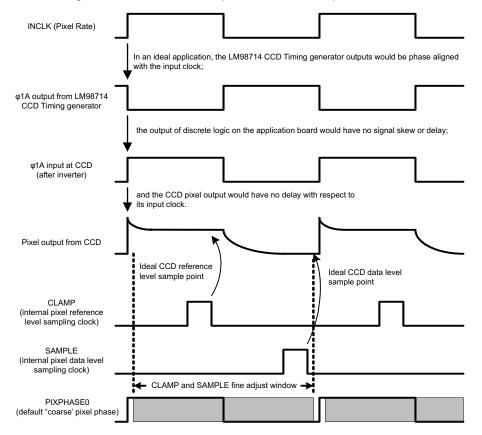

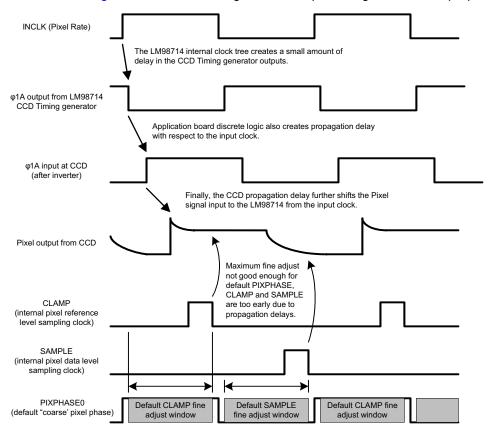

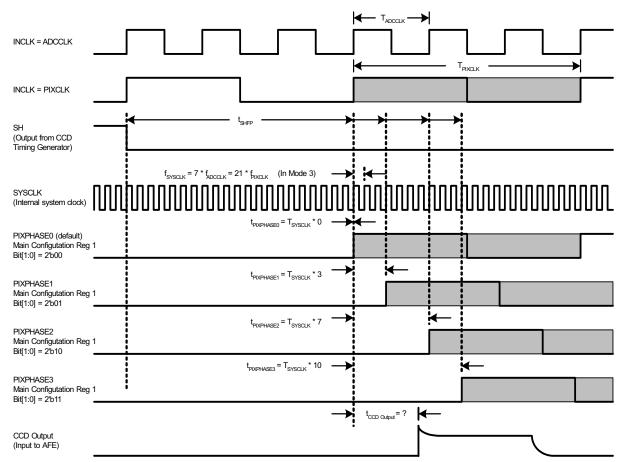

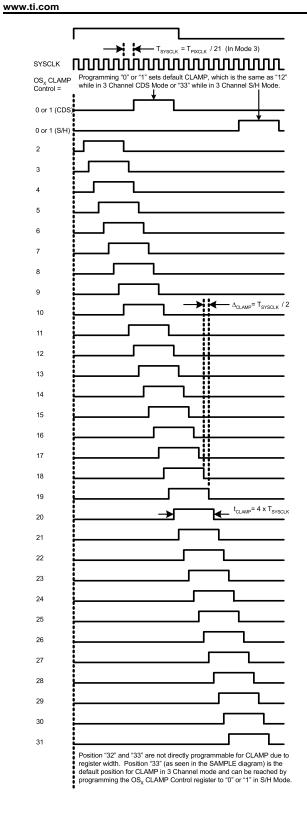

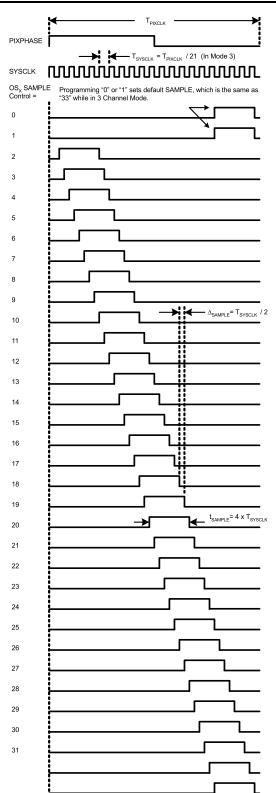

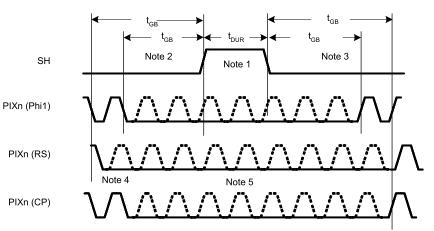

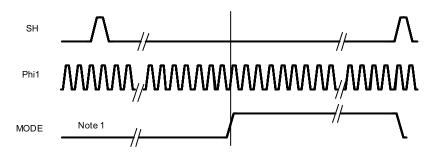

The clock input to the LM98714 can be a differential LVDS clock on the INCLK+ and INCLK- pins or a CMOS level clock applied to the INCLK+ pin with the INCLK- pin connected to DGND. The external clock signal format is auto sensed internally. In addition to the two available level formats, the input clock can be applied at the Pixel frequency (PIXCLK) or at the ADC frequency (ADCCLK). The LM98714 can perform internal clock multiplication when a Pixel frequency clock is applied, or no multiplication when an ADC frequency clock is applied. The internal configuration registers need to be written to perform the proper setup of the input clock. Table 1 shows the available input clock configurations for each operating mode.

| AFE Mode                     | Input Clock Type                                              | Internal<br>Multiplier | INCLK<br>Max Freq. | Configuration Register Settings                        |  |

|------------------------------|---------------------------------------------------------------|------------------------|--------------------|--------------------------------------------------------|--|

| INCLK = Pixel Freq. (PIXCLK) |                                                               | Зx                     | 15 MHz             | PIXCLK Configuration: Main Config Reg 1, Bit[2] = 1'b1 |  |

| Mode 3                       | INCLK = ADC Freq. (ADCCLK)                                    | 1x                     | 45 MHz             | ADCCLK Configuration: Main Config Reg 1, Bit[2] = 1'b0 |  |

| Mada 2                       | INCLK = Pixel Freq. (PIXCLK)                                  | 2x                     | 22.5 MHz           | PIXCLK Configuration: Main Config Reg 1, Bit[2] = 1'b1 |  |

| Mode 2                       | INCLK = ADC Freq. (ADCCLK)                                    | 1x                     | 45 MHz             | ADCCLK Configuration: Main Config Reg 1, Bit[2] = 1'b0 |  |

| Mode 1                       | INCLK = Pixel Freq. = ADC Freq<br>(ADCCLK = PIXCLK in Mode 1) | 1x                     | 30MHz              | Main Config Reg 1, Bit[2] = 1'bx                       |  |

# 7.3.2 Modes of Operation

The LM98714 can be configured to operate in several different operating modes. The following sections are a brief introduction to these modes of operation. A more rigorous explanation of the operating modes is contained in the Modes of Operation section. including input sampling diagrams for each mode as well as a description of the operating conditions.

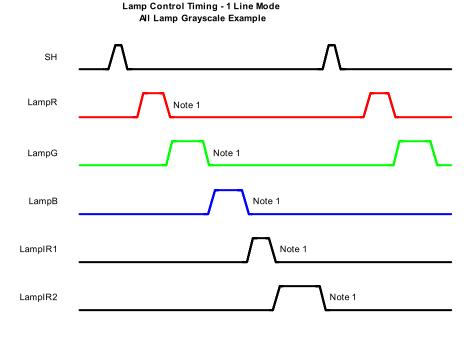

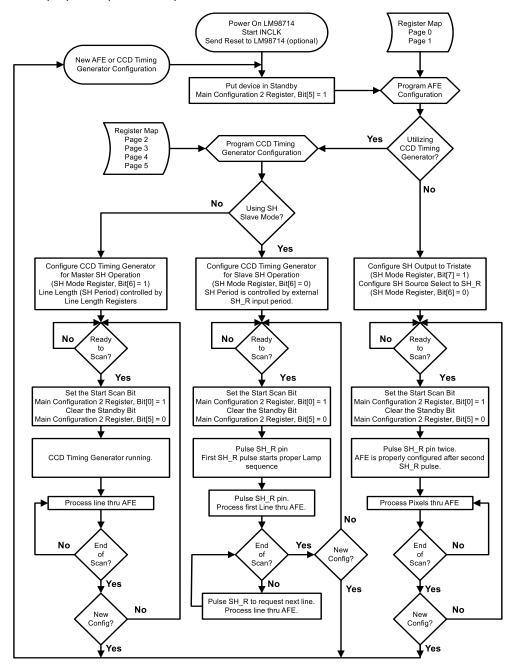

# 7.3.2.1 Mode 3 - Three Channel Input/Synchronous Pixel Sampling

$OS_B$ ,  $OS_G$ , and  $OS_R$  inputs are sampled synchronously at a pixel rate. The sampled signals are processed with each channel's offset and gain adjusted independently via the control registers. The order in which pixels are processed from the input to the ADC is fully programmable and is synchronized by the SH pulse. In this mode, the maximum channel speed is 15MSPS per channel with the ADC running at 45MSPS yielding a three color throughput of 45MSPS.

# 7.3.2.2 Mode 2 - Two Channel Input/Synchronous Pixel Sampling

Mode 2 is useful for CCD sensors with a Black and White mode with Even and Odd outputs. In its default configuration, Mode 2 samples the Even output via the  $OS_B$  channel input, and the Odd output via the  $OS_G$  channel input. Sampling of the Even and Odd pixels is performed synchronously at a maximum sample rate of 22.5MSPS per input with the ADC running at 45MSPS.

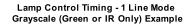

# 7.3.2.3 Mode 1a - One Channel Input/One, Two, Three, Four, or Five Color Sequential Line Sampling

In Mode 1a, all pixels are processed through a single input  $(OS_R, OS_G, or OS_B)$  chosen through the control register setup. This mode is useful in applications where only one input channel is used. The selected input is programmable through the control register. If more than one color is being sent to the input, the user can configure the  $OS_R$  channel to utilize up to five offset and gain coefficients for up to five different lines of color pixels. The SH pulse at the beginning of each line sequences the DAC and PGA coefficients as configured in the control registers. In this mode, the maximum channel speed is 30MSPS per channel with the ADC running at 30MSPS.

# 7.3.2.4 Mode 1b - One Channel Input Per Line/Sequential Line (Input) Sampling/Three Channel Processing

In Mode 1b the  $OS_R$ ,  $OS_G$ , and  $OS_B$  inputs are sampled one input per line with the input selection being sequenced to the next color by an SH pulse. This mode is useful with sensors that output whole lines of pixels of a single color. The order in which the inputs are sampled is fully programmable. Sequencing from one channel to the next is triggered by the SH pulse. The first SH pulse after this mode is set (or reset) sets up the first programmed input for gain and offset and initiates sampling through that input alone. The next SH pulse switches the active input to the second channel indicated by the configuration registers. This sequencing with SH pulses continues to the third input and then continuously loops through the inputs. In this mode, the maximum channel speed is 30MSPS per channel with the ADC running at 30MSPS.

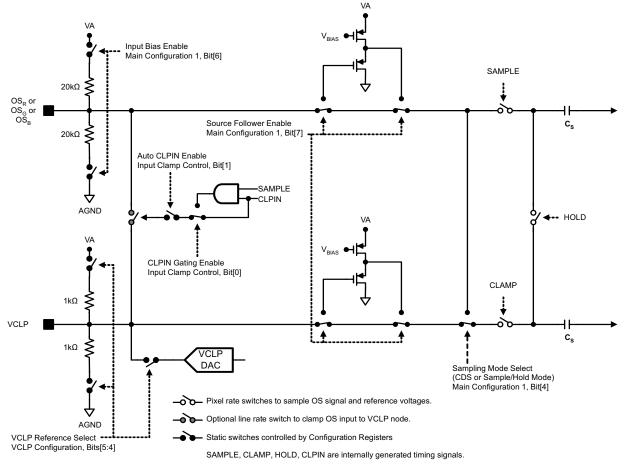

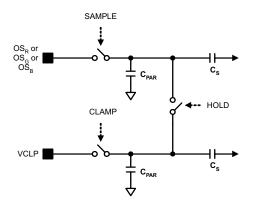

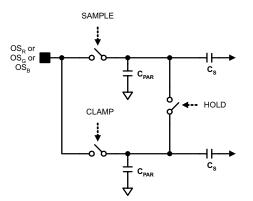

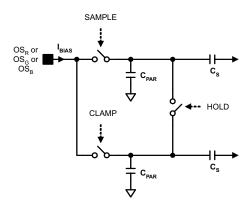

# 7.3.3 Input Bias and Clamping

Figure 2. Input Bias and Clamping Diagram

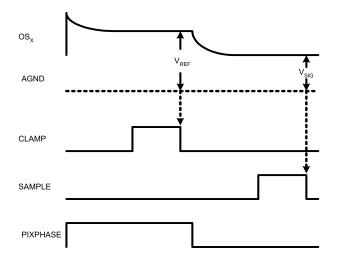

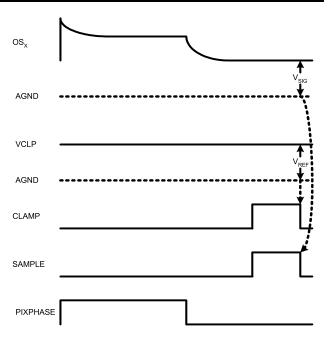

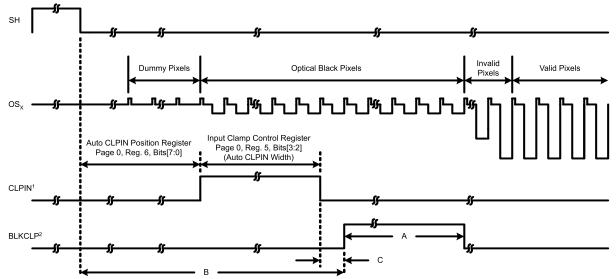

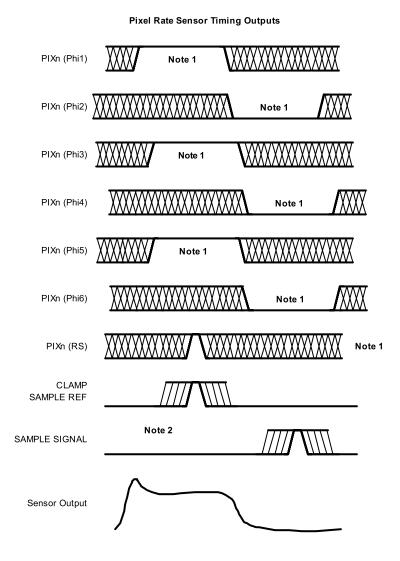

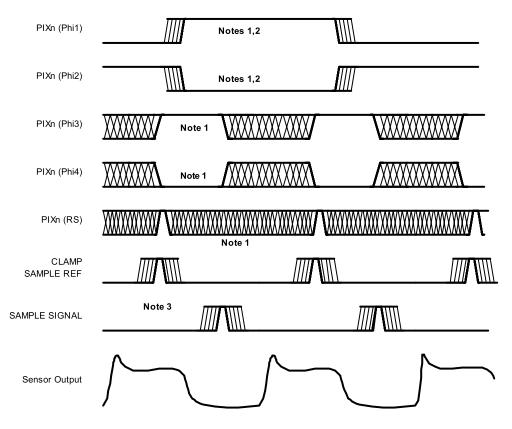

The inputs to the LM98714 are typically AC coupled through a film capacitor and can be sampled in either Sample and Hold Mode (S/H Mode) or Correlated Double Sampling Mode (CDS Mode). In either mode, the DC bias point for the LM98714 side of the AC coupling capacitor is set using the circuit of Figure 2 which can be configured to operate in a variety of different modes.

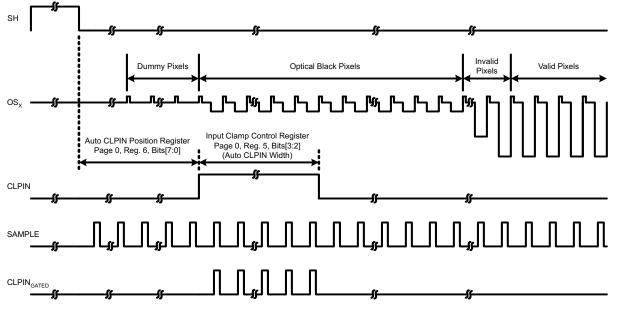

A typical CCD waveform is shown in Figure 3. Also shown in Figure 3 is an internal signal "SAMPLE" which can be used to "gate" the CLPIN signal so that it only occurs during the "signal" portion of the CCD pixel waveform.

Figure 3. Typical CCD Waveform and LM98714 Input Clamp Signal (CLPIN)

Figure 4. Sample and Hold Mode Simplified Input Diagram

Proper DC biasing of the CCD waveform in Sample and Hold mode is critical for realizing optimal operating conditions. In Sample/Hold mode, the Signal Level of the CCD waveform is compared to the DC voltage on the VCLP pin. In order to fully utilize the range of the input circuitry, it is desirable to cause the Black Level signal voltage to be as close to the VCLP voltage as possible, resulting in a near zero scale output for Black Level pixels.

In Sample/Hold Mode, the DC bias point of the input pin is typically set by actuating the input clamp switch (see Figure 2) during optical black pixels which connects the input pins to the VCLP pin DC voltage. The signal controlling this switch is an auto-generated pulse, CLPIN. CLPIN is generated with a programmable pixel delay with respect to SH and a programmable pixel width. These parameters are available through the serial interface control registers.

Actuating the input clamp will force the average value of the CCD waveform to be centered around the VCLP DC voltage. During Optical Black Pixels, the CCD output has roughly three components. The first component of the pixel is a "Reset Noise" peak followed by the Reset (or Pedestal) Level voltage, then finally the Black Level voltage signal. Taking the average of these signal components will result in a final "clamped" DC bias point that is close to the Black Level signal voltage.

**NSTRUMENTS**

**EXAS**

To provide a more precise DC bias point (i.e. a voltage closer to the Black Level voltage), the CLPIN pulse can be "gated" by the internally generated SAMPLE clock. This resulting CLPIN<sub>GATED</sub> signal is the logical "AND" of the SAMPLE and CLPIN signals as shown in Figure 3. By using the CLPIN<sub>GATED</sub> signal, the higher Reset Noise peak will not be included in the clamping period and only the average of the Reset Level and Black Level components of the CCD waveform will be centered around VCLP.

Figure 5. Equivalent Input Switched Capacitance S/H Mode

In Sample and Hold Mode, the impedance of the analog input pins is dominated by the switched capacitance of the CDS/Sample and Hold amplifier. The amplifier switched capacitance, shown as  $C_S$  in Figure 4, and internal parasitic capacitances can be estimated by a single capacitor switched between the analog input and the VCLP reference pin for Sample and Hold mode. During each pixel cycle, the modeled capacitor,  $C_{SH}$ , is charged to the OS<sub>X</sub>-VCLP voltage then discharged. The average input current at the OS<sub>X</sub> pin can be calculated knowing the input signal amplitude and the frequency of the pixel. If the application requires AC coupling of the CCD output to the LM98714 analog inputs, the Sample and Hold Mode input bias current may degrade the DC bias point of the coupling capacitor. To overcome this, Input Source Follower Buffers are available to isolate the larger Sample and Hold Mode input bias current is much lower for CDS mode, eliminating the need for the source follower buffers.

# 7.3.3.1 CDS Mode

Figure 6. CDS Mode Simplified Input Diagram

Correlated Double Sampling mode does not require as precise a DC bias point as does Sample and Hold mode. This is due mainly to the nature of CDS itself, that is, the Video Signal voltage is referenced to the Reset Level voltage instead of the static DC VCLP voltage. The common mode voltage of these two points on the CCD waveform have little bearing on the resulting differential result. However, the DC bias point does need to be established to ensure the CCD waveform's common mode voltage is within rated operating ranges.

The CDS mode biasing can be performed in the same way as described in the Sample/Hold Mode Biasing section, or, an alternative method is available which precludes the need for a CLPIN pulse. Internal resistor dividers can be switched in across the  $OS_R$ ,  $OS_G$ , and/or  $OS_B$  inputs to provide the DC bias voltage.

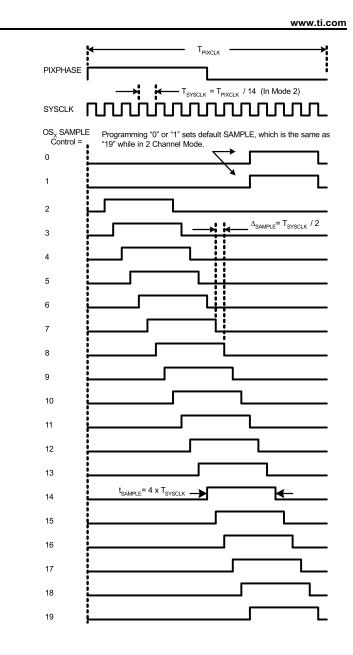

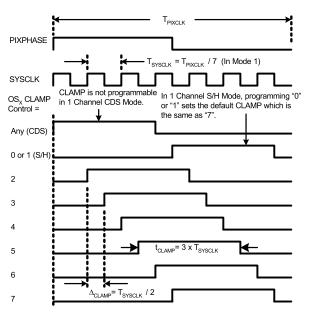

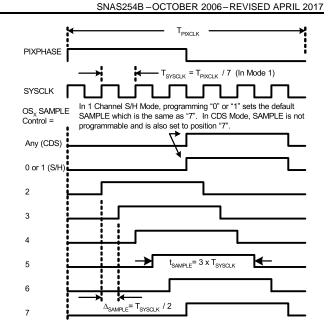

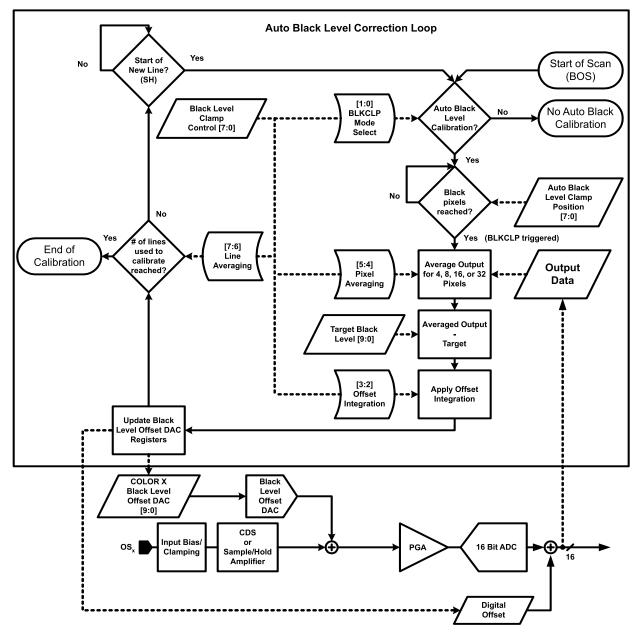

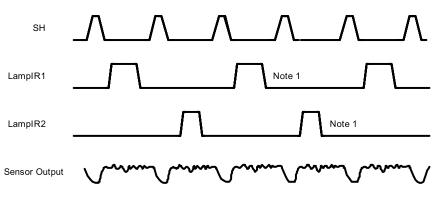

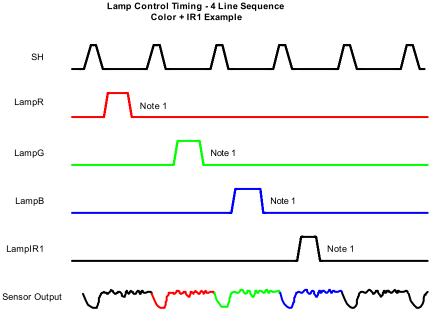

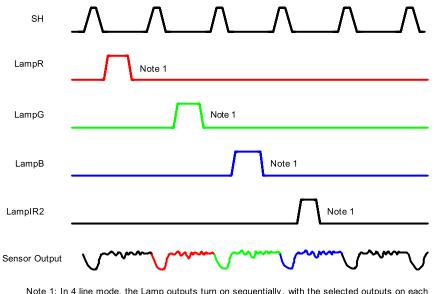

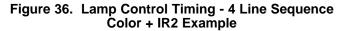

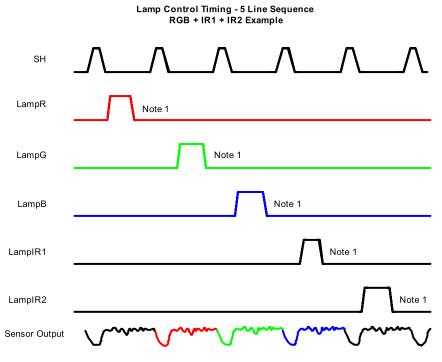

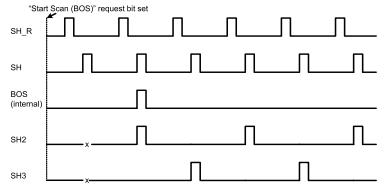

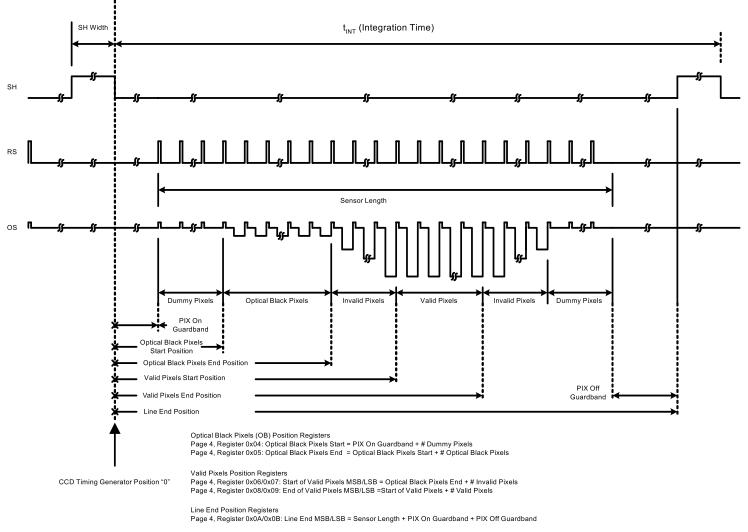

Figure 7. CDS Mode Input Bias Current