# onsemi

MARKING

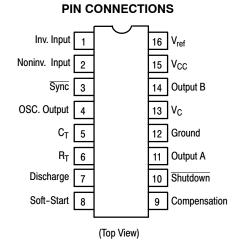

DIAGRAMS

## Pulse Width Modulator Control Circuit

## SG3525A

The SG3525A pulse width modulator control circuit offers improved performance and lower external parts count when implemented for controlling all types of switching power supplies. The on-chip +5.1 V reference is trimmed to  $\pm 1\%$  and the error amplifier has an input common-mode voltage range that includes the reference voltage, thus eliminating the need for external divider resistors. A sync input to the oscillator enables multiple units to be slaved or a single unit to be synchronized to an external system clock. A wide range of deadtime can be programmed by a single resistor connected between the C<sub>T</sub> and Discharge pins. This device also features built-in soft-start circuitry, requiring only an external timing capacitor. A shutdown pin controls both the soft-start circuitry and the output stages, providing instantaneous turn off through the PWM latch with pulsed shutdown, as well as soft-start recycle with longer shutdown commands. The under voltage lockout inhibits the outputs and the changing of the soft-start capacitor when V<sub>CC</sub> is below nominal. The output stages are totem-pole design capable of sinking and sourcing in excess of 200 mA. The output stage of the SG3525A features NOR logic resulting in a low output for an off-state.

#### Features

- 8.0 V to 35 V Operation

- 5.1 V  $\pm$  1.0% Trimmed Reference

- 100 Hz to 400 kHz Oscillator Range

- Separate Oscillator Sync Pin

- Adjustable Deadtime Control

- Input Undervoltage Lockout

- Latching PWM to Prevent Multiple Pulses

- Pulse-by-Pulse Shutdown

- Dual Source/Sink Outputs: ±400 mA Peak

- Pb-Free Packages are Available\*

#### 16 SG3525AN PDIP-16 ° AWLYYWW **N SUFFIX** ʹϼϼϼϼϼϼϼϥ CASE 648-08 SOIC-16 WB SG3525A **DW SUFFIX** AWLYYWW CASE 751G = Assembly Location WL = Wafer Lot YY = Year WW = Work Week

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

\*For additional information on our Pb–Free strategy and soldering details, please download the **onsemi** Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

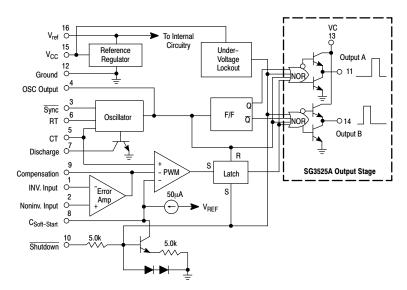

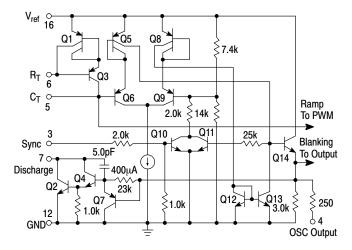

Figure 1. Representative Block Diagram

#### **ORDERING INFORMATION**

| Device       | Package                 | Shipping <sup>†</sup> |

|--------------|-------------------------|-----------------------|

| SG3525ANG    | PDIP-16<br>(Pb-Free)    | 25 Units / Rail       |

| SG3525ADWR2G | SOIC-16 WB<br>(Pb-Free) | 1000 Tape & Reel      |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, <u>BRD8011/D</u>.

#### MAXIMUM RATINGS

| Rating                                                                              | Symbol              | Value                   | Unit |

|-------------------------------------------------------------------------------------|---------------------|-------------------------|------|

| Supply Voltage                                                                      | V <sub>CC</sub>     | +40                     | Vdc  |

| Collector Supply Voltage                                                            | V <sub>C</sub>      | +40                     | Vdc  |

| Logic Inputs                                                                        |                     | -0.3 to +5.5            | V    |

| Analog Inputs                                                                       |                     | -0.3 to V <sub>CC</sub> | V    |

| Output Current, Source or Sink                                                      | ۱ <sub>0</sub>      | ±500                    | mA   |

| Reference Output Current                                                            | I <sub>ref</sub>    | 50                      | mA   |

| Oscillator Charging Current                                                         |                     | 5.0                     | mA   |

| Power Dissipation<br>$T_A = +25^{\circ}C$ (Note 1)<br>$T_C = +25^{\circ}C$ (Note 2) | PD                  | 1000<br>2000            | mW   |

| Thermal Resistance, Junction-to-Air                                                 | R <sub>θJA</sub>    | 100                     | °C/W |

| Thermal Resistance, Junction-to-Case                                                | R <sub>θJC</sub>    | 60                      | °C/W |

| Operating Junction Temperature                                                      | TJ                  | +150                    | °C   |

| Storage Temperature Range                                                           | T <sub>stg</sub>    | -55 to +125             | °C   |

| Lead Temperature (Soldering, 10 seconds)                                            | T <sub>Solder</sub> | +300                    | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Derate at 10 mW/°C for ambient temperatures above +50°C.

2. Derate at 16 mW/°C for case temperatures above +25°C.

#### **RECOMMENDED OPERATING CONDITIONS**

| Characteristics                                        | Symbol           | Min    | Max          | Unit |

|--------------------------------------------------------|------------------|--------|--------------|------|

| Supply Voltage                                         | V <sub>CC</sub>  | 8.0    | 35           | Vdc  |

| Collector Supply Voltage                               | V <sub>C</sub>   | 4.5    | 35           | Vdc  |

| Output Sink/Source Current<br>(Steady State)<br>(Peak) | IO               | 0<br>0 | ±100<br>±400 | mA   |

| Reference Load Current                                 | I <sub>ref</sub> | 0      | 20           | mA   |

| Oscillator Frequency Range                             | f <sub>osc</sub> | 0.1    | 400          | kHz  |

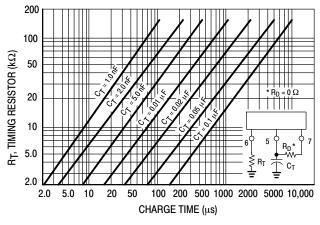

| Oscillator Timing Resistor                             | R <sub>T</sub>   | 2.0    | 150          | kΩ   |

| Oscillator Timing Capacitor                            | C <sub>T</sub>   | 0.001  | 0.2          | μF   |

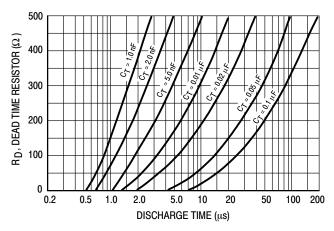

| Deadtime Resistor Range                                | R <sub>D</sub>   | 0      | 500          | Ω    |

| Operating Ambient Temperature Range                    | T <sub>A</sub>   | 0      | +70          | °C   |

#### **APPLICATION INFORMATION**

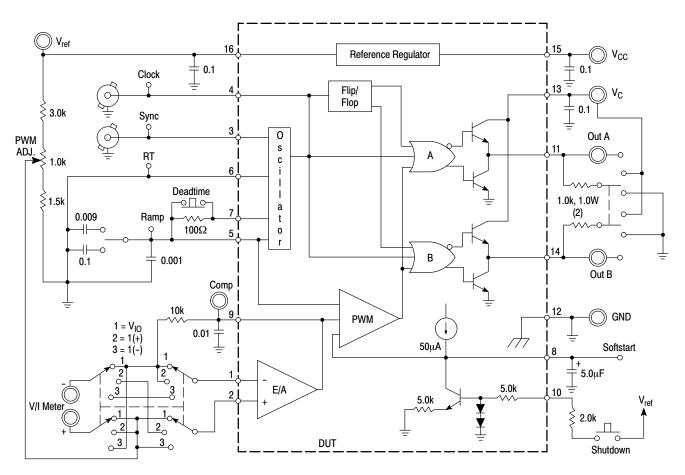

#### Shutdown Options (See Block Diagram, page 2)

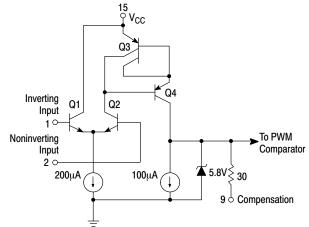

Since both the compensation and soft-start terminals (Pins 9 and 8) have current source pull-ups, either can readily accept a pull-down signal which only has to sink a maximum of 100  $\mu$ A to turn off the outputs. This is subject to the added requirement of discharging whatever external capacitance may be attached to these pins.

An alternate approach is the use of the shutdown circuitry of Pin 10 which has been improved to enhance the available shutdown options. Activating this circuit by applying a positive signal on Pin 10 performs two functions: the PWM latch is immediately set providing the fastest turn–off signal to the outputs; and a 150  $\mu$ A current sink begins to discharge the external soft–start capacitor. If the shutdown command is short, the PWM signal is terminated without significant discharge of the soft–start capacitor, thus, allowing, for example, a convenient implementation of pulse–by–pulse current limiting. Holding Pin 10 high for a longer duration, however, will ultimately discharge this external capacitor, recycling slow turn–on upon release.

Pin 10 should not be left floating as noise pickup could conceivably interrupt normal operation.

| Characteristics                                                               | Symbol                           | Min  | Тур  | Max  | Unit          |

|-------------------------------------------------------------------------------|----------------------------------|------|------|------|---------------|

| REFERENCE SECTION                                                             | •                                | •    |      | •    |               |

| Reference Output Voltage ( $T_J = +25^{\circ}C$ )                             | V <sub>ref</sub>                 | 5.00 | 5.10 | 5.20 | Vdc           |

| Line Regulation (+8.0 V $\leq$ V <sub>CC</sub> $\leq$ +35 V)                  | Reg <sub>line</sub>              | -    | 10   | 20   | mV            |

| Load Regulation (0 mA $\leq$ I <sub>L</sub> $\leq$ 20 mA)                     | Reg <sub>load</sub>              | -    | 20   | 50   | mV            |

| Temperature Stability                                                         | $\Delta V_{ref} / \Delta T$      | -    | 20   | -    | mV            |

| Total Output Variation Includes Line and Load Regulation over Temperature     | $\Delta V_{ref}$                 | 4.95 | -    | 5.25 | Vdc           |

| Short Circuit Current ( $V_{ref} = 0 V$ , $T_J = +25^{\circ}C$ )              | I <sub>SC</sub>                  | -    | 80   | 100  | mA            |

| Output Noise Voltage (10 Hz $\leq$ f $\leq$ 10 kHz, T <sub>J</sub> = +25°C)   | Vn                               | -    | 40   | 200  | $\mu V_{rms}$ |

| Long Term Stability ( $T_J = +125^{\circ}C$ ) (Note 4)                        | S                                | -    | 20   | 50   | mV/khi        |

| OSCILLATOR SECTION (Note 5, unless otherwise noted.)                          |                                  |      |      |      | -             |

| Initial Accuracy ( $T_J = +25^{\circ}C$ )                                     |                                  | -    | ±2.0 | ±6.0 | %             |

| Frequency Stability with Voltage (+8.0 V $\leq$ V <sub>CC</sub> $\leq$ +35 V) | $\frac{\Delta f_{OSC}}{D_{VCC}}$ | -    | ±1.0 | ±2.0 | %             |

| Frequency Stability with Temperature                                          | $\frac{\Delta f_{OSC}}{DT}$      | -    | ±0.3 | -    | %             |

| Minimum Frequency ( $R_T$ = 150 k $\Omega$ , $C_T$ = 0.2 $\mu$ F)             | f <sub>min</sub>                 | -    | 50   | -    | Hz            |

| Maximum Frequency ( $R_T$ = 2.0 k $\Omega$ , $C_T$ = 1.0 nF)                  | f <sub>max</sub>                 | 400  | -    | -    | kHz           |

| Current Mirror (I <sub>RT</sub> = 2.0 mA)                                     |                                  | 1.7  | 2.0  | 2.2  | mA            |

| Clock Amplitude                                                               |                                  | 3.0  | 3.5  | -    | V             |

| Clock Width (T <sub>J</sub> = +25°C)                                          |                                  | 0.3  | 0.5  | 1.0  | μs            |

| Sync Threshold                                                                |                                  | 1.2  | 2.0  | 2.8  | V             |

| Sync Input Current (Sync Voltage = +3.5 V)                                    |                                  | -    | 1.0  | 2.5  | mA            |

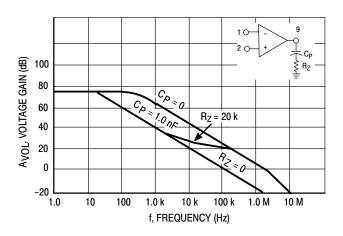

| ERROR AMPLIFIER SECTION (V <sub>CM</sub> = +5.1 V)                            |                                  |      |      |      |               |

| Input Offset Voltage                                                          | V <sub>IO</sub>                  | -    | 2.0  | 10   | mV            |

| Input Bias Current                                                            | I <sub>IB</sub>                  | -    | 1.0  | 10   | μA            |

| Input Offset Current                                                          | I <sub>IO</sub>                  | -    | -    | 1.0  | μA            |

| DC Open Loop Gain ( $R_L \ge 10 M\Omega$ )                                    | A <sub>VOL</sub>                 | 60   | 75   | -    | dB            |

| Low Level Output Voltage                                                      | V <sub>OL</sub>                  | -    | 0.2  | 0.5  | V             |

| High Level Output Voltage                                                     | V <sub>OH</sub>                  | 3.8  | 5.6  | -    | V             |

| Common Mode Rejection Ratio (+1.5 V $\leq$ V_{CM} $\leq$ +5.2 V)              | CMRR                             | 60   | 75   | -    | dB            |

| Power Supply Rejection Ratio (+8.0 V $\leq$ V_{CC} $\leq$ +35 V)              | PSRR                             | 50   | 60   | -    | dB            |

| PWM COMPARATOR SECTION                                                        |                                  |      |      |      |               |

| Minimum Duty Cycle                                                            | DC <sub>min</sub>                | -    | -    | 0    | %             |

| Maximum Duty Cycle                                                            | DC <sub>max</sub>                | 45   | 49   | _    | %             |

| Input Threshold, Zero Duty Cycle (Note 5)                                     | V <sub>th</sub>                  | 0.6  | 0.9  | -    | V             |

| Input Threshold, Maximum Duty Cycle (Note 5)                                  | V <sub>th</sub>                  | -    | 3.3  | 3.6  | V             |

| Input Bias Current                                                            | I <sub>IB</sub>                  | -    | 0.05 | 1.0  | μA            |

T<sub>low</sub> = 0° T<sub>high</sub> = +70°C

Since long term stability cannot be measured on each device before shipment, this specification is an engineering estimate of average stability from lot to lot.

Tested at f<sub>osc</sub> = 40 kHz (R<sub>T</sub> = 3.6 kΩ, C<sub>T</sub> = 0.01 μF, R<sub>D</sub> = 0 Ω).

#### ELECTRICAL CHARACTERISTICS (continued)

| Characteristics                                                                       | Symbol               | Min      | Тур        | Max        | Unit |

|---------------------------------------------------------------------------------------|----------------------|----------|------------|------------|------|

| SOFT-START SECTION                                                                    |                      |          |            | -          | -    |

| Soft-Start Current (V <sub>shutdown</sub> = 0 V)                                      |                      | 25       | 50         | 80         | μΑ   |

| Soft-Start Voltage (V <sub>shutdown</sub> = 2.0 V)                                    |                      | -        | 0.4        | 0.6        | V    |

| Shutdown Input Current (V <sub>shutdown</sub> = 2.5 V)                                |                      | -        | 0.4        | 1.0        | mA   |

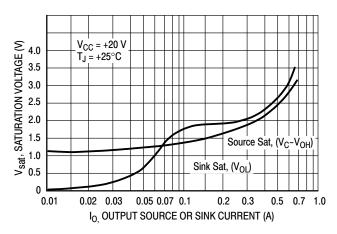

| OUTPUT DRIVERS (Each Output, V <sub>CC</sub> = +20 V)                                 |                      |          |            | -          | -    |

| Output Low Level<br>(I <sub>sink</sub> = 20 mA)<br>(I <sub>sink</sub> = 100 mA)       | V <sub>OL</sub>      |          | 0.2<br>1.0 | 0.4<br>2.0 | V    |

| Output High Level<br>(I <sub>source</sub> = 20 mA)<br>(I <sub>source</sub> = 100 mA)  | V <sub>OH</sub>      | 18<br>17 | 19<br>18   |            | V    |

| Under Voltage Lockout (V8 and V9 = High)                                              | V <sub>UL</sub>      | 6.0      | 7.0        | 8.0        | V    |

| Collector Leakage, V <sub>C</sub> = +35 V (Note 6)                                    | I <sub>C(leak)</sub> | -        | -          | 200        | μΑ   |

| Rise Time (C <sub>L</sub> = 1.0 nF, T <sub>J</sub> = $25^{\circ}$ C)                  | t <sub>r</sub>       | -        | 100        | 600        | ns   |

| Fall Time (C <sub>L</sub> = 1.0 nF, T <sub>J</sub> = 25°C)                            | t <sub>f</sub>       | -        | 50         | 300        | ns   |

| Shutdown Delay (V <sub>DS</sub> = +3.0 V, C <sub>S</sub> = 0, T <sub>J</sub> = +25°C) | t <sub>ds</sub>      | -        | 0.2        | 0.5        | μs   |

| Supply Current (V <sub>CC</sub> = +35 V)                                              | Icc                  | -        | 14         | 20         | mA   |

6. Applies to SG3525A only, due to polarity of output pulses.

Figure 3. Oscillator Charge Time versus R<sub>T</sub>

Figure 4. Oscillator Discharge Time versus R<sub>D</sub>

Figure 6. Output Saturation Characteristics

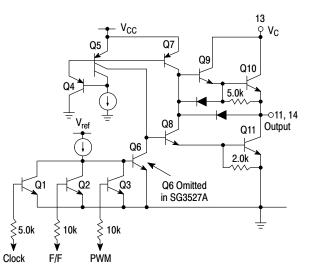

Figure 7. Oscillator Schematic

Figure 9. Output Circuit (1/2 Circuit Shown)

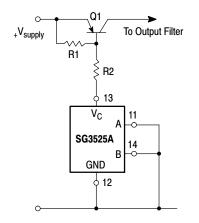

For single-ended supplies, the driver outputs are grounded. The  $V_C$  terminal is switched to ground by the totem-pole source transistors on alternate oscillator cycles.

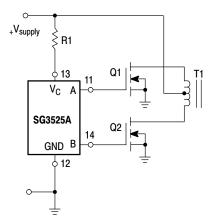

#### Figure 10. Single-Ended Supply

The low source impedance of the output drivers provides rapid charging of power FET input capacitance while minimizing external components.

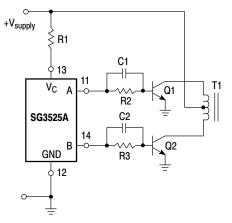

#### Figure 12. Driving Power FETS

In conventional push-pull bipolar designs, forward base drive is controlled by R1-R3. Rapid turn-off times for the power devices are achieved with speed-up capacitors C1 and C2.

#### Figure 11. Push–Pull Configuration

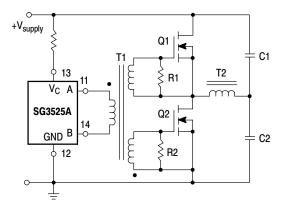

Low power transformers can be driven directly by the SG3525A. Automatic reset occurs during deadtime, when both ends of the primary winding are switched to ground.

# Figure 13. Driving Transformers in a Half–Bridge Configuration

🕀 0.010 🕅 C A 🕅 B 🕅

STYLE 1: STYLE 2: PIN 1. COMMON DRAIN CATHODE CATHODE PIN 1. 2. 2. з. CATHODE 3. COMMON DRAIN COMMON DRAIN 4. 5. CATHODE 4. CATHODE 5. 6. CATHODE 6. COMMON DRAIN 7. CATHODE 7. COMMON DRAIN CATHODE COMMON DRAIN 8. 9. 8. 9. ANODE GATE 10. ANODE 10. SOURCE ANODE ANODE 11. 12. GATE SOURCE 11. 12. 13. ANODE 13. GATE 14. 15. ANODE ANODE 14. 15. SOURCE GATE 16. ANODE 16. SOURCE

SIDE VIEW

NOTE 6

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2

- 3.

- DIMENSIONING AND TOLERANGURA PER ASIME 114.300, 1994. CONTROLLING DIMENSION: INCHES. DIMENSIONS A, A1 AND L ARE MEASURED WITH THE PACK-AGE SEATED IN JEDEC SEATING PLANE GAUGE GS-3. DIMENSIONS D, D1 AND E1 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS ARE NOT TO EXCEED 0.10 INCH. 4.

- DIMENSION E IS MEASURED AT A POINT 0.015 BELOW DATUM PLANE H WITH THE LEADS CONSTRAINED PERPENDICULAR 5. TO DATUM C.

- DIMENSION 6B IS MEASURED AT THE LEAD TIPS WITH THE LEADS UNCONSTRAINED. DATUM PLANE H IS COINCIDENT WITH THE BOTTOM OF THE 6.

- 7

- LEADS, WHERE THE LEADS EXIT THE BODY. PACKAGE CONTOUR IS OPTIONAL (ROUNDED OR SQUARE 8 CORNERS).

|     | INC    |           | MILLIM   | ETEDS |

|-----|--------|-----------|----------|-------|

| DIM |        |           | MIN      | MAX   |

|     | IVITIN |           | IVITIN   |       |

| Α   |        | 0.210     |          | 5.33  |

| A1  | 0.015  |           | 0.38     |       |

| A2  | 0.115  | 0.195     | 2.92     | 4.95  |

| b   | 0.014  | 0.022     | 0.35     | 0.56  |

| b2  | 0.060  | 0.060 TYP |          | TYP   |

| С   | 0.008  | 0.014     | 0.20     | 0.36  |

| D   | 0.735  | 0.775     | 18.67    | 19.69 |

| D1  | 0.005  |           | 0.13     |       |

| Е   | 0.300  | 0.325     | 7.62     | 8.26  |

| E1  | 0.240  | 0.280     | 6.10     | 7.11  |

| е   | 0.100  | BSC       | 2.54 BSC |       |

| eВ  |        | 0.430     |          | 10.92 |

| L   | 0.115  | 0.150     | 2.92     | 3.81  |

| М   |        | 10°       |          | 10°   |

GENERIC **MARKING DIAGRAM\***

| 16 <u> </u>                            | 1 |

|----------------------------------------|---|

| XXXXXXXXXXXXXX                         |   |

| • XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |   |

| O AWLYYWWG                             |   |

| 1 <del>00000000</del>                  | Ţ |

XXXXX = Specific Device Code

- = Assembly Location

- WL = Wafer Lot

А

- YY = Year

- WW = Work Week

- G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " .", may or may not be present.

| DOCUMENT NUMBER:                                                                  | 98ASB42431B                                                                                 | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|-----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| DESCRIPTION:                                                                      | DESCRIPTION: PDIP-16                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| ON Semiconductor reserves the right<br>the suitability of its products for any pa | to make changes without further notice to an<br>articular purpose, nor does ON Semiconducto | ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |  |  |  |  |  |

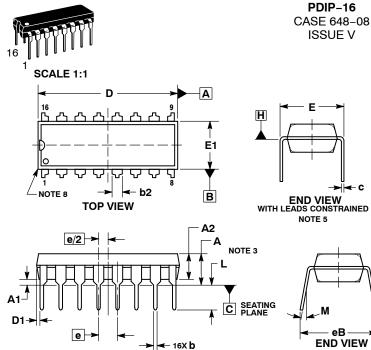

#### **MECHANICAL CASE OUTLINE** PACKAGE DIMENSIONS

#### SOIC-16 WB CASE 751G ISSUE E SCALE 1:1 NOTES A DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 1. CONTROLLING DIMENSION: MILLIMETERS 2. 16 🗢 0.25@ B@ В DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. з. <u>A A A A</u> RRRR ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF B DIMENSION AT MAXIMUM MATERIAL CONDITION. DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS. 4. MAXIMUM MOLD PROTRUSION OR FLASH TO BE 0.15 PER SIDE. 5. MILLIMETERS DIM MIN. MAX. H Н Α 2.35 2.65 h 8 45 0.25 A1 0.10 -16X B e DETAIL A в 0.35 0.49 0.2500 TAS BS END VIEW С 0.23 0.32 TOP VIEW D 10.15 10.45 7.40 7.60 Ε 1.27 BSC e 16X н 10.05 10.55 -L h 0.53 REF SEATIN **A1** 0.50 0.90 L SIDE VIEW М 0\* 7\* DETAIL A 2X SCALE 0000|0000 GENERIC 11.00 **MARKING DIAGRAM\*** 1 16X 1.62 .27 XXXXXXXXXXXX PITCH XXXXXXXXXXXX RECOMMENDED AWLYYWWG MOUNTING FOOTPRINT H H Η 1 H Н XXXXX = Specific Device Code = Assembly Location А = Wafer Lot WL YY = Year ww = Work Week G = Pb-Free Package \*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may

| DOCUMENT NUMBER:                                                                      | 98ASB42567B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DESCRIPTION:                                                                          | SOIC-16 WB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | -16 WB PAGE                                                                                                                                                                         |  |  |  |  |

| the right to make changes without furthe<br>purpose, nor does <b>onsemi</b> assume an | onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others. |                                                                                                                                                                                     |  |  |  |  |

or may not be present. Some products may

not follow the Generic Marking.

# DUSEM

DATE 08 OCT 2021

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using **onsemi** products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by **onsemi**. "Typical" parameters which may be provided in **onsemi** data sheets and/or specifications can and do vary in different applications and calcular performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. **onsemi** does not convey any license under any of its intellectual property rights nor the rights of others. **onsemi** products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use **onsemi** products for any such unintended or unauthorized application, Buyer shall indemnify and hold **onsemi** and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that **onsemi** was negligent regarding the design or manufacture of the part. **onsemi** is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

onsemi Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative