# TAS2770 20-W Digital Input Mono Class-D Audio Amplifier with Speaker I/V Sense

#### 1 Features

- High-Performance Mono Class-D Amplifier

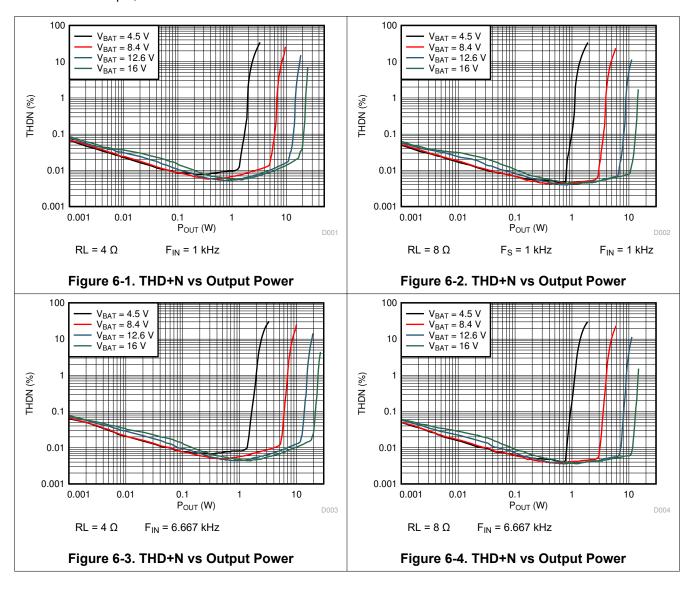

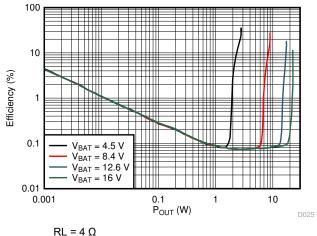

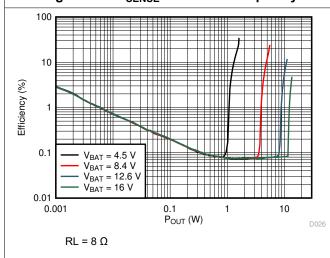

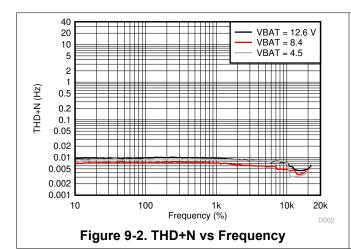

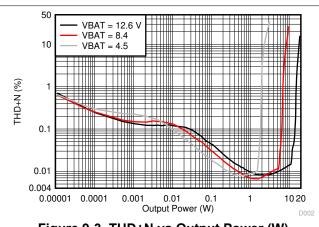

- 20-W at 1% THD+N (4 Ω, 16 V)

- 15.4-W at 1 % THD+N (4  $\Omega$ , 12.6 V)

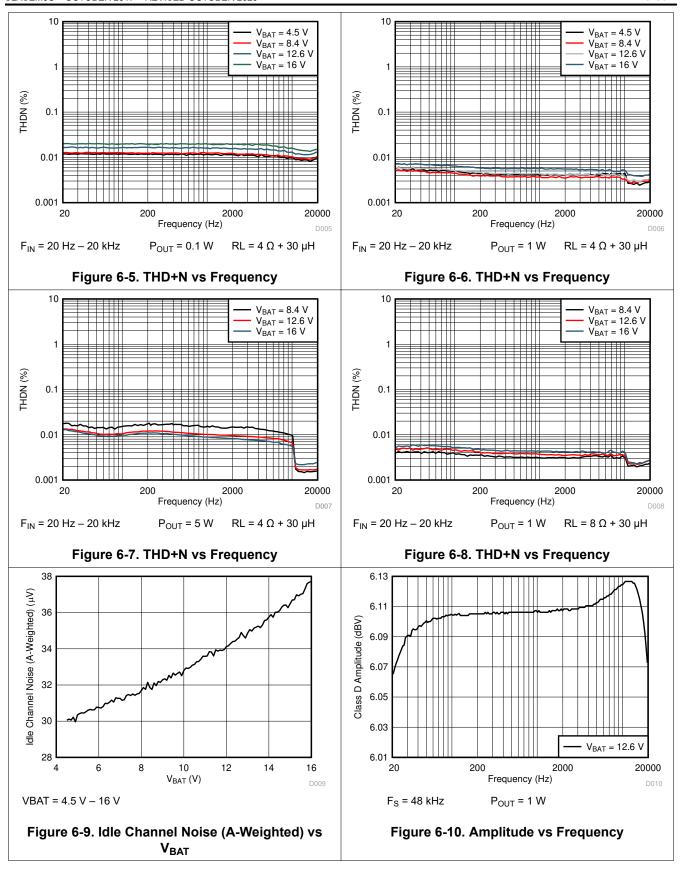

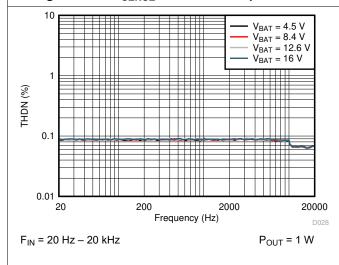

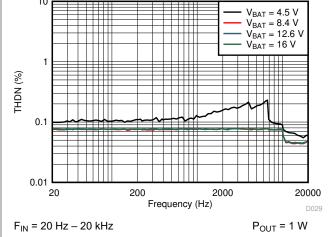

- 0.03 % THD+N at 1 W (4  $\Omega$ , VBAT = 12.6 V)

- 32-µVrms A-Weighted Idle Channel noise

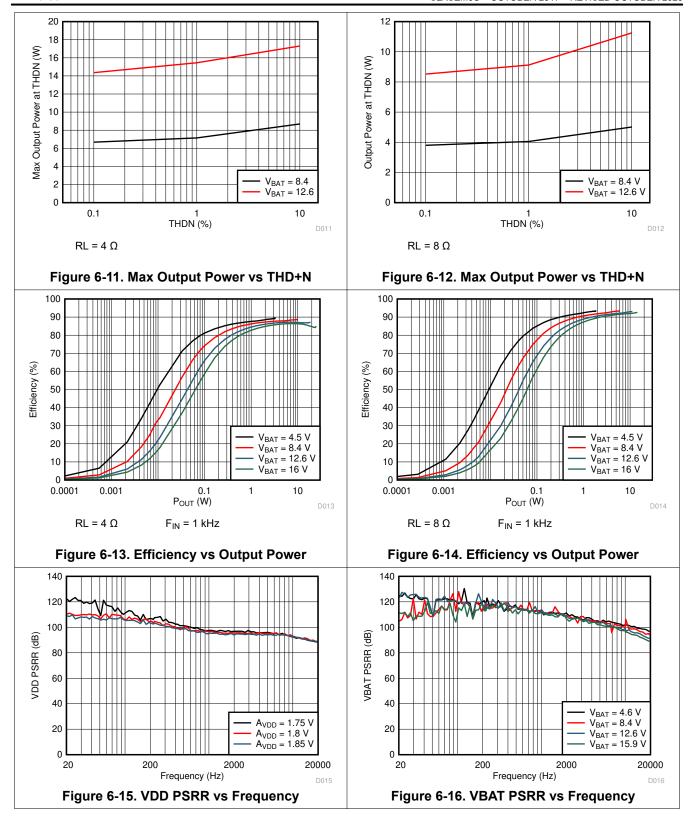

- 90-dB PSRR with 200 mV<sub>PP</sub> Ripple at 20 20 kHz

- 82.5% Efficiency at 1 W (4 Ω, VBAT = 12.6 V)

- < 1 µA HW Shutdown VBAT Current</li>

- 42 mW / 63 mW Idle Dissipation (8.4 V / 12.6 V)

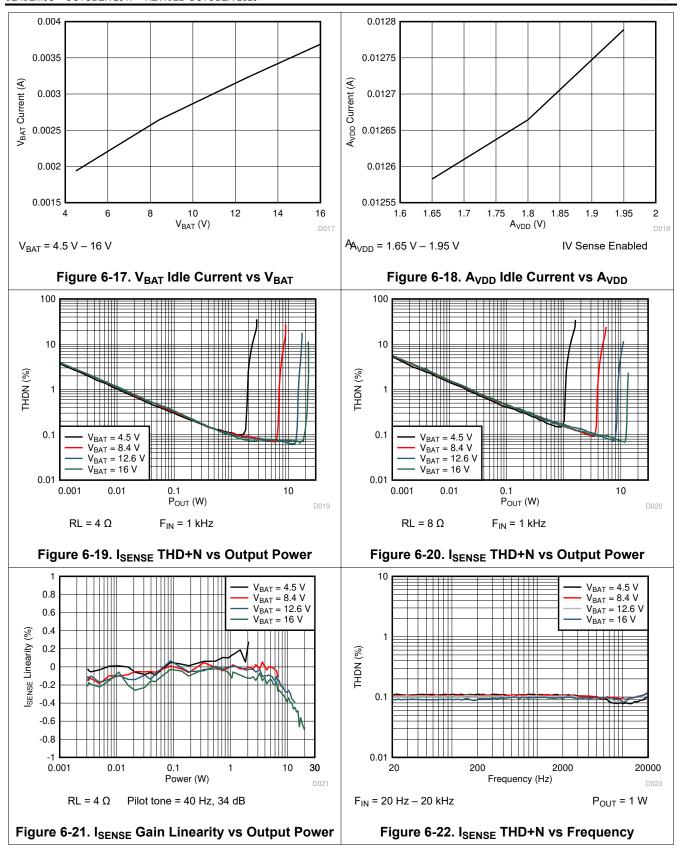

- Speaker Voltage and Current Sense

- Real-Time Diagnostics Using I/V Speaker Sense

- Over Current

- Short Circuit(short to power, short to ground and terminal-to-terminal short)

- Over-Temperature

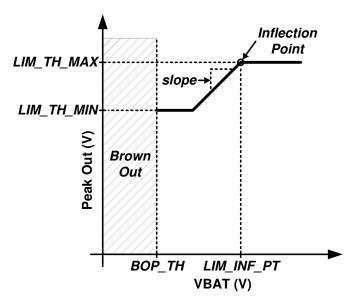

- VBAT Tracking Peak Voltage Limiter with Brown **Out Prevention**

- 44.1-kHz to 192-kHz Sample Rates

- · Flexible User Interfaces

- I<sup>2</sup>S/TDM: 8 Channels (32-bit / 96 kHz)

- I<sup>2</sup>C: 8 selectable Addresses

- MCLK Free Operation

- Low Pop and Click

- **Power Supplies**

- VBAT: 4.5 V to 16 V

- AVDD: 1.8 V

- Spread-Spectrum Low EMI Mode

- Thermal and Over Current Protection

## 2 Applications

- **Laptop Computers**

- **Bluetooth Speakers**

- Home Automation

- Smart Speakers/IoT

## 3 Description

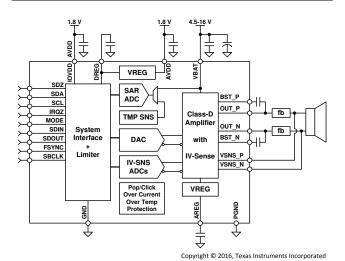

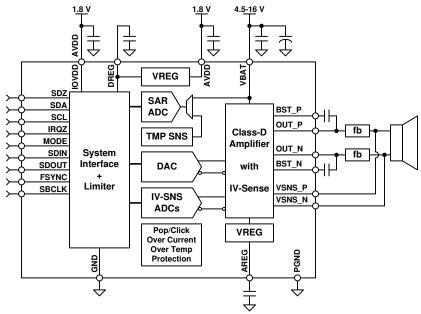

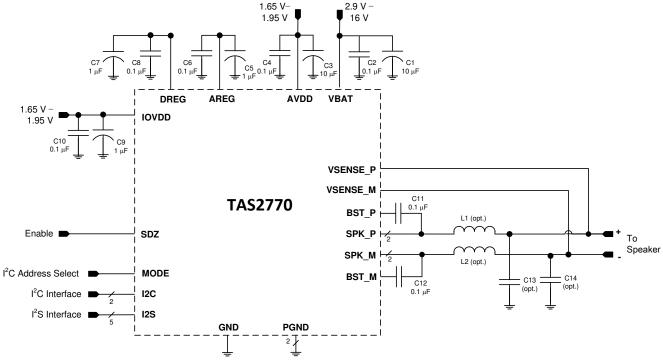

The TAS2770 is a mono, digital input Class-D audio amplifier optimized for efficiently driving small loudspeakers . The output power, protection features and packages make TAS2770 a good choice for Smart speakers, Bluetooth speakers, automation devices, Notebook computers and tablets.

The Class-D amplifier is capable of delivering 20W of continuous power into a 4-Ω load at 16V and 15W into an  $8-\Omega$  load at 16V both at 1% THD. The broad voltage input range of 4.5-16V and the high output power makes this amplifier versatile enough to work with battery power or with line powered systems

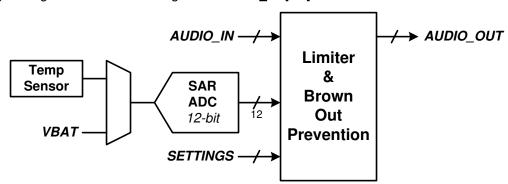

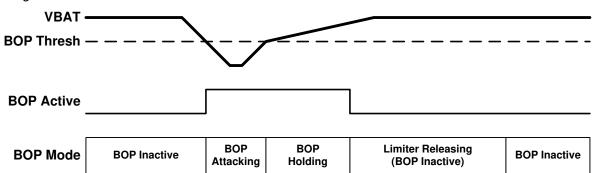

A Brown-Out preventer tracks peak voltage and automatically self-limits the gain to the voltage available. This hardware implemented feature reduces the amplifier's demand on system power preventing both audio cut out and system shutdown

The TAS2770 can be used as a conventional amp or with host based speaker protection algorithms. The integrated speaker voltage and current sense provides for real time feedback of loudspeaker conditions to the protection algorithms through a return I2S path.

Up to eight devices can share a common bus via either I<sup>2</sup>S/TDM + I<sup>2</sup>C.

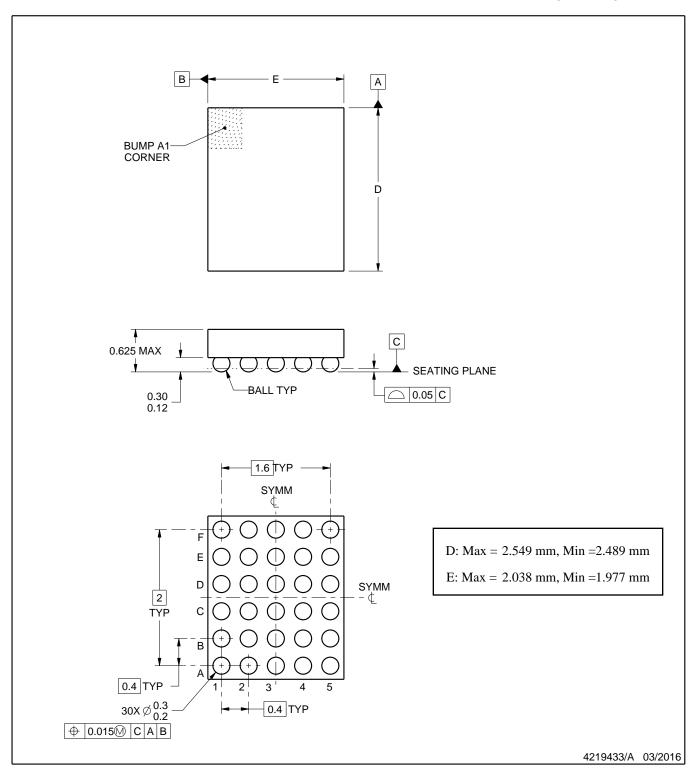

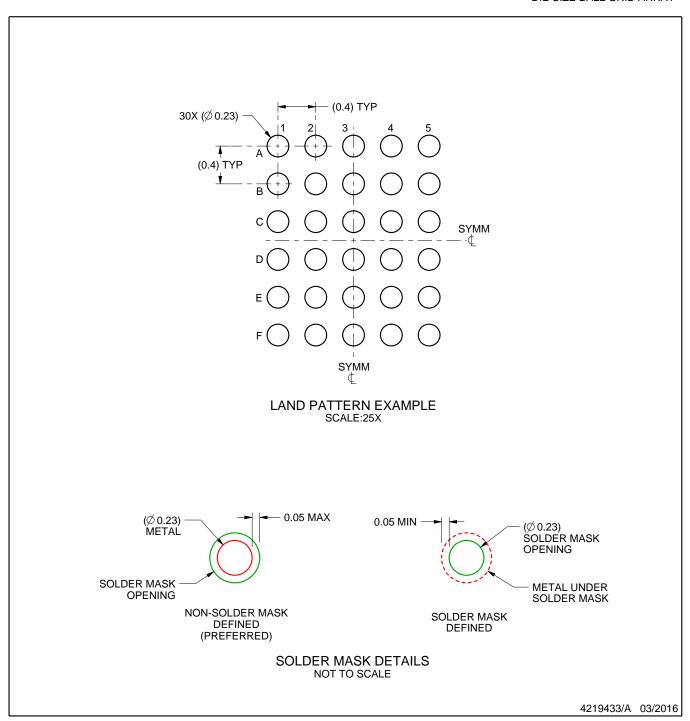

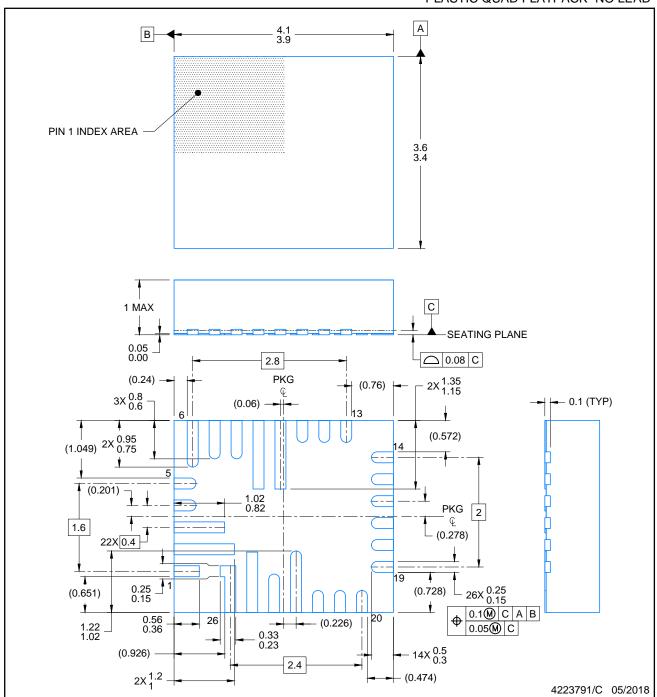

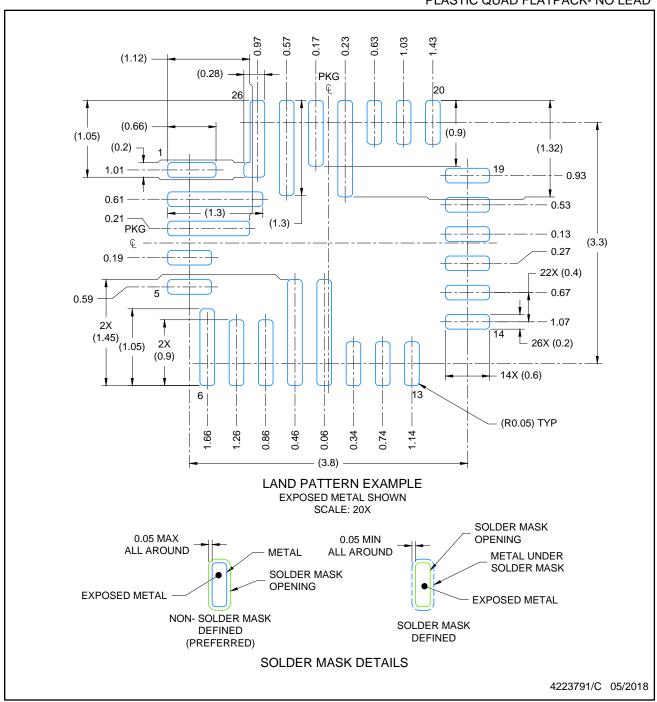

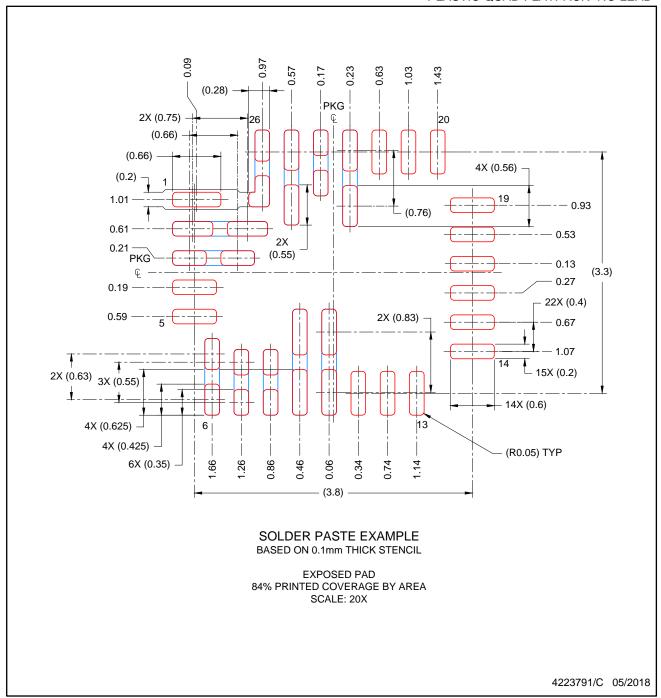

The TAS2770 device is available in a 26-pin, 0.4-mm pitch QFN for a compact PCB footprint.

#### **Device Information**

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|-------------|---------|-----------------|

| TAS2770     | QFN     | 4 mm × 3.5 mm   |

| TAS2770     | DSBGA   | 2 mm × 2.52 mm  |

| SNP002770   | QFN     | 4 mm × 3.5 mm   |

| SNP002770   | DSBGA   | 2 mm × 2.52 mm  |

**Functional Block Diagram**

## **Table of Contents**

| 1 Features                               | 1              | 8.2 Functional Block Diagram                        | 20 |

|------------------------------------------|----------------|-----------------------------------------------------|----|

| 2 Applications                           |                | 8.3 Feature Description                             |    |

| 3 Description                            | 1              | 8.4 Device Functional Modes                         | 23 |

| 4 Revision History                       |                | 8.5 Register Maps                                   | 53 |

| 5 Pin Configuration and Functions        | 3              | 9 Application and Implementation                    |    |

| Pin Functions                            | 4              | 9.1 Application Information                         | 79 |

| 6 Specifications                         |                | 9.2 Typical Application                             |    |

| 6.1 Absolute Maximum Ratings             |                | 9.3 Initialization Set Up                           |    |

| 6.2 ESD Ratings                          |                | 10 Power Supply Recommendations                     |    |

| 6.3 Recommended Operating Conditions     |                | 11 Layout                                           |    |

| 6.4 Thermal Information                  | <mark>5</mark> | 11.1 Layout Guidelines                              |    |

| 6.5 Electrical Characteristics           | 6              | 11.2 Layout Example                                 |    |

| 6.6 I <sup>2</sup> C Timing Requirements | 11             | 12 Device and Documentation Support                 | 92 |

| 6.7 TDM Port Timing Requirements         |                | 12.1 Receiving Notification of Documentation Update |    |

| 6.8 PDM Port Timing Requirements         | 12             | 12.2 Community Resources                            | 92 |

| 6.9 Typical Characteristics              | 13             | 12.3 Trademarks                                     | 92 |

| 7 Parameter Measurement Information      | 19             | 13 Mechanical, Packaging, and Orderable             |    |

| 8 Detailed Description                   | 20             | Information                                         | 93 |

| 8.1 Overview                             |                |                                                     |    |

|                                          |                |                                                     |    |

| · · · · · · · · · · · · · · · · · · ·    |                |                                                     |    |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| , , ,                                                                |      |

|----------------------------------------------------------------------|------|

| Changes from Revision B (October 2018) to Revision C (October 2020)  | Page |

| Changed information on front page                                    | 1    |

| Changed VBAT Max in Section 6.3 from 16 V to 18 V                    | 5    |

| Changed REV_ID                                                       |      |

| Changes from Revision A (December 2017) to Revision B (October 2018) | Page |

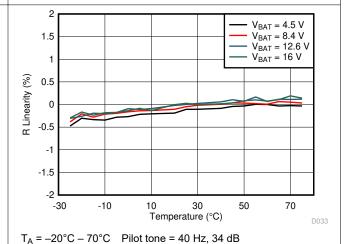

| Changed From: Efficiency (%) To: VDD PSRR (dB) in Figure 6-15        | 13   |

| Changed From: Efficiency (%) To: VBAT PSRR (dB) in Figure 6-16       | 13   |

| Changes from Revision * (October 2017) to Revision A (December 2017) | Page |

| Released TAS2770 as Production Data                                  | 1    |

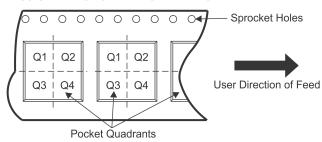

## **5 Pin Configuration and Functions**

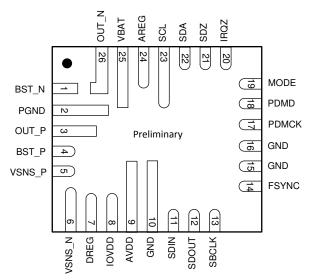

Drawing is Preliminary.

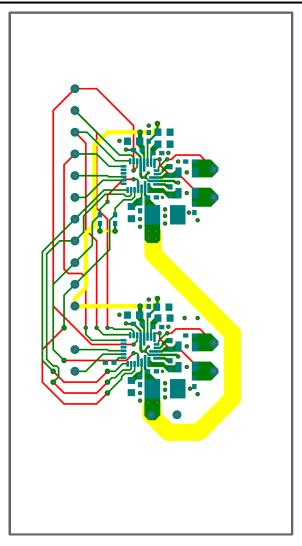

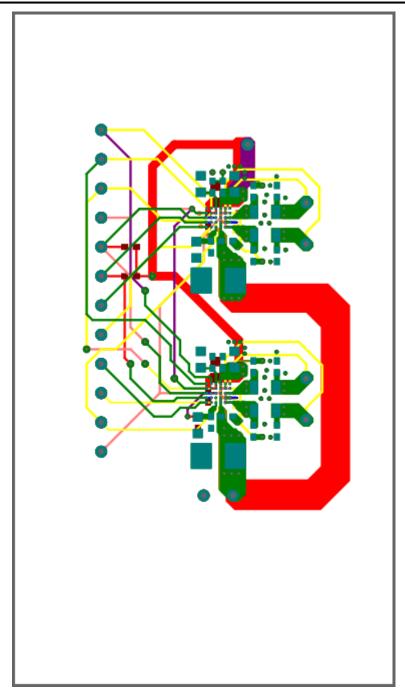

Figure 5-1. QFN Package 26-Pin RJQ Top View

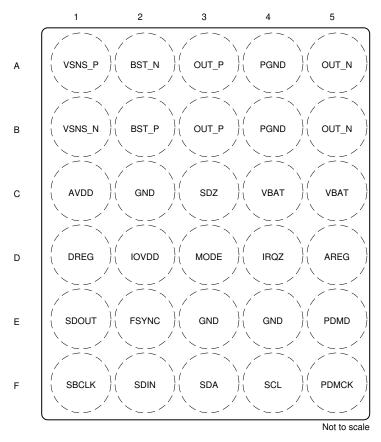

Figure 5-2. WCSP 30-Ball Top View

## **Pin Functions**

|               | ı             | PIN    | .,_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------|---------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DSBGA         | QFN           | NAME   | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| D5            | 24            | AREG   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Gate drive voltage regulator output. Decouple with cap to GND. Do not connect to external load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| C1            | 9             | AVDD   | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Analog power input. Connect to 1.8V supply and decouple to GND with cap.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

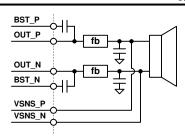

| A2            | 1             | BST_N  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Class-D negative bootstrap. Connect a cap between BST_N and OUT_N.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| B2            | 4             | BST_P  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Class-D positive bootstrap. Connect a cap between BST_P and OUT_P.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| D1            | 7             | DREG   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Digital core voltage regulator output. Bypass to GND with a cap. Do not connect to external load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| E2            | 14            | FSYNC  | Ţ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TDM Frame Sync.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| C2, E3,<br>E4 | 10, 15,<br>16 | GND    | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Analog GND. Connect to PCB GND Plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| D2            | 8             | IOVDD  | to external load.  AVDD P Analog power input. Connect to 1.8V supply and decouple to GND with BST_N I Class-D negative bootstrap. Connect a cap between BST_N and OUT_BST_P I Class-D positive bootstrap. Connect a cap between BST_P and OUT_FDREG O Digital core voltage regulator output. Bypass to GND with a cap. Do not connect to external load.  FSYNC I TDM Frame Sync.  GND P Analog GND. Connect to PCB GND Plane.  IOVDD P Digital IO Supply. Connect to the same 1.8 V supply that powers AVDD decouple with a cap to GND.  IRQZ O OPEN drain, actve low interrupt pin. Pull up to IOVDD with resistor if opt internal pull up is not used.  Mode detect pin. This pin can detect a short to IOVDD or GND, a 470 C connection to IOVDD or GND and a 47 kΩ connection to IOVDD. Minim capacitive loading on this pin and do not connect to any other load.  OUT_N O Class-D negative output.  OUT_P O Class-D positive output.  PDMCK IO PDM Clock.  PDMD I PDM Digital Input.  PGND P Class-D GND. Connect to PCB GND Plane.  SBCLK I TDM Serial Bit Clock in TDM/I²C Mode.  SCL I I²C Clock Pin. Pull up to IOVDD with a resistor.  SDIN I TDM Serial Data Input.  SDOUT IO TDM Serial Data Output in TDM/I²C Mode. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

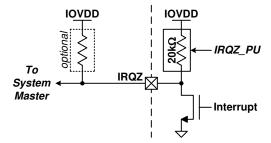

| D4            | 20            | IRQZ   | IRQZ O Open drain, active low interrupt pin. Pull up to IOVDD with resistor if opticinternal pull up is not used.  Mode detect pin. This pin can detect a short to IOVDD or GND, a 470 $\Omega$ connection to IOVDD or GND, a 2.2 k $\Omega$ connection to IOVDD or GND, a connection to IOVDD or GND and a 47 k $\Omega$ connection to IOVDD. Minimized                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| D3            | 19            | MODE   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Mode detect pin. This pin can detect a short to IOVDD or GND, a 470 $\Omega$ connection to IOVDD or GND, a 2.2 k $\Omega$ connection to IOVDD or GND, a 10 k $\Omega$ connection to IOVDD or GND and a 47 k $\Omega$ connection to IOVDD. Minimize capacitive loading on this pin and do not connect to any other load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| A5, B5        | 26            | OUT_N  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Class-D negative output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| A3, B3        | 3             | OUT_P  | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Class-D positive output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| F5            | 17            | PDMCK  | Ю                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PDM Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| E5            | 18            | PDMD   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PDM Digital Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| A4, B4        | 2             | PGND   | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Class-D GND. Connect to PCB GND Plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| F1            | 13            | SBCLK  | Ţ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TDM Serial Bit Clock in TDM/I <sup>2</sup> C Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| F4            | 23            | SCL    | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sup>2</sup> C Clock Pin. Pull up to IOVDD with a resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| F3            | 22            | SDA    | Ю                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sup>2</sup> C Data Pin. Pull up to IOVDD with a resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| F2            | 11            | SDIN   | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TDM Serial Data Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| E1            | 12            | SDOUT  | Ю                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | TDM Serial Data Output in TDM/I <sup>2</sup> C Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| С3            | 21            | SDZ    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Active low hardware shutdown.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| C4, C5        | 25            | VBAT   | Р                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Class-D power supply input. Connect to VBAT supply and decouple with a cap.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| B1            | 6             | VSNS_N | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Voltage Sense negative input. Connect to Class-D negative output after Ferrite bead filter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| A1            | 5             | VSNS_P | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Digital IO Supply. Connect to the same 1.8 V supply that powers AVDD an decouple with a cap to GND.  Open drain, actve low interrupt pin. Pull up to IOVDD with resistor if option internal pull up is not used.  Mode detect pin. This pin can detect a short to IOVDD or GND, a 470 Ω connection to IOVDD or GND, a 2.2 kΩ connection to IOVDD or GND, a 1t connection to IOVDD or GND and a 47 kΩ connection to IOVDD. Minimize capacitive loading on this pin and do not connect to any other load.  Class-D negative output.  Class-D positive output.  PDM Clock.  PDM Digital Input.  Class-D GND. Connect to PCB GND Plane.  TDM Serial Bit Clock in TDM/I²C Mode.  I²C Clock Pin. Pull up to IOVDD with a resistor.  I²C Data Pin. Pull up to IOVDD with a resistor.  TDM Serial Data Input.  TDM Serial Data Output in TDM/I²C Mode.  Active low hardware shutdown.  Class-D power supply input. Connect to VBAT supply and decouple with a Voltage Sense negative input. Connect to Class-D negative output after Fe |  |

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (1)

|                              |                                                                                          | MIN  | MAX | UNIT |

|------------------------------|------------------------------------------------------------------------------------------|------|-----|------|

|                              | AVDD                                                                                     | -0.3 | 2   | V    |

| Supply Voltage               | IOVDD                                                                                    | -0.3 | 2   | V    |

|                              | VBAT                                                                                     | -0.3 | 18  | V    |

| Input voltage <sup>(2)</sup> | Digital IOs referenced to IOVDD supply                                                   | -0.3 | 2.3 | V    |

| Operating free-air temp      | verature, T <sub>A</sub> ; Device is functional and reliable, some performance degraded. | -40  | 85  | °C   |

| Performance free-air te      | emperature, T <sub>P</sub> ; All performance characteristics are met.                    | -20  | 70  | °C   |

| Operating junction temp      | perature, T <sub>J</sub>                                                                 | -40  | 150 | °C   |

| Storage temperature, T       | -<br>stg                                                                                 | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Procedures. Exposure to absolute-maximum-rated conditions for extended periods can affect device reliability.

## 6.2 ESD Ratings

|   |                                |                                                                                | VALUE | UNIT |

|---|--------------------------------|--------------------------------------------------------------------------------|-------|------|

|   |                                | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2500 |      |

| V | ((ESD) Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1500 | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                  |                                  | MIN  | NOM   | MAX  | UNIT |

|------------------|----------------------------------|------|-------|------|------|

| AVDD             | Supply voltage                   | 1.65 | 1.8   | 1.95 | V    |

| IOVDD            | Supply voltage                   | 1.65 | 1.8   | 1.95 | V    |

| VBAT             | Supply voltage                   | 4.5  |       | 18   | V    |

| V <sub>IH</sub>  | High-level digital input voltage |      | IOVDD |      | V    |

| V <sub>IL</sub>  | Low-level digital input voltage  |      | 0     |      | V    |

| R <sub>SPK</sub> | Minimum speaker impedance        | 3.2  |       |      | Ω    |

| L <sub>SPK</sub> | Minimum speaker inductance       | 10   |       |      | μΗ   |

## **6.4 Thermal Information**

|                       |                                              | TAS2770   |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC(1)                            | QFN (RJQ) | UNIT |

|                       |                                              | 26 PINS   |      |

| $R_{\theta JA}$       | Junction-to-ambient thermal resistance       | 57.0      | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.3       | °C/W |

| R <sub>0JB</sub>      | Junction-to-board thermal resistance         | 8.5       | °C/W |

| ΨЈТ                   | Junction-to-top characterization parameter   | 0.2       | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 8.7       | °C/W |

Copyright © 2020 Texas Instruments Incorporated

<sup>(2)</sup> All digital inputs and IOs are failsafe.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

|                       |                                              | TAS2770   |      |

|-----------------------|----------------------------------------------|-----------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | QFN (RJQ) | UNIT |

|                       |                                              | 26 PINS   |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | NA        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## **6.5 Electrical Characteristics**

$T_A$  = 25 °C, VBAT = 12.6 V, AVDD = IOVDD = 1.8 V,  $R_L$  = 4  $\Omega$  + 33  $\mu$ H,  $f_{in}$  = 1 kHz, SSM,  $f_s$  = 48 kHz, Gain = 21 dBV, SDZ = 1, Measured filter free using Section 7 (unless otherwise noted).

|                       | PARAMETER                                                       | TEST CONDITIONS                                                                    | MIN               | TYP   | MAX             | UNIT   |

|-----------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------|-------|-----------------|--------|

| DIGITAL II            | NPUT and OUTPUT                                                 |                                                                                    |                   |       |                 |        |

| V <sub>IH</sub>       | High-level digital input logic voltage threshold                | All digital pins except SDA and SCL; IOVDD = 1.8 V.                                | 0.65 ×<br>IOVDD   |       |                 | V      |

| V <sub>IL</sub>       | Low-level digital input logic voltage threshold                 | All digital pins except SDA and SCL; IOVDD = 1.8 V.                                |                   |       | 0.35 ×<br>IOVDD | V      |

| V <sub>IH(I2C)</sub>  | High-level digital input logic voltage threshold                | SDA and SCL; IOVDD = 1.8 V.                                                        | 0.7 x<br>IOVDD    |       |                 | V      |

| V <sub>IL(I2C)</sub>  | Low-level digital input logic voltage threshold                 | SDA and SCL; IOVDD = 1.8 V.                                                        |                   |       | 0.3 x<br>IOVDD  | V      |

| V <sub>OH</sub>       | High-level digital output voltage                               | All digital pins except SDA, SCL and IRQZ; IOVDD = 1.8 V; I <sub>OH</sub> = 2 mA.  | IOVDD –<br>0.45 V |       |                 | V      |

| V <sub>OL</sub>       | Low-level digital output voltage                                | All digital pins except SDA, SCL and IRQZ; IOVDD = 1.8 V; I <sub>OL</sub> = -2 mA. |                   |       | 0.45            | V      |

| V <sub>OL(I2C)</sub>  | Low-level digital output voltage                                | SDA and SCL; IOVDD = 1.8 V; $I_{OL(I2C)} = -2 \text{ mA}.$                         |                   |       | 0.2 x<br>IOVDD  | V      |

| V <sub>OL(IRQZ)</sub> | Low-level digital output voltage for IRQZ open drain Output     | IRQZ; IOVDD = 1.8 V; $I_{OL(IRQZ)} = -2$ mA.                                       |                   |       | 0.45            | V      |

| Ін                    | Input logic-high leakage for digital inputs                     | All digital pins; Input = IOVDD.                                                   | -5                | 0.1   | 5               | μΑ     |

| lıL                   | Input logic-low leakage for digital inputs                      | All digital pins; Input = GND.                                                     | <b>–</b> 5        | 0.1   | 5               | μA     |

| C <sub>IN</sub>       | Input capacitance for digital inputs                            | All digital pins                                                                   |                   | 5     |                 | pF     |

| R <sub>PD</sub>       | Pull down resistance for digital input/IO pins when asserted on | SDOUT, SDIN, FSYNC, SBCLK, PDMD, PDMCK                                             |                   | 18    |                 | kΩ     |

| TDM SERI              | AL AUDIO PORT                                                   |                                                                                    |                   |       |                 |        |

|                       |                                                                 | Single Speed, I <sup>2</sup> S/TDM Operation                                       |                   | 48    |                 |        |

|                       | PCM Sample Rates & FSYNC Input                                  | Double Speed, I <sup>2</sup> S/TDM Operation                                       |                   | 96    |                 | kHz    |

|                       | Frequency                                                       | Quadruple Speed, I <sup>2</sup> S/TDM<br>Operation                                 |                   | 192   |                 | KI IZ  |

|                       | SBCLK Input Frequency                                           | I <sup>2</sup> S/TDM Operation                                                     | 2.54              |       | 27.1            | MHz    |

|                       | CDCLI/ Mayimum Input litter                                     | RMS Jitter below 40 kHz that can be tolerated without performance degradation      |                   | 1     |                 |        |

|                       | SBCLK Maximum Input Jitter                                      | RMS Jitter above 40 kHz that can be tolerated without performance degradation      |                   | 10    |                 | ns     |

|                       | SBCLK Cycles per FSYNC in I <sup>2</sup> S and TDM Modes        | Values: 64, 96, 128, 192, 256, 384 and 512                                         | 64                |       | 512             | Cycles |

| PDM AUD               | IO PORT                                                         |                                                                                    |                   |       |                 |        |

|                       | DDM also de format f                                            | Single Rate PDM                                                                    |                   | 3.072 |                 |        |

|                       | PDM clock input frequency                                       | Double Rate PDM                                                                    | ,                 | 6.144 |                 | MHz    |

|                       |                                                                 |                                                                                    |                   |       |                 |        |

$T_A$  = 25 °C, VBAT = 12.6 V, AVDD = IOVDD = 1.8 V,  $R_L$  = 4  $\Omega$  + 33  $\mu$ H,  $f_{in}$  = 1 kHz, SSM,  $f_s$  = 48 kHz, Gain = 21 dBV, SDZ = 1, Measured filter free using Section 7 (unless otherwise noted).

PARAMETER

TEST CONDITIONS

MIN TYP

MAX UNIT

Single Speed PCM. Values: 64X and

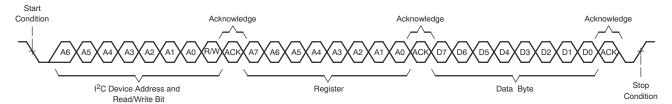

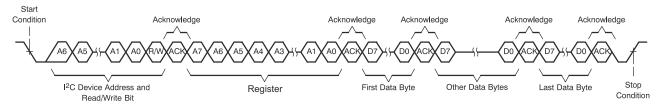

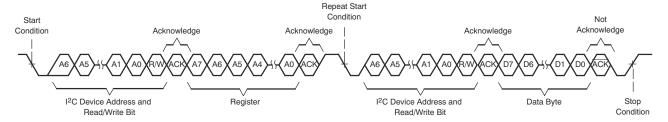

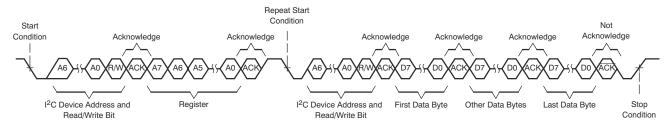

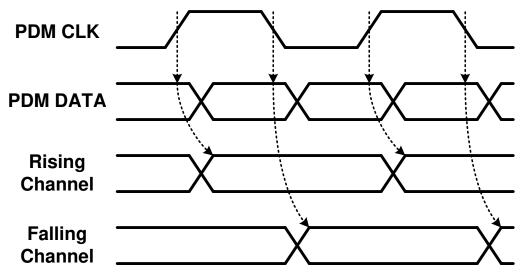

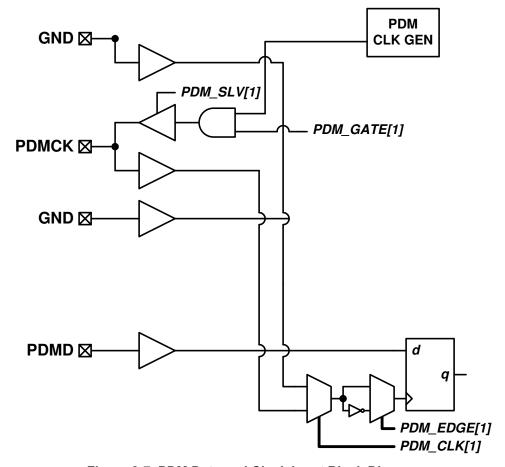

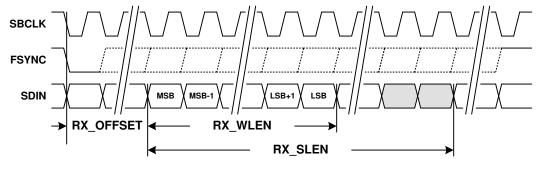

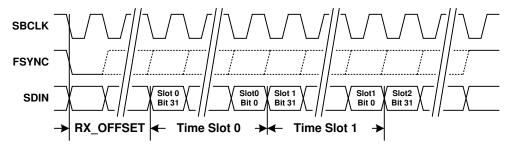

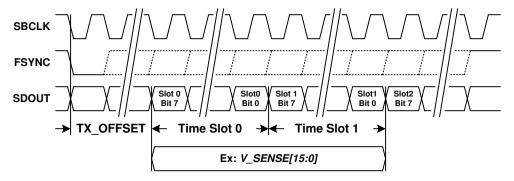

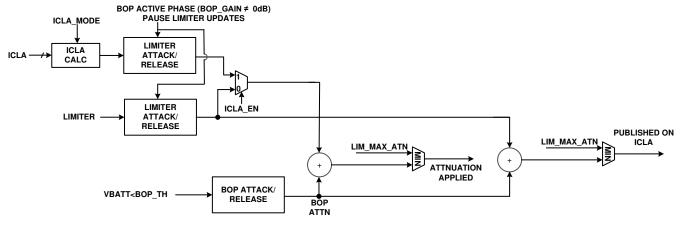

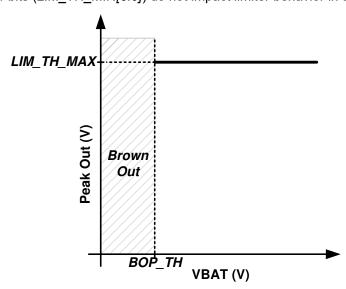

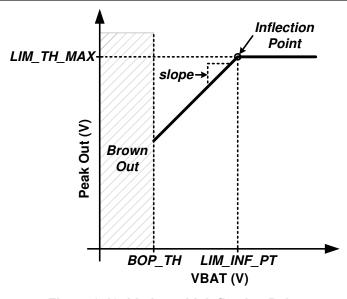

64