ADS1204 SBAS301D – OCTOBER 2003 – REVISED FEBRUARY 2020

# ADS1204 Four 1-Bit, 10-MHz, 2nd-Order, Delta-Sigma Modulators

#### 1 Features

- 16-bit resolution

- 14-bit linearity

- Resolution, speed trade-off:

10-bit effective resolution with 10-µs signal delay

(12-bit with 19 µs)

- ±2.5-V input range at 2.5 V

- Internal reference voltage: 2%

- Gain error: 0.5%

- · Four independent delta-sigma modulators

- · Four input reference buffers

- · Onboard 20-MHz oscillator

- · Selectable internal or external clock

- Operating temperature range: -40°C to +105°C

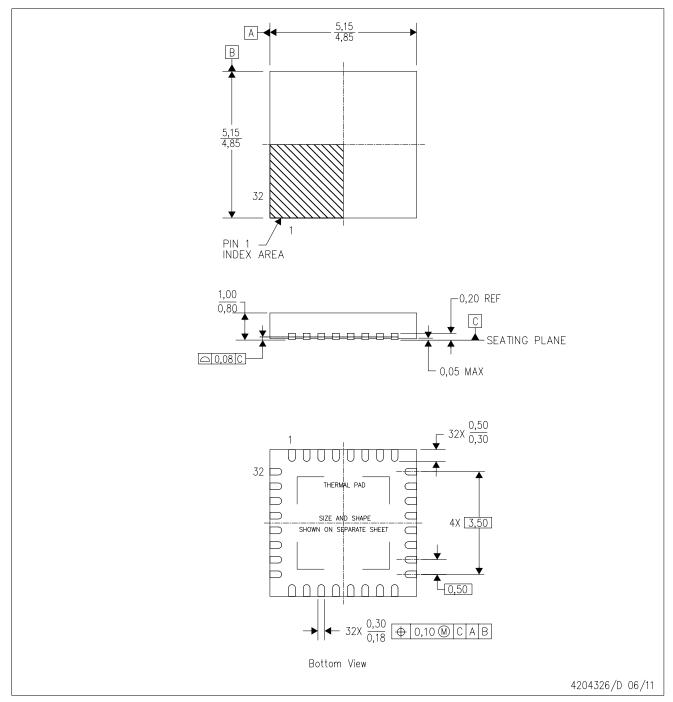

- Package: VQFN-32 (5 mm x 5 mm)

# 2 Applications

- Motor controls

- Current measurement

- · Industrial process controls

- Smart transmitters

- Weight scales

- Pressure transducers

- Portable instruments

- Instrumentation

# 3 Description

The ADS1204 is a four-channel, high-performance device, with four delta-sigma ( $\Delta\Sigma$ ) modulators with 100-dB dynamic range, operating from a single 5-V supply. The differential inputs are ideal for direct connection transducers in industrial environment. With the appropriate digital filter and modulator rate, the device can be used to achieve 16-bit analog-to-digital (A/D) conversion with no missing code. Effective resolution of 12 bits can be obtained with a digital filter data rate of 160 kHz at a modulator rate of 10 MHz. The ADS1204 is designed for use in medium- to high-resolution measurement applications including current measurements, smart transmitters, industrial process control, weight scales, chromatography, and portable instrumentation. It is available in a VQFN-32 (5×5) package.

# **Device Information**<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |

|-------------|-----------|-------------------|--|--|

| ADS1204     | VQFN (32) | 5.00 mm × 5.00 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

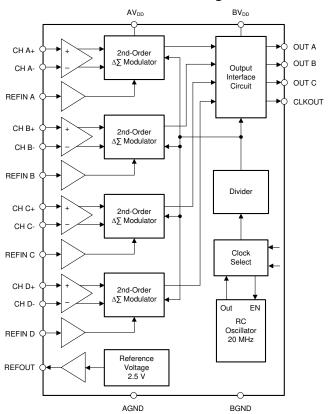

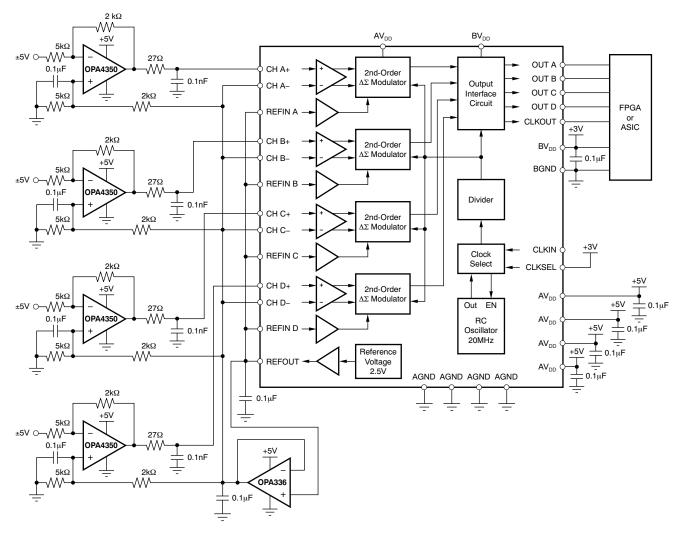

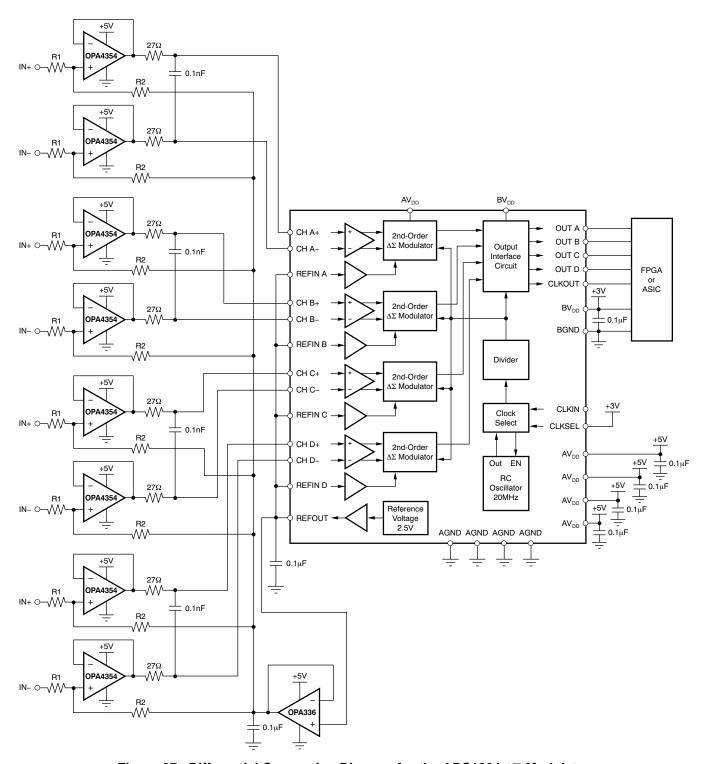

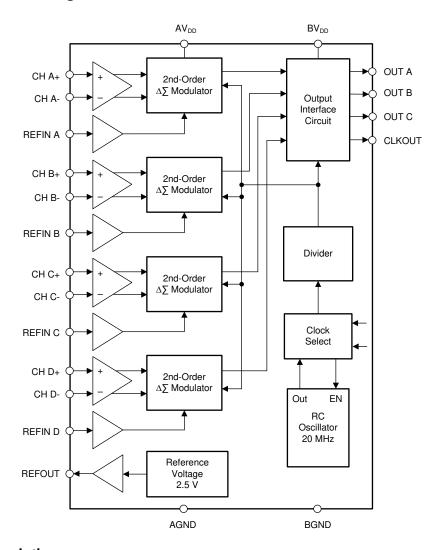

#### **Functional Block Diagram**

# **Table of Contents**

| 1 | Features 1                           |    | 7.3 Feature Description                             | 10   |

|---|--------------------------------------|----|-----------------------------------------------------|------|

| 2 | Applications 1                       |    | 7.4 Device Functional Modes                         | 19   |

| 3 | Description 1                        | 8  | Application and Implementation                      | . 19 |

| 4 | Revision History2                    |    | 8.1 Application Information                         | 19   |

| 5 | Pin Configuration and Functions 4    | 9  | Power Supply Recommendations                        | 2′   |

| 6 | Specifications5                      |    | 9.1 Power-Supply Sequencing                         | 2    |

| • | 6.1 Absolute Maximum Ratings 5       |    | 9.2 Power-Supply Decoupling                         | 2    |

|   | 6.2 ESD Ratings                      | 10 | Layout                                              | . 22 |

|   | 6.3 Recommended Operating Conditions |    | 10.1 Layout Guidelines                              | 22   |

|   | 6.4 Thermal Information              |    | 10.2 Layout Example                                 | 23   |

|   | 6.5 Electrical Characteristics       | 11 | Device and Documentation Support                    | 24   |

|   | 6.6 Timing Requirements: 5.0 V       |    | 11.1 Receiving Notification of Documentation Update | s 24 |

|   | 6.7 Timing Requirements: 3.0 V       |    | 11.2 Support Resources                              | 24   |

|   | 6.8 Typical Characteristics          |    | 11.3 Trademarks                                     | 24   |

| 7 | Detailed Description 14              |    | 11.4 Electrostatic Discharge Caution                | 2    |

| - | 7.1 Overview                         |    | 11.5 Glossary                                       | 24   |

|   | 7.2 Functional Block Diagram         | 12 | Mechanical, Packaging, and Orderable Information    | 24   |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

## Changes from Revision C (February 2009) to Revision D

**Page**

| • | Added Device Information table, page 1 graphic, ESD Ratings table, Thermal Information table, Overview section, Functional Block Diagram section, Feature Description section, Device Functional Modes section, Application and Implementation section, Power Supply Recommendations section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1  |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| • | Changed QFN to VQFN throughout document                                                                                                                                                                                                                                                                                                                                                              | 1  |

| • | Changed Applications section                                                                                                                                                                                                                                                                                                                                                                         | 1  |

| • | Deleted Ordering Information table                                                                                                                                                                                                                                                                                                                                                                   | 5  |

| • | Changed Power dissipation to point to Thermal Information table instead, added unit                                                                                                                                                                                                                                                                                                                  | 5  |

| • | Changed External clock maximum specification from 24 MHz to 32 MHz in Recommended Operating Conditions table                                                                                                                                                                                                                                                                                         | 6  |

| • | Changed footnote in Recommended Operating Conditions table                                                                                                                                                                                                                                                                                                                                           | 6  |

| • | Deleted Dissipation Ratings table                                                                                                                                                                                                                                                                                                                                                                    | 6  |

| • | Changed External clock frequency maximum specification from 24 MHz to 32 MHz in Electrical Characteristics table                                                                                                                                                                                                                                                                                     | 7  |

| • | Changed CLKIN period minimum specification from 41.6 ns to 31.25 ns in Timing Requirements: 5.0 V table                                                                                                                                                                                                                                                                                              | ç  |

| • | Changed NOM column to MAX column in <i>Timing Requirements: 5.0 V</i> table                                                                                                                                                                                                                                                                                                                          | ç  |

| • | Changed BV <sub>DD</sub> from 5 V to 3 V in <i>Timing Requirements: 3.0 V</i> test conditions                                                                                                                                                                                                                                                                                                        | 9  |

| • | Changed CLKIN period minimum specification from 41.6 ns to 31.25 ns in Timing Requirements: 3.0 V table                                                                                                                                                                                                                                                                                              | ç  |

| • | Changed Layout section                                                                                                                                                                                                                                                                                                                                                                               | 22 |

# Changes from Revision B (August 2007) to Revision C

Updated document format .....

Page

| • | Extended operating temperature range from +85°C to +105°C throughout document                                                           | 1 |

|---|-----------------------------------------------------------------------------------------------------------------------------------------|---|

| • | Deleted operating free-air temperature range row from Absolute Maximum Ratings table                                                    | 5 |

| • | Added free-air temperature range ratings to Recommended Operating Conditions table                                                      | 6 |

| • | Changed Dissipation Ratings table                                                                                                       | 6 |

| • | Changed typical specification in <i>Input capacitance</i> row of <i>Analog Input</i> section of <i>Electrical Characteristics</i> table | 6 |

Submit Documentation Feedback

Copyright © 2003–2020, Texas Instruments Incorporated

#### www.ti.com

| _        | Added note to QFN package                                                                                              | 4              |

|----------|------------------------------------------------------------------------------------------------------------------------|----------------|

| CI       | Changes from Revision A (June 2004) to Revision B                                                                      | Page           |

| <u>•</u> | Updated typical characteristic graphs to reflect extended temperature range                                            | 10             |

| •        | Deleted test condition of V <sub>OUT</sub> row in Voltage Reference Output section of Electrical Characteristics table | 6              |

| •        | Added additional specification for Total Harmonic Distortion in AC Accuracy section of Electrical Characters           | istics table 6 |

# TEXAS INSTRUMENTS

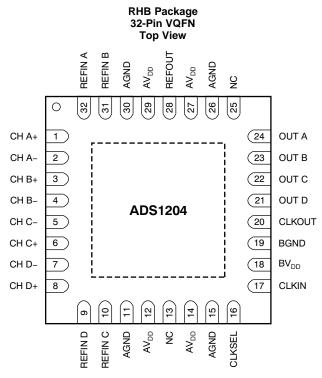

# 5 Pin Configuration and Functions

NOTE: The thermal pad is internally connected to the substrate. This pad can be connected to the analog ground or left floating. Keep the thermal pad separate from the digital ground, if possible.

#### **Pin Functions**

| PIN              |     |                    |                                                                                 |  |

|------------------|-----|--------------------|---------------------------------------------------------------------------------|--|

| NAME             | NO. | I/O <sup>(1)</sup> | DESCRIPTION                                                                     |  |

| CH A+            | 1   | AI                 | Analog input of channel A: noninverting input                                   |  |

| CH A-            | 2   | Al                 | Analog input of channel A: inverting input                                      |  |

| CH B+            | 3   | AI                 | Analog input of channel B: noninverting input                                   |  |

| CH B-            | 4   | AI                 | Analog input of channel B: inverting input                                      |  |

| CH C-            | 5   | AI                 | Analog input of channel C: inverting input                                      |  |

| CH C+            | 6   | AI                 | Analog input of channel C: noninverting input                                   |  |

| CH D-            | 7   | AI                 | Analog input of channel D: inverting input                                      |  |

| CH D+            | 8   | AI                 | Analog input of channel D: noninverting input                                   |  |

| REFIN D          | 9   | Al                 | Reference voltage input of channel D: pin for external reference voltage        |  |

| REFIN C          | 10  | AI                 | Reference voltage input of channel C: pin for external reference voltage        |  |

| AGND             | 11  | _                  | Analog ground                                                                   |  |

| AVDD             | 12  | Р                  | Analog power supply; nominal 5 V                                                |  |

| NC               | 13  | _                  | No connection; this pin is left unconnected                                     |  |

| $AV_{DD}$        | 14  | Р                  | Analog power supply; nominal 5 V                                                |  |

| AGND             | 15  | _                  | Analog ground                                                                   |  |

| CLKSEL           | 16  | 1                  | Clock select between internal clock (CLKSEL = 1) or external clock (CLKSEL = 0) |  |

| CLKIN            | 17  | I                  | External clock input                                                            |  |

| BV <sub>DD</sub> | 18  | Р                  | Digital interface power supply; from 2.7 V to 5.5 V                             |  |

| BGND             | 19  |                    | Interface ground                                                                |  |

| CLKOUT           | 20  | 0                  | System clock output                                                             |  |

Product Folder Links: ADS1204

(1) AI = analog input; AO = analog output; I = input; O = output; P = power supply.

Submit Documentation Feedback

### Pin Functions (continued)

| Р         | IN |                    |                                                                                      |  |

|-----------|----|--------------------|--------------------------------------------------------------------------------------|--|

| NAME NO.  |    | I/O <sup>(1)</sup> | DESCRIPTION                                                                          |  |

| OUT D     | 21 | 0                  | Bit stream from channel D modulator                                                  |  |

| OUT C     | 22 | 0                  | Bit stream from channel C modulator                                                  |  |

| OUT B     | 23 | 0                  | Bit stream from channel B modulator                                                  |  |

| OUT A     | 24 | 0                  | it stream from channel A modulator                                                   |  |

| NC        | 25 | _                  | No connection; this pin is left unconnected                                          |  |

| AGND      | 26 | _                  | Analog ground                                                                        |  |

| $AV_{DD}$ | 27 | Р                  | Analog power supply; nominal 5 V                                                     |  |

| REFOUT    | 28 | AO                 | Reference voltage output: output pin of the internal reference source; nominal 2.5 V |  |

| $AV_{DD}$ | 29 | Р                  | Analog power supply; nominal 5 V                                                     |  |

| AGND      | 30 | _                  | Analog ground                                                                        |  |

| REFIN B   | 31 | Al                 | Reference voltage input of channel B: pin for external reference voltage             |  |

| REFIN A   | 32 | AI                 | Reference voltage input of channel A: pin for external reference voltage             |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                               |                                            | MIN             | MAX             | UNIT |  |

|-----------------------------------------------|--------------------------------------------|-----------------|-----------------|------|--|

| Supply voltage                                | AV <sub>DD</sub> to AGND                   | -0.3            | 6               |      |  |

|                                               | BV <sub>DD</sub> to BGND                   | -0.3            | 6               | V    |  |

| Analog input voltage with respect to AGND     |                                            | AGND - 0.3      | $AV_{DD} + 0.3$ | V    |  |

| Reference input voltage with respect to AGND  |                                            | AGND - 0.3      | $AV_{DD} + 0.3$ | V    |  |

| Digital input voltage with respect to BGND    |                                            | BGND - 0.3      | $BV_{DD} + 0.3$ | V    |  |

| Ground voltage difference, AGND to BGND       |                                            |                 | ±0.3            | V    |  |

| Voltage differences, BV <sub>DD</sub> to AGND |                                            | -0.3            | 6               | V    |  |

| Input current to any pin ex                   | ccept supply                               |                 | ±10             | mA   |  |

| Power dissipation                             |                                            | See the Thermal | I Information   | Α    |  |

| T                                             | Operating virtual junction, T <sub>J</sub> | -40             | +150            |      |  |

| Temperature                                   | Storage, T <sub>stg</sub>                  | -65             | +150            | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±750  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

|                                                      |                    | MIN         | NOM | MAX     | UNIT |

|------------------------------------------------------|--------------------|-------------|-----|---------|------|

| Supply voltage, AVDD to AGND                         |                    | 4.75        | 5   | 5.25    | V    |

| Supply voltage, BVDD to BGND                         | Low-voltage levels | 2.7         |     | 3.6     | V    |

|                                                      | 5V logic levels    | 4.5         | 5   | 5.5     | V    |

| Reference input voltage                              | •                  | 0.5 2.5 2.6 |     | V       |      |

| Operating common-mode signal                         | nmon-mode signal   |             |     | $AV_DD$ | V    |

| Analog inputs                                        | +IN - (-IN)        | 0           |     | ±REFIN  | V    |

| External clock <sup>(1)</sup>                        | ,                  | 16          | 20  | 32      | MHz  |

| Operating free-air temperature range, T <sub>A</sub> |                    | -40         |     | +125    | °C   |

| Specified free-air temperature range,                | T <sub>A</sub>     | -40         |     | +105    | °C   |

(1) Analog performance is degraded at clock frequencies > 20 MHz; see the Typical Characteristics section for details.

#### 6.4 Thermal Information

|                      |                                              | ADS1204    |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RHB (VQFN) | UNIT |

|                      |                                              | 32 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 28.6       | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 17.0       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 9.7        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 9.7        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.7        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC package thermal metrics application report.

#### 6.5 Electrical Characteristics

over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = 5$  V,  $BV_{DD} = 3$  V, CH x+ = 0.5 V to 4.5 V, CH x- = 2.5 V, REFIN = REFOUT = internal 2.5 V, CLKIN = 20 MHz, and 16-bit sinc<sup>3</sup> filter with decimation by 256 (unless otherwise noted)

|                    | PARAMETER                                | TEST CONDITIONS                    | MIN TYP <sup>(1)</sup> | MAX    | UNIT   |

|--------------------|------------------------------------------|------------------------------------|------------------------|--------|--------|

| RESOLUT            | ΓΙΟΝ                                     |                                    |                        |        |        |

|                    | Resolution                               |                                    | 16                     |        | Bits   |

| DC ACCU            | IRACY                                    |                                    |                        | ,      |        |

| INII               | Integral linearity error <sup>(2)</sup>  |                                    | ±1                     | ±3     | LSB    |

| INL                | integral linearity error                 |                                    | ±0.001                 | ±0.005 | % FSR  |

|                    | Integral linearity metab                 |                                    |                        | ±6     | LSB    |

|                    | Integral linearity match                 |                                    |                        | ±0.009 | % FSR  |

| DNL                | Differential nonlinearity <sup>(3)</sup> |                                    |                        | ±1     | LSB    |

| Vos                | Input offset error                       |                                    | -1.4                   | ±3     | mV     |

|                    | Input offset error match                 |                                    |                        | ±2     | mV     |

| TCV <sub>OS</sub>  | Input offset error drift                 |                                    | ±2                     | ±8     | μV/°C  |

| G <sub>ERR</sub>   | Gain error <sup>(4)</sup>                | Referenced to V <sub>REF</sub>     | ±0.08                  | ±0.5   | % FSR  |

|                    | Gain error match                         |                                    | ±0.185                 | ±0.5   | % FSR  |

| TCG <sub>ERR</sub> | Gain error drift                         |                                    | ±2                     |        | ppm/°C |

| PSRR               | Power-supply rejection ratio             | 4.75 V < AV <sub>DD</sub> < 5.25 V | 78                     |        | dB     |

All typical values are at  $T_A = +25$ °C.

(4) Maximum values, including temperature drift, are specified over the full specified temperature range.

Integral nonlinearity is defined as the maximum deviation of the line through the end points of the specified input range of the transfer curve for CH x+ = -2 V to +2 V at 2.5 V, expressed either as the number of LSBs or as a percent of measured input range (4 V).

# **Electrical Characteristics (continued)**

over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = 5$  V,  $BV_{DD} = 3$  V, CH x+ = 0.5 V to 4.5 V, CH x- = 2.5 V, REFIN = REFOUT = internal 2.5 V, CLKIN = 20 MHz, and 16-bit  $sinc^3$  filter with decimation by 256 (unless otherwise noted)

|                       | PARAMETER                         | TEST CONDITIONS                                                                                   | MIN                  | TYP <sup>(1)</sup> | MAX                   | UNIT   |

|-----------------------|-----------------------------------|---------------------------------------------------------------------------------------------------|----------------------|--------------------|-----------------------|--------|

| ANALOG I              | NPUT                              |                                                                                                   |                      |                    |                       |        |

| FSR                   | Full-scale differential range     | (CH x+) - (CH x-); CH x- = 2.5 V                                                                  |                      |                    | ±2.5                  | V      |

|                       | Specified differential range      | (CH x+) - (CH x-); CH x- = 2.5 V                                                                  |                      |                    | ±2                    | V      |

|                       | Maximum operating input range (3) |                                                                                                   | 0                    |                    | $AV_{DD}$             | V      |

|                       | Input capacitance                 | Common-mode                                                                                       |                      | 1.5                | 55                    | pF     |

|                       | Input leakage current             | CLK turned off                                                                                    |                      |                    | ±1                    | nA     |

|                       | Differential input resistance     |                                                                                                   |                      | 100                |                       | kΩ     |

|                       | Differential input capacitance    |                                                                                                   |                      | 2.5                |                       | pF     |

|                       |                                   | At DC                                                                                             |                      | 100                |                       | -      |

| CMRR                  | Common-mode rejection ratio       | $V_{IN} = \pm 1.25 V_{PP}$ at 40 kHz                                                              |                      | 110                |                       | dB     |

| BW                    | Bandwidth                         | FS sine wave, –3 dB                                                                               |                      | 50                 |                       | MHz    |

| SAMPLING              | B DYNAMICS                        | ,                                                                                                 |                      |                    |                       |        |

|                       | Internal clock frequency          | CLKSEL = 1                                                                                        | 8                    | 10                 | 12                    | MHz    |

| CLKIN                 | External clock frequency          | CLKSEL = 0                                                                                        | 1                    | 20                 | 32                    | MHz    |

| AC ACCU               |                                   |                                                                                                   |                      |                    |                       |        |

|                       |                                   | $V_{IN} = \pm 2 V_{PP} \text{ at 5 kHz};$<br>-40°C \le T_A \le +85°C                              |                      | -96                | -88                   | dB     |

| THD                   | Total harmonic distortion         | $V_{IN} = \pm 2 V_{PP} \text{ at 5 kHz;}  -40^{\circ}\text{C} \le T_{A} \le +105^{\circ}\text{C}$ |                      | -96                | -96 -87               |        |

| SFDR                  | Spurious-free dynamic range       | $V_{IN} = \pm 2 V_{PP}$ at 5 kHz                                                                  | 92                   | 100                |                       | dB     |

| SNR                   | Signal-to-noise ratio             | V <sub>IN</sub> = ±2 V <sub>PP</sub> at 5 kHz                                                     | 86                   | 89                 |                       | dB     |

| SINAD                 | Signal-to-noise + distortion      | V <sub>IN</sub> = ±2 V <sub>PP</sub> at 5 kHz                                                     | 85                   | 89                 |                       | dB     |

|                       | Channel-to-channel isolation (3)  | V <sub>IN</sub> = ±2 V <sub>PP</sub> at 50 kHz                                                    |                      | 85                 |                       | dB     |

| ENOB                  | Effective number of bits          |                                                                                                   | 14                   | 14.5               |                       | Bits   |

| VOLTAGE               | REFERENCE OUTPUT                  |                                                                                                   |                      |                    |                       |        |

| V <sub>OUT</sub>      | Reference voltage output          |                                                                                                   | 2.450                | 2.5                | 2.550                 | V      |

| dV <sub>OUT</sub> /dT | Output voltage temperature drift  |                                                                                                   |                      | ±20                |                       | ppm/°C |

|                       | Outside a Name of State           | $f = 0.1$ Hz to 10 Hz, $C_L = 10 \mu F$                                                           |                      | 10                 |                       |        |

|                       | Output voltage noise              | $f = 10 \text{ Hz to } 10 \text{ kHz}, C_L = 10 \mu\text{F}$                                      |                      | 12                 |                       | μVrms  |

| PSRR                  | Power-supply rejection ratio      |                                                                                                   |                      | 60                 |                       | dB     |

| I <sub>OUT</sub>      | Output current                    |                                                                                                   |                      | 10                 |                       | μΑ     |

| I <sub>SC</sub>       | Short-circuit current             |                                                                                                   |                      | 0.5                |                       | mA     |

|                       | Turn-on settling time             | To 0.1% at $C_L = 0$                                                                              |                      | 100                |                       | μs     |

| VOLTAGE               | REFERENCE INPUT                   |                                                                                                   |                      |                    |                       |        |

| V <sub>IN</sub>       | Reference voltage input           |                                                                                                   | 0.5                  | 2.5                | 2.6                   | V      |

|                       | Reference input resistance        |                                                                                                   |                      | 100                |                       | ΜΩ     |

|                       | Reference input capacitance       |                                                                                                   |                      | 5                  |                       | pF     |

|                       | Reference input current           |                                                                                                   |                      |                    | 1                     | μΑ     |

| DIGITAL II            | NPUTS <sup>(5)</sup>              |                                                                                                   |                      |                    | 1                     |        |

|                       | Logic family                      |                                                                                                   | CMOS w               | ith Schmitt Trigg  | ger                   |        |

| V <sub>IH</sub>       | High-level input voltage          |                                                                                                   | $0.7 \times BV_{DD}$ | В                  | V <sub>DD</sub> + 0.3 | V      |

| V <sub>IL</sub>       | Low-level input voltage           |                                                                                                   | -0.3                 |                    | .3 × BV <sub>DD</sub> | V      |

| I <sub>IN</sub>       | Input current                     | V <sub>I</sub> = BV <sub>DD</sub> or GND                                                          |                      |                    | ±50                   | nA     |

| C <sub>I</sub>        | Input capacitance                 |                                                                                                   |                      | 5                  |                       | pF     |

<sup>(5)</sup> Applicable for 5.0-V nominal supply:  $BV_{DD}$  (min) = 4.5 V and  $BV_{DD}$  (max) = 5.5 V.

Submit Documentation Feedback

# **Electrical Characteristics (continued)**

over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = 5$  V,  $BV_{DD} = 3$  V, CH x+ = 0.5 V to 4.5 V, CH x- = 2.5 V, REFIN = REFOUT = internal 2.5 V, CLKIN = 20 MHz, and 16-bit  $sinc^3$  filter with decimation by 256 (unless otherwise noted)

|                  | PARAMETER                           | TEST CONDITIONS                                      | MIN TYP(               | 1) MAX                 | UNIT |

|------------------|-------------------------------------|------------------------------------------------------|------------------------|------------------------|------|

| DIGITAL          | L OUTPUTS <sup>(5)</sup>            |                                                      |                        | 1.                     |      |

|                  | Logic family                        |                                                      | СМО                    | S                      |      |

| V <sub>OH</sub>  | High-level output voltage           | $BV_{DD} = 4.5 \text{ V}, I_{OH} = -100 \mu\text{A}$ | 4.44                   |                        | V    |

| V <sub>OL</sub>  | Low-level output voltage            | BV <sub>DD</sub> = 4.5 V, I <sub>OL</sub> = 100 μA   |                        | 0.5                    | V    |

| Co               | Output capacitance                  |                                                      |                        | 5                      | pF   |

| C <sub>L</sub>   | Load capacitance                    |                                                      |                        | 30                     | pF   |

|                  | Data format                         |                                                      | Bit stream             | m                      |      |

| DIGITAL          | L INPUTS <sup>(6)</sup>             |                                                      |                        | <u>.</u>               |      |

|                  | Logic family                        |                                                      | LVCMO                  | S                      |      |

| V <sub>IH</sub>  | High-level input voltage            | BV <sub>DD</sub> = 3.6 V                             | 2                      | BV <sub>DD</sub> + 0.3 | V    |

| V <sub>IL</sub>  | Low-level input voltage             | BV <sub>DD</sub> = 2.7 V                             | -0.3                   | 0.8                    | V    |

| I <sub>IN</sub>  | Input current                       | V <sub>I</sub> = BV <sub>DD</sub> or GND             |                        | ±50                    | nA   |

| Cı               | Input capacitance                   |                                                      |                        | 5                      | pF   |

| DIGITAL          | L OUTPUTS <sup>(6)</sup>            |                                                      | 1                      | 1.                     |      |

|                  | Logic family                        |                                                      | LVCMO                  | S                      |      |

| V <sub>OH</sub>  | High-level output voltage           | $BV_{DD} = 2.7V$ , $I_{OH} = -100 \mu A$             | BV <sub>DD</sub> - 0.2 |                        | V    |

| V <sub>OL</sub>  | Low-level output voltage            | BV <sub>DD</sub> = 2.7 V, I <sub>OL</sub> = 100 μA   |                        | 0.2                    | V    |

| Co               | Output capacitance                  |                                                      |                        | 5                      | pF   |

| C <sub>L</sub>   | Load capacitance                    |                                                      |                        | 30                     | pF   |

|                  | Data format                         |                                                      | Bit stream             | m                      |      |

| POWER            | SUPPLY                              |                                                      | 1                      | 1.                     |      |

| $AV_{DD}$        | Analog supply voltage               |                                                      | 4.5                    | 5.5                    | V    |

| D) /             | De War I/O annual annual annual     | Low-voltage levels                                   | 2.7                    | 3.6                    | .,   |

| $BV_{DD}$        | Buffer I/O supply voltage           | 5-V logic levels                                     | 4.5                    |                        | V    |

| Al <sub>DD</sub> |                                     | CLKSEL = 1                                           | 22.                    |                        |      |

|                  | Analog operating supply current     | CLKSEL = 0                                           | 22.4 29                |                        | mA   |

| 5.               | 5 % 1/2                             | BV <sub>DD</sub> = 3 V, CLKOUT = 10 MHz              |                        | 4                      |      |

| $BI_{DD}$        | Buffer I/O operating supply current | BV <sub>DD</sub> = 5 V, CLKOUT = 10 MHz              |                        | mA                     |      |

|                  | Parama dia dia atta                 | CLKSEL = 0                                           | 122 145                |                        | mW   |

|                  | Power dissipation                   | CLKSEL = 1                                           | 112.                   |                        |      |

<sup>(6)</sup> Applicable for 3.0-V nominal supply:  $BV_{DD}$  (min) = 2.7 V and  $BV_{DD}$  (max) = 3.6 V.

Submit Documentation Feedback

Copyright © 2003–2020, Texas Instruments Incorporated

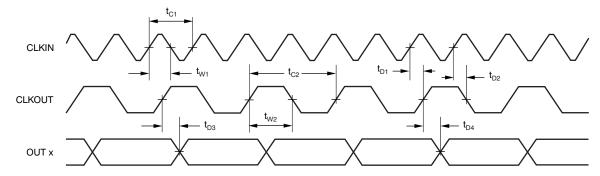

# 6.6 Timing Requirements: 5.0 V<sup>(1)</sup>

over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = 5$  V, and  $BV_{DD} = 5$  V (unless otherwise noted)

|                 |                                                           | MIN                 | MAX                  | UNIT |

|-----------------|-----------------------------------------------------------|---------------------|----------------------|------|

| t <sub>C1</sub> | CLKIN period                                              | 31.25               | 1000                 | ns   |

| t <sub>W1</sub> | CLKIN high time                                           | 10                  | t <sub>C1</sub> - 10 | ns   |

| t <sub>C2</sub> | CLKOUT period using internal oscillator (CLKSEL = 1)      | 83                  | 125                  | ns   |

|                 | CLKOUT period using external clock (CLKSEL = 0)           | 2 × t <sub>C1</sub> |                      | ns   |

| t <sub>W2</sub> | CLKOUT high time                                          | $(t_{C2} / 2) - 5$  | $(t_{C2}/2) + 5$     | ns   |

| t <sub>D1</sub> | CLKOUT rising edge delay after CLKIN rising edge          | 0                   | 10                   | ns   |

| t <sub>D2</sub> | CLKOUT falling edge delay after CLKIN rising edge         | 0                   | 10                   | ns   |

| t <sub>D3</sub> | Data valid delay after rising edge of CLKOUT (CLKSEL = 1) | $(t_{C2} / 4) - 8$  | $(t_{C2} / 4) + 8$   | ns   |

| t <sub>D4</sub> | Data valid delay after rising edge of CLKOUT (CLKSEL = 0) | $t_{W1} - 3$        | t <sub>W1</sub> + 7  | ns   |

<sup>(1)</sup> Applicable for 5.0-V nominal supply:  $BV_{DD}$  (min) = 4.5 V and  $BV_{DD}$  (max) = 5.5 V. All input signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of  $BV_{DD}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH}) / 2$ . See Figure 1.

# 6.7 Timing Requirements: 3.0 V<sup>(1)</sup>

over recommended operating free-air temperature range at  $-40^{\circ}$ C to  $+105^{\circ}$ C,  $AV_{DD} = 5$  V, and  $BV_{DD} = 3$  V (unless otherwise noted)

|                 |                                                           | MIN                 | MAX                  | UNIT |

|-----------------|-----------------------------------------------------------|---------------------|----------------------|------|

| t <sub>C1</sub> | CLKIN period                                              | 31.25               | 1000                 | ns   |

| t <sub>W1</sub> | CLKIN high time                                           | 10                  | t <sub>C1</sub> - 10 | ns   |

| t <sub>C2</sub> | CLKOUT period using internal oscillator (CLKSEL = 1)      | 83                  | 125                  | ns   |

|                 | CLKOUT period using external clock (CLKSEL = 0)           | 2 × t <sub>C1</sub> |                      | ns   |

| t <sub>W2</sub> | CLKOUT high time                                          | $(t_{C2} / 2) - 5$  | $(t_{C2} / 2) + 5$   | ns   |

| t <sub>D1</sub> | CLKOUT rising edge delay after CLKIN rising edge          | 0                   | 10                   | ns   |

| t <sub>D2</sub> | CLKOUT falling edge delay after CLKIN rising edge         | 0                   | 10                   | ns   |

| t <sub>D3</sub> | Data valid delay after rising edge of CLKOUT (CLKSEL = 1) | $(t_{C2} / 4) - 8$  | $(t_{C2} / 4) + 8$   | ns   |

| t <sub>D4</sub> | Data valid delay after rising edge of CLKOUT (CLKSEL = 0) | t <sub>W1</sub> - 3 | t <sub>W1</sub> + 7  | ns   |

(1) Applicable for 3.0V nominal supply:  $BV_{DD}$  (min) = 2.7V and  $BV_{DD}$  (max) = 3.6V. All input signals are specified with  $t_R = t_F = 5$ ns (10% to 90% of  $BV_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2. See Figure 1.

Figure 1. ADS1204 Timing Diagram

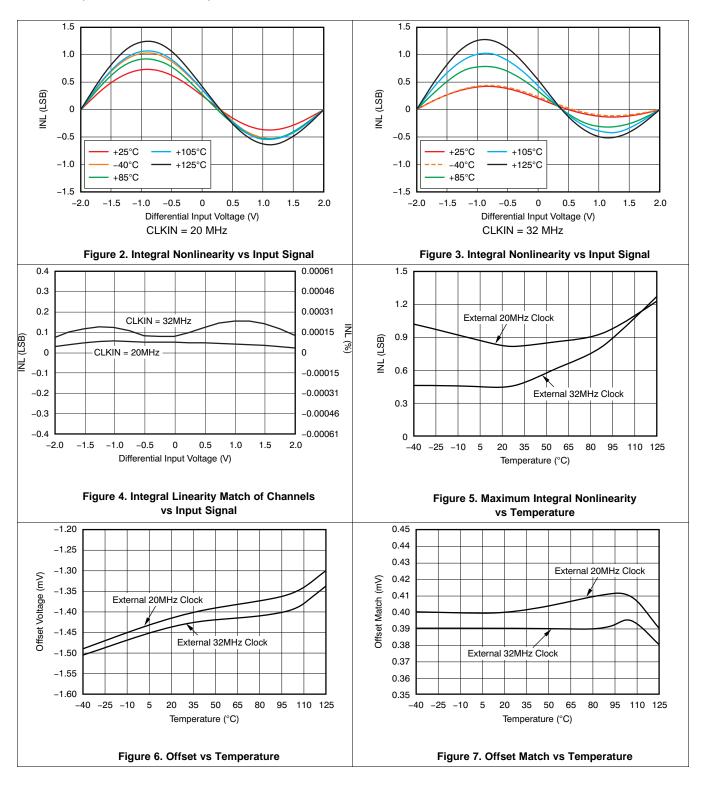

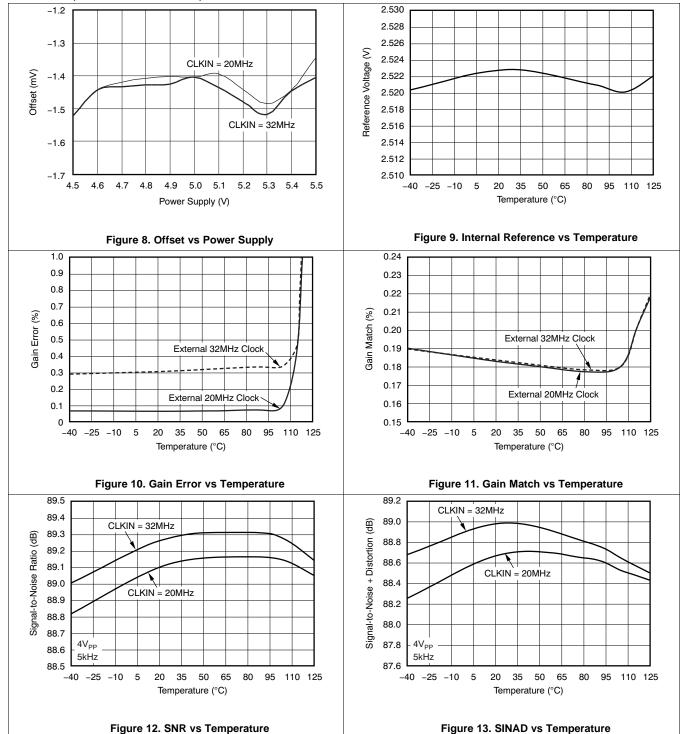

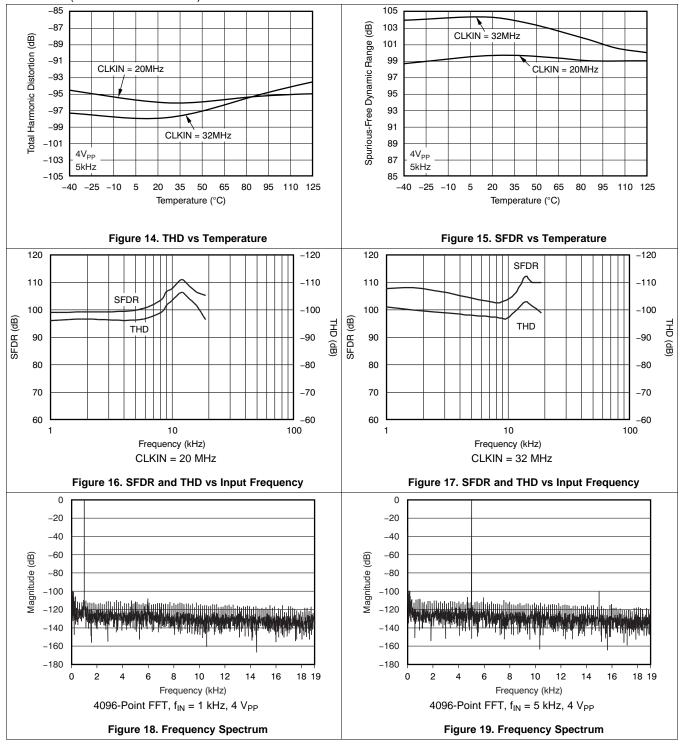

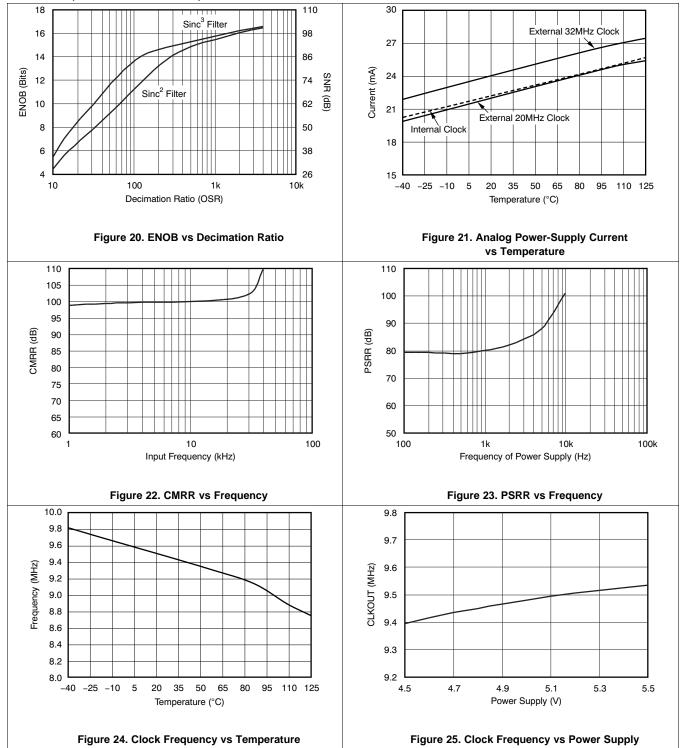

#### 6.8 Typical Characteristics

$AV_{DD} = 5 \text{ V}$ ,  $BV_{DD} = 3 \text{ V}$ , CH x+ = 0.5 V to 4.5 V, CH x- = 2.5 V, REFIN = external, CLKSEL = 0, and 16-bit  $sinc^3$  filter, with OSR = 256 (unless otherwise noted)

Submit Documentation Feedback

Copyright © 2003–2020, Texas Instruments Incorporated

# **Typical Characteristics (continued)**

$AV_{DD} = 5 \text{ V}$ ,  $BV_{DD} = 3 \text{ V}$ , CH x+ = 0.5 V to 4.5 V, CH x- = 2.5 V, REFIN = external, CLKSEL = 0, and 16-bit  $sinc^3$  filter, with OSR = 256 (unless otherwise noted)

Copyright © 2003–2020, Texas Instruments Incorporated

Product Folder Links: ADS1204

# **Typical Characteristics (continued)**

$AV_{DD} = 5 \text{ V}$ ,  $BV_{DD} = 3 \text{ V}$ , CH x+ = 0.5 V to 4.5 V, CH x- = 2.5 V, REFIN = external, CLKSEL = 0, and 16-bit  $sinc^3$  filter, with OSR = 256 (unless otherwise noted)

Submit Documentation Feedback

Copyright © 2003–2020, Texas Instruments Incorporated

# **Typical Characteristics (continued)**

$AV_{DD} = 5 \text{ V}$ ,  $BV_{DD} = 3 \text{ V}$ , CH x + = 0.5 V to 4.5 V, CH x - = 2.5 V, REFIN = external, CLKSEL = 0, and 16-bit  $sinc^3$  filter, with OSR = 256 (unless otherwise noted)

Copyright © 2003-2020, Texas Instruments Incorporated

# 7 Detailed Description

#### 7.1 Overview

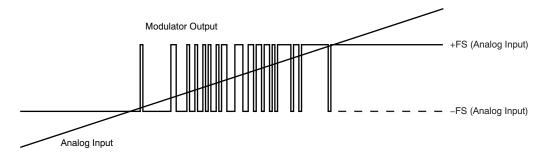

The ADS1204 is a four-channel, second-order, CMOS device with four delta-sigma ( $\Delta\Sigma$ ) modulators, designed for medium- to high-resolution A/D signal conversions from dc to 39 kHz (filter response –3 dB) if an oversampling ratio (OSR) of 64 is chosen. The output of the converter (OUTX) provides a stream of digital ones and zeros. The time average of this serial output is proportional to the analog input voltage.

The modulator shifts the quantization noise to high frequencies. A low-pass digital filter should be used at the output of the  $\Delta\Sigma$  modulator. The filter serves two functions. First, it filters out high-frequency noise. Second, the filter converts the 1-bit data stream at a high sampling rate into a higher-bit data word at a lower rate (decimation).

An application-specific integrated circuit (ASIC) or field-programmable gate array (FPGA) could be used to implement the digital filter. Figure 26 and Figure 27 illustrate typical application circuits with the ADS1204 connected to an FPGA.

The overall performance (that is, speed and accuracy) depends on the selection of an appropriate OSR and filter type. A higher OSR produces greater output accuracy while operating at a lower refresh rate. Alternatively, a lower OSR produces lower output accuracy, but operates at a higher refresh rate. This system allows flexibility with the digital filter design and is capable of A/D conversion results that have a dynamic range exceeding 100 dB with an OSR equal to 256.

Figure 26. Single-Ended Connection Diagram for the ADS1204  $\Delta\Sigma$  Modulator

Figure 27. Differential Connection Diagram for the ADS1204  $\Delta\Sigma$  Modulator

#### 7.2 Functional Block Diagram

## 7.3 Feature Description

The differential analog input of the ADS1204 is implemented with a switched-capacitor circuit. This circuit implements a second-order modulator stage, which digitizes the analog input signal into a 1-bit output stream. The clock source can be internal as well as external. Different frequencies for this clock allow for a variety of solutions and signal bandwidths. Every analog input signal is continuously sampled by the modulator and compared to a reference voltage that is applied to the REFINx pin. A digital stream, which accurately represents the analog input voltage over time, appears at the output of the corresponding converter.

#### **Feature Description (continued)**

#### 7.3.1 Analog Input Stage

#### 7.3.1.1 Analog Input

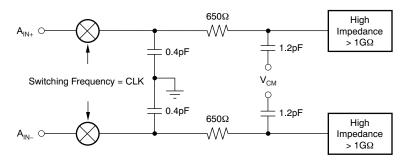

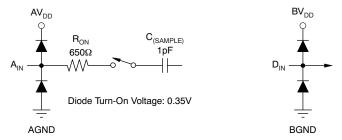

The topology of the analog inputs of ADS1204 is based on fully differential switched-capacitor architecture. This input stage provides the mechanism to achieve low system noise, high common-mode rejection (100 dB), and excellent power-supply rejection.

The input impedance of the analog input is dependent on the modulator clock frequency ( $f_{CLK}$ ), which is also the sampling frequency of the modulator. Figure 28 shows the basic input structure of one channel of the ADS1204. The relationship between the input impedance of the ADS1204 and the modulator clock frequency is shown in Equation 1:

$$Z_{IN} = \frac{100k\Omega}{f_{MOD}/10MHz}$$

(1)

The input impedance becomes a consideration in designs where the source impedance of the input signal is high. This high impedance may cause degradation in gain, linearity, and THD. The importance of this effect depends on the desired system performance. There are two restrictions on the analog input signals, CH x+ and CH x-. If the input voltage exceeds the range (GND - 0.3 V) to ( $V_{DD}$  + 0.3 V), the input current must be limited to 10 mA because the input protection diodes on the front end of the converter will begin to turn on. In addition, the linearity and the noise performance of the device are ensured only when the differential analog voltage resides within  $\pm 2$  V (with  $V_{REF}$  as a midpoint); however, the FSR input voltage is  $\pm 2.5$  V.

Figure 28. Input Impedance of the ADS1204

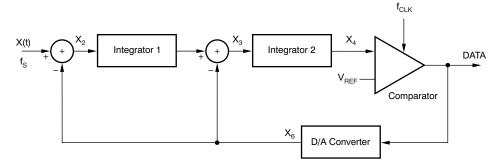

#### 7.3.1.2 Modulator

The ADS1204 can be operated in two modes. When CKLSEL = 1, the four modulators operate using the internal clock, which is fixed at 20 MHz. When CKLSEL = 0, the modulators operate using an external clock. In both modes, the clock is divided by two internally and functions as the modulator clock. The frequency of the external clock can vary from 1 MHz to 32 MHz to adjust for the clock requirements of the application.

The modulator topology is fundamentally a second-order, switched-capacitor,  $\Delta\Sigma$  modulator, such as the one conceptualized in Figure 29. The analog input voltage and the output of the 1-bit digital-to-analog converter (DAC) are differentiated, providing analog voltages at X2 and X3. The voltages at X2 and X3 are presented to their individual integrators. The output of these integrators progresses in a negative or positive direction. When the value of the signal at X4 equals the comparator reference voltage, the output of the comparator switches from negative to positive, or positive to negative, depending on its original state. When the output value of the comparator switches from high to low or vice versa, the 1-bit DAC responds on the next clock pulse by changing its analog output voltage at X6, causing the integrators to progress in the opposite direction. The feedback of the modulator to the front end of the integrators forces the value of the integrator output to track the average of the input.

Figure 29. Block Diagram of the Second-Order Modulator

## 7.3.2 Digital Output

A differential input signal of 0 V will ideally produce a stream of ones and zeros that are high 50% of the time and low 50% of the time. A differential input of 2 V produces a stream of ones and zeros that are high 80% of the time. A differential input of -2 V produces a stream of ones and zeros that are high 20% of the time. The input voltage versus the output modulator signal is shown in Figure 30.

Figure 30. Analog Input versus Modulator Output of the ADS1204

#### 7.3.3 Equivalent Input Circuits

Figure 31 shows equivalent circuits for the analog input and digital outputs.

Equivalent Analog Input Circuit

Equivalent Digital Input Circuit

NOTE: The thermal pad is internally connected to the substrate. This pad can be connected to the analog ground or left floating. Keep the thermal pad separate from the digital ground, if possible.

Figure 31. Equivalent Input Circuits

Submit Documentation Feedback

#### 7.4 Device Functional Modes

The system clock of the ADS1204 is 20 MHz by default. The system clock can be provided either from the internal 20MHz RC oscillator or from an external clock source. For this purpose, the CLKIN pin is provided; it is controlled by the mode setting, CLKSEL.

The system clock is divided by two for the modulator clock. Therefore, the default clock frequency of the modulator is 10MHz. With a possible external clock range of 1MHz to 32MHz, the modulator operates between 500 kHz and 16 MHz.

# 8 Application and Implementation

#### **NOTE**

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The analog signal connected to the input of the  $\Delta\Sigma$  modulator is converted using the clock signal applied to the modulator. The result of the conversion, or modulation, is generated and sent to the OUTx pin from the  $\Delta\Sigma$  modulator. In most applications where a direct connection is realized between the  $\Delta\Sigma$  modulator and an ASIC or FPGA (each with an implemented filter), the two standard signals per modulator (CLKOUT and OUTx) are provided from the modulator. The output clock signal is equal for all four modulators. If CLKSEL = 1, CLKIN must always be set either high or low.

#### 8.1.1 Filter Usage

The modulator generates only a bitstream, which does not output a digital word like an A/D converter. In order to output a digital word equivalent to the analog input voltage, the bitstream must be processed by a digital filter.

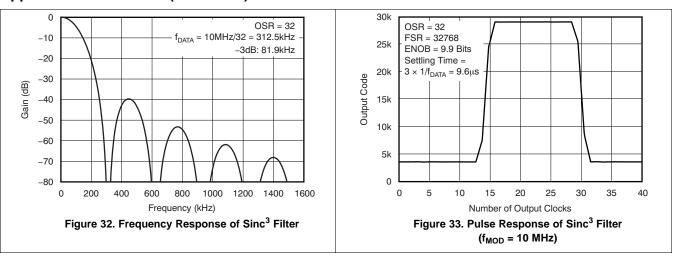

A very simple filter, built with minimal effort and hardware, is the sinc<sup>3</sup> filter shown in Equation 2:

$$H(z) = \left(\frac{1 - z^{-OSR}}{1 - z^{-1}}\right)^{2}$$

(2)

This filter provides the best output performance at the lowest hardware size (for example, a count of digital gates). For oversampling ratios in the range of 16 to 256, this is a good choice. All the characterizations in the data sheet are also done using a  $sinc^3$  filter with an oversampling ratio of OSR = 256 and an output word width of 16 bits.

In a sinc<sup>3</sup> filter response (see Figure 32 and Figure 33), the location of the first notch occurs at the frequency of output data rate  $f_{DATA} = f_{CLK}$  / OSR. The -3-dB point is located at half the Nyquist frequency or  $f_{DATA}$  / 4. For some applications, it may be necessary to use another filter type for better frequency response.

# TEXAS INSTRUMENTS

#### **Application Information (continued)**

This performance can be improved, for example, by a cascaded filter structure. The first decimation stage can be a sinc<sup>3</sup> filter with a low OSR and the second stage a high-order filter.

For more information, see the Combining the ADS1202 with an FPGA Digital Filter for Current Measurement in Motor Control Applications application note, available for download at www.ti.com.

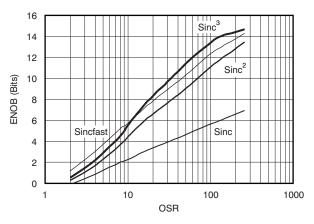

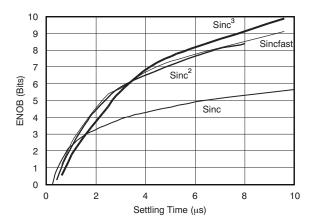

The effective number of bits (ENOB) can be used to compare the performance of A/D converters and  $\Delta\Sigma$  modulators. Figure 34 shows the ENOB of the ADS1204 with different filter types. In this data sheet, the ENOB is calculated from the SNR as shown in Equation 3:

$$SNR = 1.76dB + 6.02dB \times ENOB$$

(3)

Figure 34. Measured ENOB vs OSR

In motor control applications, a very fast response time for overcurrent detection is required. There is a constraint between 1 µs and 5 µs with 3 bits to 7 bits resolution. The time for full settling is dependent on the filter order. Therefore, the full settling of the sinc<sup>3</sup> filter needs three data clocks and the sinc<sup>2</sup> filter needs two data clocks. The data clock is equal to the modulator clock divided by the OSR. For overcurrent protection, filter types other than sinc<sup>3</sup> might be a better choice. A simple example is a sinc<sup>2</sup> filter. Figure 35 compares the settling time of different filter types. The Sincfast is a modified sinc<sup>2</sup> filter as Equation 4 shows:

$$H(z) = \left(\frac{1 - z^{-OSR}}{1 - z^{-1}}\right)^{2} (1 + z^{-2 \times OSR})$$

(4)

# **Application Information (continued)**

Figure 35. Measured ENOB versus Settling Time

For more information, see the Combining the ADS1202 with an FPGA Digital Filter for Current Measurement in Motor Control Applications application note, available for download at www.ti.com.

## 9 Power Supply Recommendations

The ADS1204 requires two power supplies,  $AV_{DD}$  for analog, and  $BV_{DD}$  for digital. The analog supply is a fixed voltage of 5 V ± 5%, whereas the digital supply can be set within a range of 2.7 V to 5.5 V.  $BV_{DD}$  determines the I/O voltage for the interface. If  $AV_{DD}$  equals  $BV_{DD}$ , the two supplies can be tied together.

## 9.1 Power-Supply Sequencing

The supplies can be sequenced in any order, but in no case must any analog or digital input exceed the respective analog or digital power-supply voltage and current limits. In particular, inputs to the ADS1204, such as CH x+, CH x-, and CLKIN, should not be present before the power supply is on. Violating this condition could cause latch-up. If these signals are present before the supply is on, series resistors should be used to limit the input current to a maximum of 10 mA.

Wait approximately 600 µs after all power supplies are stabilized before communicating with the device to allow the power-on reset process to complete.

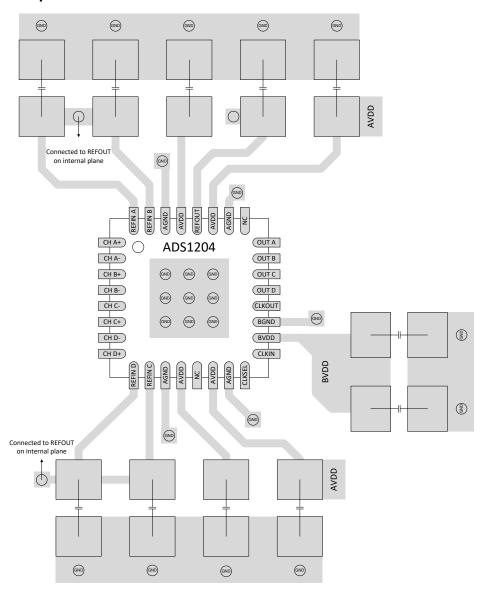

#### 9.2 Power-Supply Decoupling

Good decoupling practices must be used for the ADS1204 and for all components in the design. All decoupling capacitors, specifically the 0.1- $\mu$ F ceramic capacitors, must be placed as close as possible to the pin being decoupled. A 1- $\mu$ F and 10- $\mu$ F capacitor, in parallel with the 0.1- $\mu$ F ceramic capacitor, can be used to decouple AV<sub>DD</sub> to AGND as well as BV<sub>DD</sub> to BGND. At least one 0.1- $\mu$ F ceramic capacitor must be used to decouple every AV<sub>DD</sub> to AGND and BV<sub>DD</sub> to BGND, as well as for the digital supply on each digital component.

In cases where both the analog and digital I/O supplies share the same supply source, an RC filter of 10  $\Omega$  and 0.1  $\mu$ F can be used to help reduce the noise in the analog supply.

# 10 Layout

## 10.1 Layout Guidelines

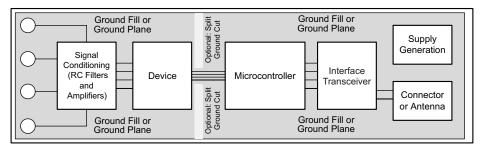

Employing best design practices is recommended when laying out a printed-circuit board (PCB) for both analog and digital components. This recommendation generally means that the layout separates analog components [such as ADCs, amplifiers, references, digital-to-analog converters (DACs), and analog MUXs] from digital components [such as microcontrollers, complex programmable logic devices (CPLDs), field-programmable gate arrays (FPGAs), radio frequency (RF) transceivers, universal serial bus (USB) transceivers, and switching regulators]. Figure 36 shows an example of good component placement. Although Figure 36 provides a good example of component placement, the best placement for each application is unique to the geometries, components, and PCB fabrication capabilities employed. That is, there is no single layout that is perfect for every design and careful consideration must always be used when designing with any analog component.

Figure 36. System Component Placement

The following basic recommendations for layout of the ADS1204 help achieve the best possible performance of the ADC.

- Separate analog and digital signals. To start, partition the board into analog and digital sections where the layout permits. Routing digital lines away from analog lines prevents digital noise from coupling back into analog signals.

- The ground plane can be split into an analog plane (AGND) and digital plane (DGND), but is not necessary. Place digital signals over the digital plane, and analog signals over the analog plane. As a final step in the layout, the split between the analog and digital grounds must be connected to together at the ADC.

- Fill void areas on signal layers with ground fill.

- Provide good ground return paths. Signal return currents flow on the path of least impedance. If the ground

plane is cut or has other traces that block the current from flowing right next to the signal trace, another path

must be found to return to the source and complete the circuit. If forced into a larger path, the chance that the

signal radiates increases. Sensitive signals are more susceptible to EMI interference.

- Use bypass capacitors on supplies to reduce high-frequency noise. Do not place vias between bypass capacitors and the active device. Placing the bypass capacitors on the same layer as close to the active device yields the best results.

- Consider the resistance and inductance of the routing. Often, traces for the inputs have resistances that react

with the input bias current and cause an added error voltage. Reducing the loop area enclosed by the source

signal and the return current reduces the inductance in the path. Reducing the inductance reduces the EMI

pickup and reduces the high-frequency impedance at the input of the device.

- Watch for parasitic thermocouples in the layout. Dissimilar metals going from each analog input to the sensor

can create a parasitic thermocouple that can add an offset to the measurement. Differential inputs must be

matched for both the inputs going to the measurement source.

- Analog inputs with differential connections must have a capacitor placed differentially across the inputs. Best

input combinations for differential measurements use adjacent analog input lines (such as CH A+, CH Athrough CH D+ and CH D-). The differential capacitors must be of high quality. The best ceramic chip

capacitors are COG (NPO) that have stable properties and low noise characteristics.

# 10.2 Layout Example

Figure 37. ADS1204 Layout Example

Copyright © 2003–2020, Texas Instruments Incorporated

Submit Documentation Feedback

# 11 Device and Documentation Support

#### 11.1 Receiving Notification of Documentation Updates

To receive notification of documentation updates, navigate to the device product folder on ti.com. In the upper right corner, click on *Alert me* to register and receive a weekly digest of any product information that has changed. For change details, review the revision history included in any revised document.

#### 11.2 Support Resources

TI E2E™ support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 11.3 Trademarks

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

### 11.4 Electrostatic Discharge Caution

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### 11.5 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

# **PACKAGE OPTION ADDENDUM**

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| ADS1204IRHBR     | ACTIVE     | VQFN         | RHB                | 32   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 105   | ADS<br>1204I            | Samples |

| ADS1204IRHBT     | ACTIVE     | VQFN         | RHB                | 32   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 105   | ADS<br>1204l            | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

5 x 5, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224745/A

# RHB (S-PVQFN-N32)

# PLASTIC QUAD FLATPACK NO-LEAD

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) Package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-220.

# RHB (S-PVQFN-N32)

# PLASTIC QUAD FLATPACK NO-LEAD

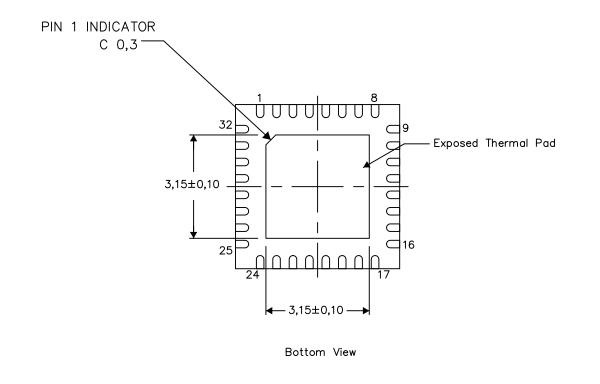

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Exposed Thermal Pad Dimensions

4206356-3/AC 05/15

NOTE: A. All linear dimensions are in millimeters

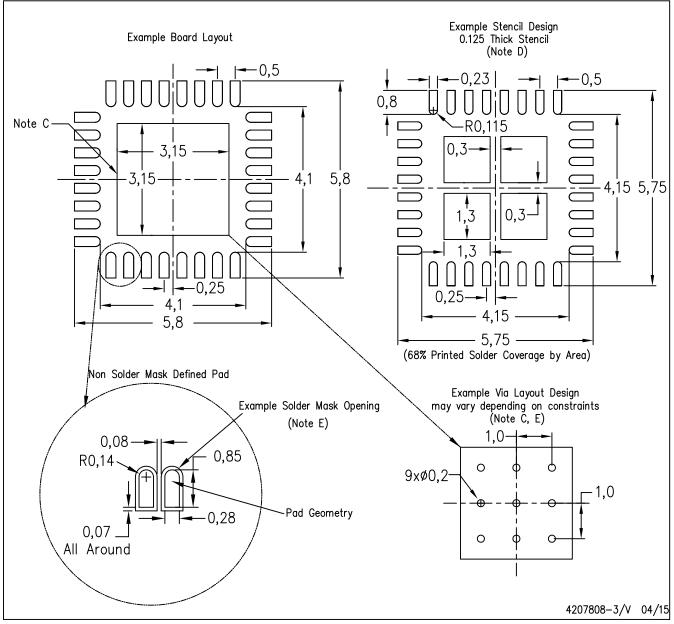

# RHB (S-PVQFN-N32)

# PLASTIC QUAD FLATPACK NO-LEAD

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- E. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for any larger diameter vias placed in the thermal pad.

## **IMPORTANT NOTICE AND DISCLAIMER**

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated