## **ON Semiconductor**

### Is Now

To learn more about onsemi™, please visit our website at www.onsemi.com

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/ or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application,

# Self-Protected Low Side Driver with In-Rush Current Management

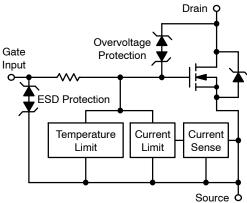

The NCV8411 is a three terminal protected Low–Side Smart Discrete FET. The protection features include Delta Thermal Shutdown, overcurrent, overtemperature, ESD and integrated Drain to Gate clamping for over voltage protection. The device also offers fault indication via the gate pin. This device is suitable for harsh automotive environments.

#### **Features**

- Short Circuit Protection with In-Rush Current Management

- Delta Thermal Shutdown

- Thermal Shutdown with Automatic Restart

- Over Voltage Protection

- Integrated Clamp for Over Voltage Protection and Inductive Switching

- ESD Protection

- dV/dt Robustness

- Analog Drive Capability (Logic Level Input)

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q101 Qualified and PPAP Capable

- These Devices are Pb-Free and are RoHS Compliant

### **Typical Applications**

- Switch a Variety of Resistive, Inductive and Capacitive Loads

- Can Replace Electromechanical Relays and Discrete Circuits

- Automotive / Industrial

Figure 1. Block Diagram

1

#### ON Semiconductor®

#### www.onsemi.com

| V <sub>DSS</sub><br>(Clamped) | R <sub>DS(ON)</sub> TYP | I <sub>D</sub> MAX<br>(Limited) |

|-------------------------------|-------------------------|---------------------------------|

| 42 V                          | 23 mΩ @ 10 V            | 45 A                            |

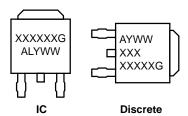

CASE 369C STYLE 2

#### **MARKING DIAGRAM**

| 1 = Gate   | 1 🗁 | AYWW  | h |

|------------|-----|-------|---|

| 2 = Drain  | 2 🗖 | NCV   |   |

| 3 = Source | 3 🗀 | 8411G | V |

A = Assembly Location

Y = Year WW = Work Week G = Pb-Free Package

#### **ORDERING INFORMATION**

| Device       | Package           | Shipping <sup>†</sup> |

|--------------|-------------------|-----------------------|

| NCV8411DTRKG | DPAK<br>(Pb-Free) | 2500/Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

**Table 1. MAXIMUM RATINGS**

| Rating                                                                                                           | Symbol                                                      | Value (min)      | Unit  |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------|-------|

| Drain-to-Source Voltage Internally Clamped                                                                       | V <sub>DSS</sub>                                            | 42               | V     |

| Drain-to-Gate Voltage Internally Clamped                                                                         | $V_{DG}$                                                    | 42               | V     |

| Gate-to-Source Voltage                                                                                           | V <sub>GS</sub>                                             | ±14              | V     |

| Drain Current - Continuous                                                                                       | I <sub>D</sub>                                              | Internally Lin   | nited |

| Total Power Dissipation  @ T <sub>A</sub> = 25°C (Note 1)  @ T <sub>A</sub> = 25°C (Note 2)                      | P <sub>D</sub>                                              | 1.3<br>2.7       | W     |

| Thermal Resistance Junction-to-Case Junction-to-Ambient (Note 1) Junction-to-Ambient (Note 2)                    | R <sub>thJC</sub><br>R <sub>thJA</sub><br>R <sub>thJA</sub> | 0.65<br>95<br>45 | °C/W  |

| Single Pulse Inductive Load Switching Energy (Note 3) $(L = 120 \text{ mH}, T_{J(start)} = 150^{\circ}\text{C})$ | E <sub>AS</sub>                                             | 600              | mJ    |

| Load Dump Voltage (VGS = 0 and 10 V, RG = 2 $\Omega$ , RL = 3 $\Omega$ ) (Note 4)                                | U <sub>S</sub> *                                            | 55               | V     |

| Operating Junction Temperature                                                                                   | T <sub>J</sub>                                              | -40 to 150       | °C    |

| Storage Temperature                                                                                              | T <sub>storage</sub>                                        | -55 to 150       | °C    |

| ESD CHARACTERISTICS (Note 3)                                                                                     |                                                             |                  | -     |

| Electro-Static Discharge Capability<br>Human Body Model (HBM)                                                    | ESD                                                         | 4                | kV    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- Mounted onto a 2" square FR4 board (100 sq mm, 1 oz. Cu, steady state)

Mounted onto a 2" square FR4 board (645 sq mm, 1 oz. Cu, steady state)

- 3. Not tested in production.

- Load Dump Test B (with centralized load dump suppression) according to ISO16750–2 standard. Guaranteed by design. Not tested in production. Passed Class C according to ISO16750–1.

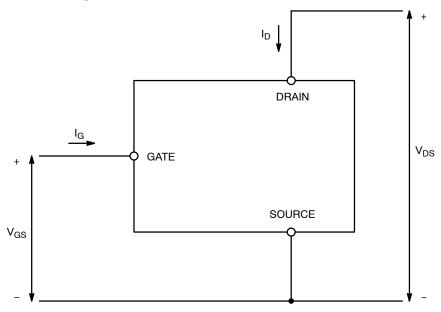

Figure 2. Voltage and Current Convention

Table 2. ELECTRICAL CHARACTERISTICS (T  $_{J}$  =  $25^{\circ}C$  unless otherwise noted)

| Characteristic                                | Test Conditions                                                                           | Symbol                              | Min | Тур  | Max  | Unit  |

|-----------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------|-----|------|------|-------|

| OFF CHARACTERISTICS                           |                                                                                           |                                     |     |      |      |       |

| Drain-to-Source Clamped                       | $V_{GS} = 0 \text{ V}, I_D = 250 \mu\text{A}$                                             | V <sub>(BR)DSS</sub>                | 42  | 46   | 50   | V     |

| Breakdown Voltage                             | $V_{GS} = 0 \text{ V, } I_D = 250 \mu\text{A,}$<br>$T_J = 150^{\circ}\text{C (Note 5)}$   |                                     | 42  | 44   | 50   |       |

| Zero Gate Voltage Drain Current               | V <sub>DS</sub> = 32 V, V <sub>GS</sub> = 0 V                                             | I <sub>DSS</sub>                    | -   | 1.5  | 5    | μΑ    |

|                                               | V <sub>DS</sub> = 32 V, V <sub>GS</sub> = 0 V,<br>T <sub>J</sub> = 150°C (Note 5)         |                                     | -   | 5.5  | -    |       |

| Gate Input Current                            | $V_{GS} = 5 \text{ V}, V_{DS} = 0 \text{ V}$                                              | $I_{GSS}$                           | -   | 50   | 100  | μΑ    |

| ON CHARACTERISTICS                            |                                                                                           |                                     |     |      |      |       |

| Gate Threshold Voltage                        | $V_{GS} = V_{DS}$ , $I_D = 1.2 \text{ mA}$                                                | V <sub>GS(th)</sub>                 | 1.0 | 1.8  | 2.5  | V     |

| Threshold Temperature Coefficient             | $V_{GS} = V_{DS}$ , $I_D = 1.2 \text{ mA (Note 5)}$                                       |                                     | -   | 5    | -    | mV/°C |

| Static Drain-to-Source                        | $V_{GS} = 10 \text{ V}, I_D = 5 \text{ A}, T_J = 25^{\circ}\text{C}$                      | R <sub>DS(ON)</sub>                 | -   | 23   | 29   | mΩ    |

| On Resistance                                 | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 5 A,<br>T <sub>J</sub> = 150°C (Note 5)          |                                     | -   | 43   | 55   |       |

|                                               | $V_{GS} = 5 \text{ V}, I_D = 5 \text{ A}, T_J = 25^{\circ}\text{C}$                       |                                     | -   | 28   | 34   | 1     |

|                                               | V <sub>GS</sub> = 5 V, I <sub>D</sub> = 5 A,<br>T <sub>J</sub> = 150°C (Note 5)           |                                     | -   | 50   | 60   |       |

| Source Drain Forward On Voltage               | $I_S = 5 A, V_{GS} = 0 V$                                                                 | $V_{SD}$                            | -   | 0.8  | 1.1  | V     |

| SWITCHING CHARACTERISTICS (No                 | ote 5)                                                                                    |                                     |     |      |      |       |

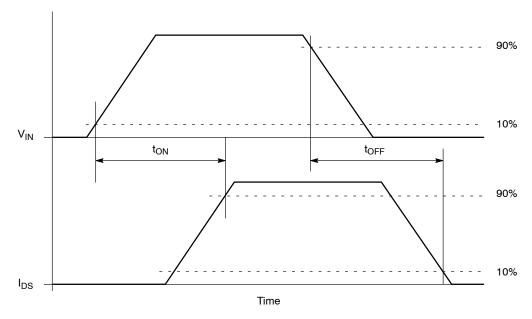

| Turn-On Time (10% $V_{GS}$ to 90% $I_D$ )     | $V_{GS} = 0 \text{ V to 5 V},$                                                            | t <sub>ON</sub>                     | -   | 29   | 50   | μs    |

| Turn-Off Time (90% $V_{GS}$ to 10% $I_D$ )    | $V_{DS} = 12 \text{ V}, I_{D} = 1 \text{ A}$                                              | t <sub>OFF</sub>                    | -   | 53   | 150  | 1     |

| Turn-On Time (10% $V_{GS}$ to 90% $I_D$ )     | $V_{GS} = 0 \text{ V to } 10 \text{ V},$                                                  | t <sub>ON</sub>                     | -   | 14   | 25   |       |

| Turn-Off Time (90% $V_{GS}$ to 10% $I_{D}$ )  | $V_{DS} = 12 \text{ V}, I_D = 1 \text{ A}$                                                | t <sub>OFF</sub>                    | ı   | 80   | 180  |       |

| Slew Rate On (80% $V_{DS}$ to 50% $V_{DS}$ )  | $V_{GS} = 0 \text{ V to } 10 \text{ V},$                                                  | $-dV_{DS}/dt_{ON}$                  | -   | 1.52 | 2.5  | V/μs  |

| Slew Rate Off (50% $V_{DS}$ to 80% $V_{DS}$ ) | $V_{DD} = 12 \text{ V}, R_L = 4.7 \Omega$                                                 | dV <sub>DS</sub> /dt <sub>OFF</sub> | -   | 0.71 | 0.85 |       |

| SELF PROTECTION CHARACTERIST                  | rics                                                                                      |                                     |     |      |      |       |

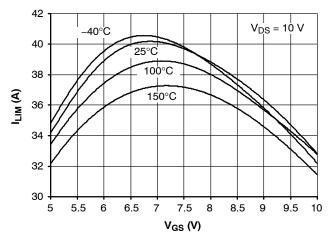

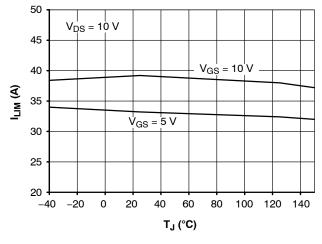

| Current Limit                                 | $V_{GS} = 5 \text{ V}, V_{DS} = 10 \text{ V}$                                             | I <sub>LIM</sub>                    | 29  | 33   | 40   | Α     |

|                                               | $V_{GS} = 5 \text{ V}, V_{DS} = 10 \text{ V},$<br>$T_J = 150^{\circ}\text{C (Note 5)}$    |                                     | 27  | 31   | 37   |       |

|                                               | V <sub>GS</sub> = 10 V, V <sub>DS</sub> = 10 V (Note 5)                                   |                                     | 23  | 34   | 46   |       |

|                                               | $V_{GS} = 10 \text{ V}, V_{DS} = 10 \text{ V},$<br>$T_{J} = 150^{\circ}\text{C (Note 5)}$ |                                     | 23  | 33   | 46   |       |

| Temperature Limit (Turn-Off)                  | V <sub>GS</sub> = 5 V (Note 5)                                                            | T <sub>LIM(OFF)</sub>               | 150 | 170  | 185  | °C    |

| Thermal Hysteresis                            |                                                                                           | $\Delta T_{LIM(ON)}$                | -   | 10   | _    | 1     |

| Temperature Limit (Turn-Off)                  | V <sub>GS</sub> = 10 V (Note 5)                                                           | T <sub>LIM(OFF)</sub>               | 150 | 180  | 200  |       |

| Thermal Hysteresis                            |                                                                                           | $\Delta T_{LIM(ON)}$                | _   | 10   | _    |       |

| GATE INPUT CHARACTERISTICS (N                 | ote 5)                                                                                    |                                     |     |      |      |       |

| Device ON Gate Input Current –                | $V_{GS} = 5 \text{ V}, V_{DS} = 10 \text{ V}, I_D = 1 \text{ A}$                          | I <sub>GON</sub>                    | -   | 50   | 100  | μΑ    |

| Normal Operation                              | V <sub>GS</sub> = 10 V, V <sub>DS</sub> = 10 V, I <sub>D</sub> = 1 A                      |                                     | 200 | 318  | 500  |       |

| Device ON Gate Input Current –                | $V_{GS} = 5 \text{ V}, V_{DS} = 10 \text{ V}, I_D = 0 \text{ A}$                          | $I_{GTL}$                           | _   | 633  | 900  |       |

| Thermal Limit                                 | $V_{GS} = 10 \text{ V}, V_{DS} = 10 \text{ V}, I_D = 0 \text{ A}$                         |                                     | _   | 1470 | 2000 |       |

| Device ON Gate Input Current –                | $V_{GS} = 5 \text{ V}, V_{DS} = 10 \text{ V}$                                             | I <sub>GCL</sub>                    | -   | 245  | 600  |       |

| Current Limit                                 | $V_{GS} = 10 \text{ V}, V_{DS} = 10 \text{ V}$                                            |                                     | -   | 1121 | 1500 |       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

5. Not tested in production.

10000 T<sub>J(start)</sub> = 25°C 1000 T<sub>J(start)</sub> = 150°C 100 L (mH)

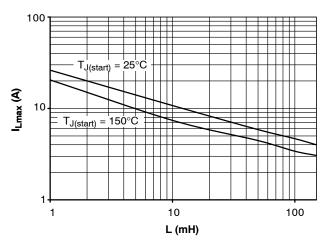

Figure 3. Single Pulse Maximum Switch-off Current vs. Load Inductance

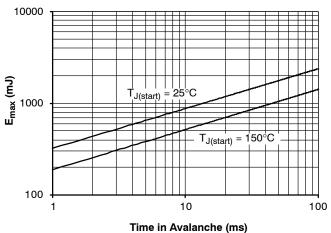

Figure 4. Single Pulse Maximum Switching Energy vs. Load Inductance

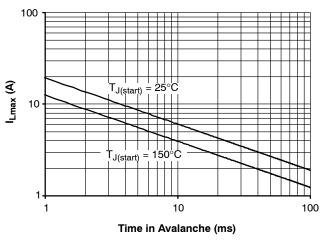

Figure 5. Single Pulse Maximum Inductive Switch-off Current vs. Time in Avalanche

Figure 6. Single Pulse Maximum Inductive Switching Energy vs. Time in Avalanche

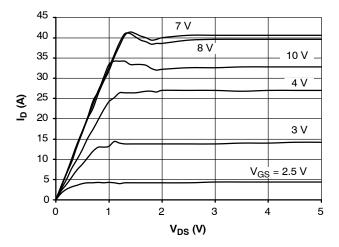

Figure 7. On-state Output Characteristics at 25°C

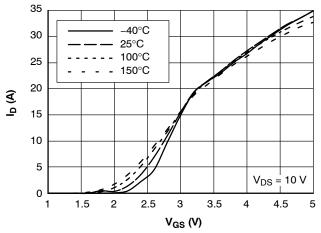

Figure 8. Transfer Characteristics

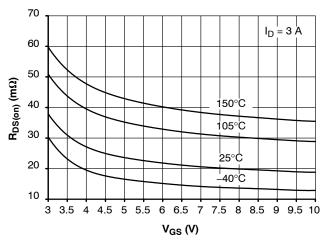

Figure 9. R<sub>DS(on)</sub> vs. Gate-Source Voltage

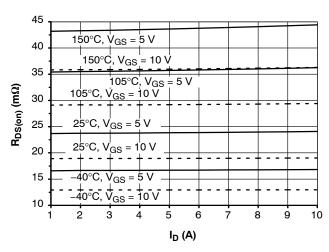

Figure 10. R<sub>DS(on)</sub> vs. Drain Current

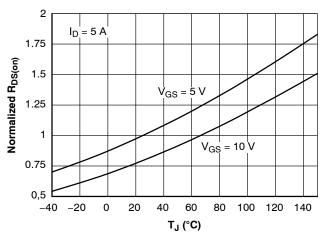

Figure 11. Normalized R<sub>DS(on)</sub> vs. Temperature

Figure 12. Current Limit vs. Gate-Source Voltage

Figure 13. Current Limit vs. Junction Temperature

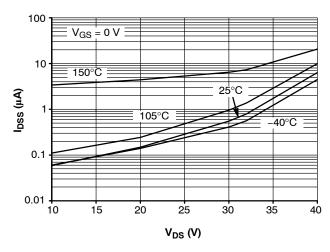

Figure 14. Drain-to-Source Leakage Current

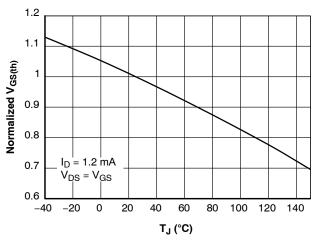

Figure 15. Normalized Threshold Voltage vs. Temperature

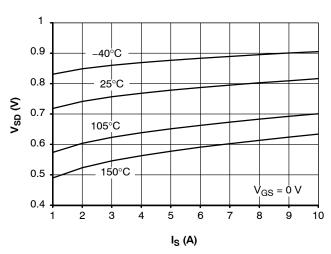

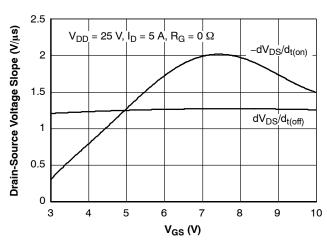

Figure 16. Source-Drain Diode Forward Characteristics

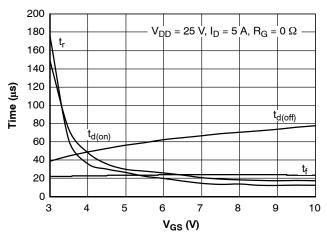

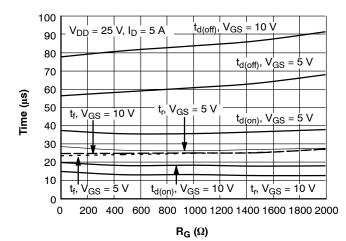

Figure 17. Resistive Load Switching Time vs.

Gate-Source Voltage

Figure 18. Resistive Load Switching Drain-Source Voltage Slope vs. Gate-Source Voltage

Figure 19. Resistive Load Switching Time vs.

Gate Resistance

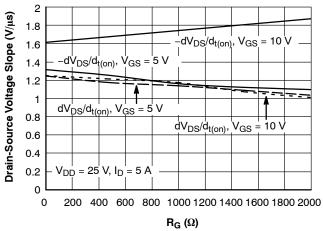

Figure 20. Drain-Source Voltage Slope during Turn On and Turn Off vs. Gate Resistance

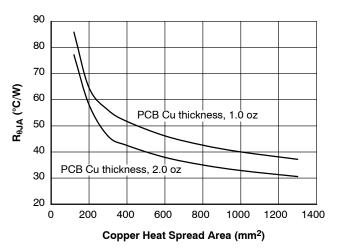

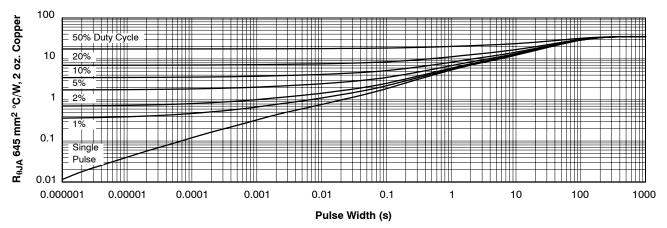

Figure 21.  $R_{\theta JA}$  vs. Copper Area

Figure 22. Transient Thermal Resistance

#### APPLICATION INFORMATION

#### **Circuit Protection Features**

The NCV8411 has three main protections. Current Limit, Thermal Shutdown and Delta Thermal Shutdown. These protections establish robustness of the NCV8411.

#### **Current Limit and Short Circuit Protection**

The NCV8411 has current sense element. In the event that the drain current reaches designed current limit level, integrated Current Limit protection establishes its constant level.

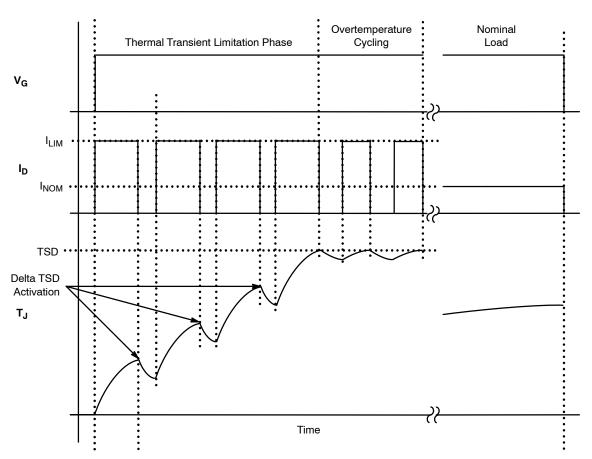

#### **Delta Thermal Shutdown**

Delta Thermal Shutdown (DTSD) Protection increases higher reliability of the NCV8411. DTSD consist of two independent temperature sensors – cold and hot sensors. The

NCV8411 establishes a slow junction temperature rise by sensing the difference between the hot and cold sensors. ON/OFF output cycling is designed with hysteresis that results in a controlled saw tooth temperature profile (Figure 23). The die temperature slowly rises (DTSD) until the absolute temperature shutdown (TSD) is reached around 175°C.

#### **Thermal Shutdown with Automatic Restart**

Internal Thermal Shutdown (TSD) circuitry is provided to protect the NCV8411 in the event that the maximum junction temperature is exceeded. When activated at typically 175°C, the NCV8411 turns off. This feature is provided to prevent failures from accidental overheating.

#### **TEST CIRCUITS AND WAVEFORMS**

Figure 23. Overload Protection Behavior

### TEST CIRCUITS AND WAVEFORMS

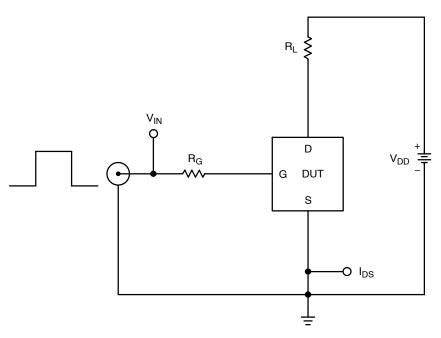

Figure 24. Resistive Load Switching Test Circuit

Figure 25. Resistive Load Switching Waveforms

### TEST CIRCUITS AND WAVEFORMS

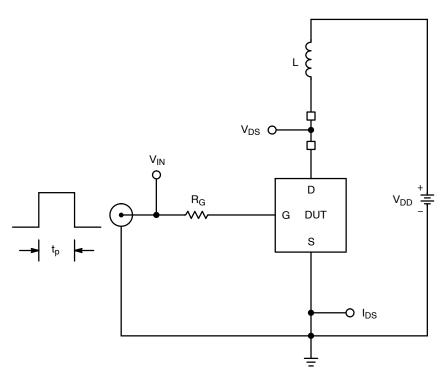

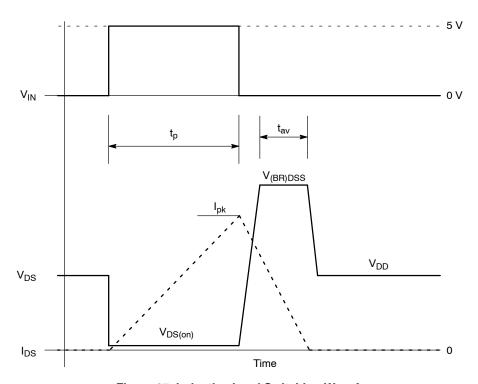

Figure 26. Inductive Load Switching Test Circuit

Figure 27. Inductive Load Switching Waveform

ROTATED 90° CW

STYLE 1:

STYLE 2:

**DATE 21 JUL 2015**

- IOTES. 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. 2. CONTROLLING DIMENSION: INCHES. 3. THERMAL PAD CONTOUR OPTIONAL WITHIN DI-

- MENSIONS b3, L3 and Z.

Jimensions b And E DO NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.006 INCHES PER SIDE.

MENSIONS D AND E ARE DETERMINED AT THE

- OUTERMOST EXTREMES OF THE PLASTIC BODY.

6. DATUMS A AND B ARE DETERMINED AT DATUM

- 7. OPTIONAL MOLD FEATURE.

|     | INCHES |       | MILLIM   | IETERS |

|-----|--------|-------|----------|--------|

| DIM | MIN    | MAX   | MIN      | MAX    |

| Α   | 0.086  | 0.094 | 2.18     | 2.38   |

| A1  | 0.000  | 0.005 | 0.00     | 0.13   |

| b   | 0.025  | 0.035 | 0.63     | 0.89   |

| b2  | 0.028  | 0.045 | 0.72     | 1.14   |

| b3  | 0.180  | 0.215 | 4.57     | 5.46   |

| С   | 0.018  | 0.024 | 0.46     | 0.61   |

| c2  | 0.018  | 0.024 | 0.46     | 0.61   |

| D   | 0.235  | 0.245 | 5.97     | 6.22   |

| E   | 0.250  | 0.265 | 6.35     | 6.73   |

| е   | 0.090  | BSC   | 2.29     | BSC    |

| Н   | 0.370  | 0.410 | 9.40     | 10.41  |

| L   | 0.055  | 0.070 | 1.40     | 1.78   |

| L1  | 0.114  | REF   | 2.90 REF |        |

| L2  | 0.020  | BSC   | 0.51 BSC |        |

| L3  | 0.035  | 0.050 | 0.89     | 1.27   |

| L4  |        | 0.040 | 1.01     |        |

| Z   | 0.155  |       | 3.93     |        |

#### **GENERIC MARKING DIAGRAM\***

XXXXXX = Device Code = Assembly Location Α = Wafer Lot L

Υ = Year WW = Work Week G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking.

### В L3 Ζ Ո DETAIL A NOTE 7 **BOTTOM VIEW** Cb2 е SIDE VIEW | $\oplus$ | 0.005 (0.13) lacktriangle C **TOP VIEW** Z Ħ L2 GAUGE C SEATING PLANE **BOTTOM VIEW** Α1 ALTERNATE CONSTRUCTIONS **DETAIL A**

| 3. EMITTER     | 3. SOURCE            | <ol> <li>ANODE</li> <li>CATHODE</li> </ol> | 3. GATE                                                            | 3. CATHODE                                                        |

|----------------|----------------------|--------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------|

| 4. COLLECTOR   | 4. DRAIN             |                                            | 4. ANODE                                                           | 4. ANODE                                                          |

| 3. GATE 3. EMI | LECTOR 2.<br>TTER 3. | N/C PIN CATHODE ANODE                      | E 9:<br>1. ANODE<br>2. CATHODE<br>3. RESISTOR ADJUST<br>4. CATHODE | STYLE 10:<br>PIN 1. CATHODE<br>2. ANODE<br>3. CATHODE<br>4. ANODE |

STYLE 4:

STYLE 5:

STYLE 3:

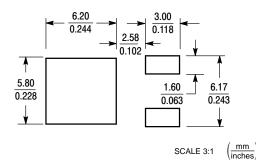

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DESCRIPTION:     | DPAK SINGLE GAUGE SURFACE MOUNT |                                                                      | PAGE 1 OF 2 |

|------------------|---------------------------------|----------------------------------------------------------------------|-------------|

| NEW STANDARD:    | REF TO JEDEC TO-252             | "CONTROLLED COPY" in red.                                            |             |

| STATUS:          | ON SEMICONDUCTOR STANDARD       | accessed directly from the Document versions are uncontrolled except |             |

| DOCUMENT NUMBER: | 98AON10527D                     |                                                                      |             |

| <b>DOCUMENT</b> | NUMBER: |

|-----------------|---------|

| 98AON10527      | 7D      |

PAGE 2 OF 2

|       | <del>,</del>                                                                                                                           |             |

|-------|----------------------------------------------------------------------------------------------------------------------------------------|-------------|

| ISSUE | REVISION                                                                                                                               | DATE        |

| 0     | RELEASED FOR PRODUCTION. REQ. BY L. GAN                                                                                                | 24 SEP 2001 |

| Α     | ADDED STYLE 8. REQ. BY S. ALLEN.                                                                                                       | 06 AUG 2008 |

| В     | ADDED STYLE 9. REQ. BY D. WARNER.                                                                                                      | 16 JAN 2009 |

| С     | ADDED STYLE 10. REQ. BY S. ALLEN.                                                                                                      | 09 JUN 2009 |

| D     | RELABELED DRAWING TO JEDEC STANDARDS. ADDED SIDE VIEW DETAIL A. CORRECTED MARKING INFORMATION. REQ. BY D. TRUHITTE.                    | 29 JUN 2010 |

| E     | ADDED ALTERNATE CONSTRUCTION BOTTOM VIEW. MODIFIED DIMENSIONS b2 AND L1. CORRECTED MARKING DIAGRAM FOR DISCRETE. REQ. BY I. CAMBALIZA. | 06 FEB 2014 |

| F     | ADDED SECOND ALTERNATE CONSTRUCTION BOTTOM VIEW. REQ. BY K. MUSTAFA.                                                                   | 21 JUL 2015 |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

|       |                                                                                                                                        |             |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor and see no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative