# Triple Output I<sup>2</sup>C Controlled RGB LED Driver

The NCP5623B mixed analog circuit is a triple output LED driver dedicated to the RGB illumination or backlight LCD display.

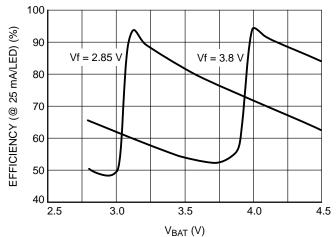

The built—in DC/DC converter is based on a high efficient charge pump structure with operating mode 1x and 2x. It provides a 94% peak efficiency. The tiny package makes the device suitable for room limited portable applications.

#### **Features**

- 2.7 to 5.5 V Input Voltage Range

- RGB Function Fully Supported

- Programmable Integrated Gradual Dimming

- 90 mA Output Current Capability

- 94% Peak Efficiency

- Built-in Short Circuit Protection

- Provides Three Independent LED Drives

- Support I<sup>2</sup>C Protocol

- Embedded OVP / Open Load Protection

- This is a Pb-Free Device

# **Typical Applications**

- Multicolor Illuminations

- Portable Back Light

- Digital Cellular Phone Camera Photo Flash

- LCD and Key Board Simultaneous Drive

1

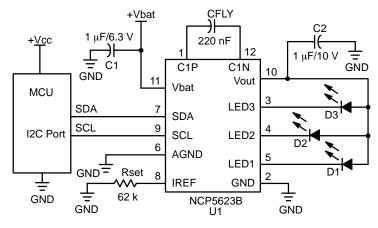

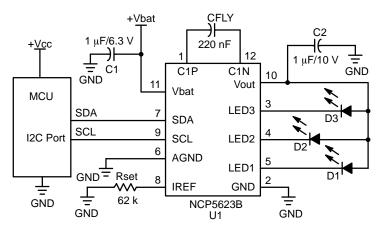

Figure 1. Typical Multiple White LED Driver

# ON Semiconductor®

www.onsemi.com

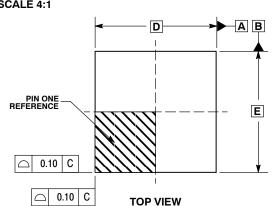

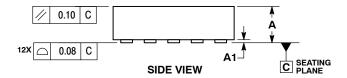

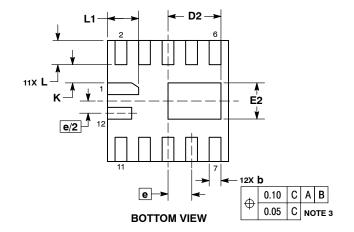

LLGA12 MU SUFFIX CASE 513AA

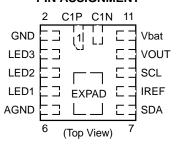

# **PIN ASSIGNMENT**

#### MARKING DIAGRAM

GV = Specific Device Code

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device        | Package             | Shipping <sup>†</sup> |

|---------------|---------------------|-----------------------|

| NCP5623BMUTBG | LLGA12<br>(Pb-Free) | 3000/Tape & Reel      |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

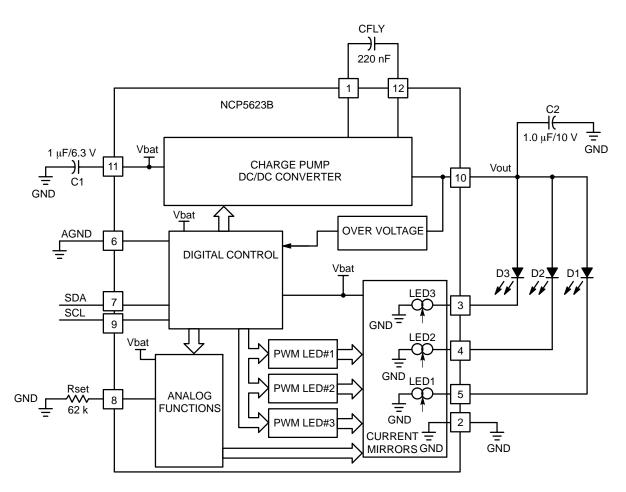

Figure 2. Simplified Block Diagram

# **PIN ASSIGNMENT**

| PIN | Name             | Туре              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | C1P              | POWER             | One side of the external charge pump capacitor (C <sub>FLY</sub> ) is connected to this pin, associated with C1N, pin 12 (Note 1).                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2   | GND              | POWER             | This pin is the GROUND signal for the analog and digital blocks and must be connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3   | LED3             | INPUT,<br>POWER   | This pin sinks to ground and monitors the current flowing into the LED3, intended to be used in illumination application (Note 2). The Anode of the associated LED shall be connected to the Vout pin.                                                                                                                                                                                                                                                                                                                                                                           |

| 4   | LED2             | INPUT,<br>POWER   | This pin sinks to ground and monitors the current flowing into the LED2, intended to be used in illumination application (Note 2). The Anode of the associated LED shall be connected to the Vout pin.                                                                                                                                                                                                                                                                                                                                                                           |

| 5   | LED1             | INPUT,<br>POWER   | This pin sinks to ground and monitors the current flowing into the LED1, intended to be used in illumination application (Note 2).                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6   | AGND             | ANALOG<br>GROUND  | This pin copies the Analog Ground and must be connected to the system ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7   | SDA              | INPUT,<br>DIGITAL | This pin carries the data provided by the I <sup>2</sup> C protocol. The content of the SDA byte is used to program the mode of operation and to set up the output current (Note 1).                                                                                                                                                                                                                                                                                                                                                                                             |

| 8   | I <sub>REF</sub> | INPUT,<br>ANALOG  | This pin provides the reference current, based on the internal band–gap voltage reference, to control the output current flowing in the LED. A 1% tolerance, or better, resistor shall be used to get the highest accuracy of the LED biases. An external current mirror can be used to bias this pin to dynamically set up the I–LED peak current.  In no case shall the voltage at I <sub>REF</sub> pin be forced either higher or lower than the 600 mV provided by the internal reference.                                                                                   |

| 9   | SCL              | INPUT,<br>DIGITAL | This pin carries the I <sup>2</sup> C clock to control the Charge Pump converter and to set up the output current. The SCL clock is associated with the SDA signal.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10  | VOUT             | OUTPUT,<br>POWER  | This pin provides the output voltage supplied by the Charge Pump converter. The Vout pin must be bypassed by 1 $\mu$ F ceramic capacitor located as close as possible to the V <sub>OUT</sub> pin to properly bypass the output voltage to ground. The circuit shall not operate without such bypass capacitor connected across the Vout pin and Ground (Note 1).  The output voltage is internally clamped to 5.5 V maximum in the event of a no load situation. On the other hand, the output current is limited to 40 mA (typical) in the event of a short circuit to ground. |

| 11  | VBAT             | INPUT,<br>POWER   | This pin is the input Battery voltage to supply the analog and digital blocks. The pin must be decoupled to ground by a 1µF or higher ceramic capacitor (Note 1).                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12  | C1N              | POWER             | One side of the external charge pump capacitor (C <sub>FLY</sub> ) is connected to this pin, associated with C1P, pin 1 (Note 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| -   | EXPAD            | GROUND            | EXPAD is not physically connected to the die. To optimize power dissipation, EXPAD must be connected to the system (PCB) power ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Using low ESR ceramic capacitor, X5R type, is mandatory to optimize the Charge Pump efficiency and to reduce the EMI.

The peak current is 37 mA for each LED, the total charge pump output DC current being limited to 75 mA.

### **MAXIMUM RATINGS**

| Symbol                                                 | Rating                                                                                                                                    | Value                       | Unit               |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------|

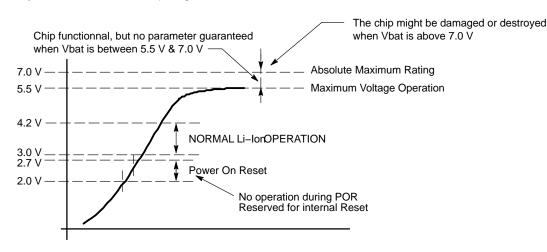

| V <sub>BAT</sub>                                       | Power Supply (see Figure 3)                                                                                                               | -0.3 < Vbat < 7.0           | V                  |

| Vout                                                   | Output Power Supply                                                                                                                       | 7.0                         | V                  |

| SDA, SCL,<br>SHDI2C                                    | Digital Input Voltage Digital Input Current                                                                                               | –0.3 < V < V <sub>BAT</sub> | V<br>mA            |

| ESD                                                    | Human Body Model: R = 1500 $\Omega$ , C = 100 pF (Note 3) Machine Model                                                                   | 2<br>200                    | kV<br>V            |

| P <sub>D</sub><br>R <sub>θJC</sub><br>R <sub>θJA</sub> | LLGA12 package Power Dissipation @ T <sub>A</sub> = +85°C (Note 4) Thermal Resistance Junction to Case Thermal Resistance Junction to Air | 200<br>51<br>200            | mW<br>°C/W<br>°C/W |

| T <sub>A</sub>                                         | Operating Ambient Temperature Range                                                                                                       | -40 to +85                  | °C                 |

| T <sub>J</sub>                                         | Operating Junction Temperature Range                                                                                                      | -40 to +125                 | °C                 |

| T <sub>Jmax</sub>                                      | Maximum Junction Temperature                                                                                                              | +150                        | °C                 |

| T <sub>stg</sub>                                       | Storage Temperature Range                                                                                                                 | −65 to +150                 | °C                 |

|                                                        | Latch-up current maximum rating per JEDEC standard: JESD78.                                                                               | ±100                        | mA                 |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

<sup>3.</sup> This device series contains ESD protection and exceeds the following tests: Human Body Model (HBM) ±2.0 kV per JEDEC standard: JESD22–A114 Machine Model (MM) ±200 V per JEDEC standard: JESD22–A115.

The maximum package power dissipation limit must not be exceeded.

Moisture Sensitivity Level (MSL): 1 per IPC/JEDEC standard: J–STD–020A.

# **POWER SUPPLY SECTION:**

(Typical values are referenced to  $T_A$  = +25°C, Min & Max values are referenced -40°C to +85°C ambient temperature, unless otherwise noted), operating conditions 2.85 V < Vbat < 5.5 V, unless otherwise noted.

| Pin   | Symbol             | Rating                                                                                                                            | Min      | Тур          | Max | Unit |

|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------|--------------|-----|------|

| 11    | V <sub>bat</sub>   | Power Supply                                                                                                                      | 2.7      |              | 5.5 | V    |

| 10    | l <sub>out</sub>   | Continuous DC current in the load, PWM = 100%<br>@ $V_f$ = 3.4 V, $V_{bat}$ = 3.0 V<br>@ $V_f$ = 3.4 V, 3.3 V < $V_{bat}$ < 5.5 V | 55<br>75 |              |     | mA   |

| 10    | Isch               | Continuous Output Short Circuit Current 2.85 V < Vbat < 4.2 V                                                                     |          | 45           | 90  | mA   |

| 10    | Vout               | Output Voltage Compliance (OVP)                                                                                                   | 4.4      |              | 5.7 | V    |

| 10    | Tstart             | DC/DC Start time (Cout = 1 $\mu$ F)<br>3.0 V < Vbat = nominal < 5.5 V<br>From last acknowledgement bit to full load operation     |          | 150          |     | μs   |

| 10    | I <sub>stdb</sub>  | Stand By Current 3.0 V $\leq$ V <sub>bat</sub> $\leq$ 4.2 V, lout = 0 mA                                                          |          | 0.8          | 1.0 | μА   |

| 10    | I <sub>op</sub>    | Operating Current, @ lout = 0 mA, $3.0 \text{ V} \le \text{Vbat} \le 4.2 \text{ V}$                                               |          | 350          |     | μА   |

| 3,4,5 | I <sub>TOL</sub>   | RGB Output Current Tolerance<br>@Vbat = 3.6 V, I <sub>LED</sub> = 10 mA<br>-25°C < Ta < 85°C                                      |          | ±3           |     | %    |

| 3,4,5 | I <sub>MATCH</sub> | RGB Output Current LED Matching  @Vbat = 3.6 V, I <sub>LED</sub> = 5.0 mA                                                         |          | ±0.5         |     | %    |

|       | Fpwr               | Charge Pump Operating Frequency -40°C < Ta < 85°C                                                                                 | 0.8      | 1            | 1.2 | MHz  |

|       | E <sub>PWR</sub>   | Efficiency @ Vbat = 3.6 V - LED1 to LED3 = 5 mA, Vf = 2.8 V (Total = 15 mA) - LED1 to LED3 = 20 mA, Vf = 3.2 V (Total = 60 mA)    |          | 94.2<br>92.3 |     | %    |

#### **ANALOG SECTION:**

(Typical values are referenced to  $T_A = +25^{\circ}C$ , Min & Max values are referenced  $-40^{\circ}C$  to  $+85^{\circ}C$  ambient temperature, unless otherwise noted), operating conditions 2.85 V < Vbat < 5.5 V, unless otherwise noted.

| Pin   | Symbol                                                    | Rating                                    | Min | Тур  | Max | Unit |

|-------|-----------------------------------------------------------|-------------------------------------------|-----|------|-----|------|

| 8     | I <sub>REF</sub>                                          | Reference current @Vref = 600 mV (Note 7) | 3   | 12.5 | 20  | μΑ   |

| 8     | $V_{REF}$                                                 | Reference Voltage (Note 7)                | -3% | 600  | +3% | mV   |

|       | I <sub>LEDR</sub>                                         | Reference Current (IREF) current ratio    |     | 2400 |     |      |

| 8     | Rset External Reference current setting resistor (Note 6) |                                           | 30  | 48   | 200 | kΩ   |

| 3,4,5 | F <sub>PWM</sub>                                          | Internal PWM Frequency (Note 8)           |     | 2.1  |     | kHz  |

- 6. The overall output current tolerance depends upon the accuracy of the external resistor. Using 1% or better resistor is recommended.

- The external circuit must not force the I<sub>REF</sub> pin voltage either higher or lower than the 600 mV specified. The system is optimized with a 12.5 μA reference current.

- 8. This parameter, derived from the 1 MHz clock, is guaranteed by design, not tested in production.

### **DIGITAL PARAMETERS SECTION:**

(Typical values are referenced to  $T_A = +25^{\circ}C$ , Min & Max values are referenced  $-40^{\circ}C$  to  $+85^{\circ}C$  ambient temperature, unless otherwise noted), operating conditions 2.85 V < Vbat < 5.5 V, unless otherwise noted.

| Pin | Symbol           | Rating                                                                    | Min | Тур | Max              | Unit |

|-----|------------------|---------------------------------------------------------------------------|-----|-----|------------------|------|

| 9   | F <sub>SCL</sub> | Input I <sup>2</sup> C clock frequency                                    |     |     | 400              | kHz  |

| 7,9 | V <sub>IH</sub>  | Positive going Input High Voltage Threshold,<br>SDA, SCL signals (Note 9) | 1.6 |     | V <sub>BAT</sub> | V    |

| 7,9 | V <sub>IL</sub>  | Negative going Input High Voltage Threshold,<br>SDA, SCL signals (Note 9) | 0   |     | 0.4              | V    |

NOTE: Digital inputs undershoot ≤ 0.30 V to ground, Digital inputs overshoot < 0.30 V to V<sub>BAT</sub>

- 9. Test guaranteed by design and fully characterized, not implemented in production.

- 10. The fall time  $-t_f$  for both SCL and SDA input signals must be 120 ns maximum.

Figure 3. Understanding Integrated Circuit Voltage Limitations

# DC/DC OPERATION

The converter is based on a charge pump technique to generate a DC voltage capable to supply the RGB LED load. The system regulates the current flowing into each LED, not the DC Vout value, by means of internal current mirrors associated with the diodes.

Consequently, Vout = Vbat \* Mode, with Mode = 1 or Mode = 2, the extra voltage Vout – Vf being sustained by the current mirror structure.

The average forward current of each LED can be independently programmed (by means of the associated PWM) to achieve the RGB function. The maximum LED current, setup by the external current setting resistor connected across IREF pin and Ground, is associated to the digital content of the  $I^2C$  register (see Table 1). This peak current applies to the three LED simultaneously, but, thanks to the RGB function, the average output current of each LED is controlled by the independent PWM controllers. Consequently, the luminosity of each RGB diode can be independently adjusted to cope with a given illumination need. Since the peak current is constant, the color of the RGB diodes is the one defined by the specifications of each individual LED.

The built—in OVP circuit continuously monitors the V<sub>out</sub> voltage and stops the converter when the voltage is above 5.7 V. The converter resumes to normal operation when the voltage drops below 4.4 V (no latch—up mechanism). Consequently, the chip can operate under no load conditions during any test procedures.

#### LOAD CURRENT CALCULATION

The load current is derived from the 600 mV reference voltage provided by the internal Band Gap associated to the external resistor connected across  $I_{REF}$  pin and Ground. Note: due to the internal structure of this pin, no voltage, either downward or upward, shall be forced at the  $I_{REF}$  pin.

The reference current is multiplied by the constant k=2400 to yield the output load current. Since the reference voltage is based on a temperature compensated Band Gap, a tight tolerance resistor will provide a very accurate load current. The resistor is calculated from the Ohm's law ( $R_{set}=Vref/I_{REF}$ ) and a more practical equation can be arranged to define the resistor value for a given maximum output current:

$$R_{set} = (Vref*k)/Iout$$

[1]

$R_{set} = (0.6*2400)/Iout$

$$R_{set} = 1440/Iout$$

[2]

Since the Iref to ILED ratio is very high, it is strongly recommended to set up the reference current at  $12.5 \,\mu\text{A}$  to

optimize the tolerance of the output current. Although it is possible to use higher or lower value, as defined in the analog section, a 48 k $\Omega$  / 1% resistor will provide the best compromise, the dimming being performed by the appropriate PWM registers.

On the other hand, care must be observed to avoid leakage current flowing into either the IREF pin or the current setting resistor.

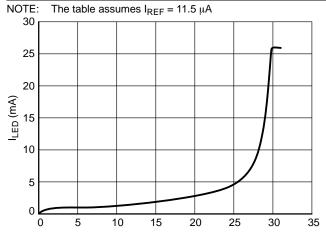

Finally, for any desired ILED current, the curve provided Figure 4 can be recalculated according to the equation:

$$ILED = \frac{IREF \cdot k}{31 - n}$$

(eq. 1)

ILED =

$$\frac{\frac{\text{Vref}}{\text{Rset}} \cdot 2400}{31 - n}$$

(eq. 2)

with:  $n = \text{step value} @ 1 \le n \le 30$

Rset = Current setting resistor

k = internal multiplier constant = 2400

Note: n = 0 forces ILED to zero

n = 30 and n = 31 yields the same LED current

#### LOAD CONNECTION

The primary function of the NCP5623B is to control three LED arranged in the RGB color structure (reference OSRAM LATB G66x). The brightness of each LED is independently controlled by a set of dedicated PWM structure embedded into the silicon chip. The peak current, identical for each LED, is programmable by means of the I<sup>2</sup>C data byte. With 32 steps per PWM, the chip provides 32768 colors hue in a standard display.

Moreover, a built—in gradual dimming provides a smooth brightness transition for any current level, in both Upward and Downward direction. The dimming function is controlled by the  $I^2C$  interface: see Table 2.

The NCP5623B chip is capable to drive the three LED simultaneously, as depicted in Figure 1, but the load can be arranged to accommodate several LED if necessary in the application. Finally, the three current mirrors can be connected in parallel to drive a single powerful LED, thus yielding 90 mA current capability in a single LED.

#### I<sup>2</sup>C PROTOCOL

The NCP5623B is programmed by means of the standard  $I^2C$  protocol controlled by an external MCU. The communication takes place with two serial bytes sharing the same  $I^2C$  frame:

- Byte#1 → physical  $I^2C$  address

- Byte#2 → Selected internal registers & function

| В7                        | В6                                                                             | B5 | B4 | В3 | B2 | B1 | В0  |  |

|---------------------------|--------------------------------------------------------------------------------|----|----|----|----|----|-----|--|

| Byte#1 : I <sup>2</sup> ( | Byte#1 : I <sup>2</sup> C Physical Address, based 7 bits : % 011 1000 → \$38 * |    |    |    |    |    |     |  |

| 0                         | 1                                                                              | 1  | 1  | 0  | 0  | 0  | R/W |  |

| Byte#2 : DA               | Byte#2 : DATA register                                                         |    |    |    |    |    |     |  |

| B7                        | B6                                                                             | B5 | B4 | В3 | B2 | B1 | В0  |  |

<sup>\*</sup>Note: according to the I<sup>2</sup>C specifications, the physical address is based on 7 bits out of the SDA byte, the 8<sup>th</sup> bit representing the R/W command. Since the NCP5623B is a receiver only, the R/W command is 0 and the hexadecimal byte send by the MCU is %0111 0000 = \$70

**B**[7:5]: INTERNAL REGISTER SELECTION:

| В7 | В6 | B5 | Function                                       |

|----|----|----|------------------------------------------------|

| 0  | 0  | 0  | Chip Shut Down → all LED current = zero        |

| 0  | 0  | 1  | Set up the maximum Output LED Current step     |

| 0  | 1  | 0  | PWM1 : LED1 control                            |

| 0  | 1  | 1  | PWM2 : LED2 control                            |

| 1  | 0  | 0  | PWM3 : LED3 control                            |

| 1  | 0  | 1  | Set the Upward IEND target                     |

| 1  | 1  | 0  | Set the Downward IEND target                   |

| 1  | 1  | 1  | Set step time and activate the Gradual Dimming |

The contain of bits B[4:0] depends upon the type of function selected by bits B[7:5] as depicted in Table 1

Table 1. INTERNAL REGISTER BITS ASSIGNMENT

| В7 | В6 | B5 | B4              | В3             | B2             | B1             | В0            | Comments                                               |

|----|----|----|-----------------|----------------|----------------|----------------|---------------|--------------------------------------------------------|

| 0  | 0  | 0  | Х               | Х              | Х              | Х              | Х             | Shut down                                              |

| 0  | 0  | 1  | 16              | 8              | 4              | 2              | 1             | Maximum Output LED Current Step see Figure 4 (Note 11) |

| 0  | 1  | 0  | BPWM16          | BPWM8          | BPWM4          | BPWM2          | BPWM1         | PWM1                                                   |

| 0  | 1  | 1  | BPWM16          | BPWM8          | BPWM4          | BPWM2          | BPWM1         | PWM2                                                   |

| 1  | 0  | 0  | BPWM16          | BPWM8          | BPWM4          | BPWM2          | BPWM1         | PWM3                                                   |

| 1  | 0  | 1  | GDIM5<br>16     | GDIM4<br>8     | GDIM3<br>4     | GDIM2<br>2     | GDIM1<br>1    | Set Gradual Dimming<br>Upward IEND Target (Note 12)    |

| 1  | 1  | 0  | GDIM5<br>16     | GDIM4<br>8     | GDIM3<br>4     | GDIM2<br>2     | GDIM1<br>1    | Set Gradual Dimming<br>Downward IEND Target (Note 12)  |

| 1  | 1  | 1  | GDIM5<br>128 ms | GDIM4<br>64 ms | GDIM3<br>32 ms | GDIM2<br>16 ms | GDIM1<br>8 ms | Gradual Dimming<br>Step Time & run                     |

<sup>11.</sup> The programmed current applies to the three LED simultaneously, the gradual dimming is not engaged

# **GRADUAL DIMMING**

The purpose of that function is to gradually Increase or Decrease the brightness of the backlight LED upon command from the external MCU. The function is activated and controlled by means of the I<sup>2</sup>C protocol.

In order to avoid arithmetic division functions at silicon level, the period (either upward or downward) is equal to the time defined for each step, multiplied by the number of steps

To operate such a function, the MCU will provide three information:

- 1 The target current level (either upward or downward)

- 2 The time per step

# 3 – The Upward or Downward mode of operation

When a new gradual dimming sequence is requested, the output current increases, according to an exponential curve, from the existing start value to the end value. The end current value is defined by the contain of the Upward or Downward registers, the width of each step is defined by the last register (B7 = B6 = B5 = 1), the number of step being in the 1 to 30 range. In the event of software error, the system checks that neither the maximum output current (30 mA), nor the zero level are forced out of their respective bounds. Similarly: software errors shall not force the NCP5623B into an uncontrolled mode of operation. not recommended to

<sup>12.</sup> The bit values represent the steps count, not the ILED current: see equations 1 & 2, page 7, to derive the ILED value.

trigger another gradual dimming when current gradual dimming is running. If IEND is set to be lower than start current level for upward gradual dimming, after gradual dimming is triggered, LED current will rise from current level to maximum, drop to zero and start from zero to IEND then. It's similar if IEND is higher than start current level for downward gradual dimming.

The dimming is built with 30 steps and the time delay is encoded into the second byte of the I<sup>2</sup>C transaction: see Table 1.

When the gradual dimming is deactivated (B7 = B6 = 0, B5 = 1), the output current is straightforwardly set up to the level defined by the contain of the related register upon acknowledge of the output current byte.

The gradual dimming sequence must be completed before a new output current data byte is send to the NCP5623B . At this point, the brightness sequence takes place when the new data byte is acknowledged by the internal  $I^2C$  decoder. Since the six registers are loaded on independent byte flow associated to the  $I^2C$  address, any parameter of the NCP5623B chip can be updated ahead of the next function as depicted in Table 2.

**Table 2. BASIC PROGRAMMING SEQUENCES**

| I <sup>2</sup> C Address | COMMAND Bits[7:0]      | Operation                                            | Note                                                                        |

|--------------------------|------------------------|------------------------------------------------------|-----------------------------------------------------------------------------|

| \$70                     | 000X XXXX              | System Shut Down                                     | Bits[4:0] are irrelevant                                                    |

| \$70                     | 0010 0000<br>0011 1111 | Set Up the ILED current                              | ILED register Bits[4:0] contain the IMAX value as defined by the Iref value |

| \$70                     | 0100 0000<br>0101 1111 | Set Up the PWM1                                      | PWM1<br>Bits[4:0] contain the PWM value                                     |

| \$70                     | 0110 0000<br>0111 1111 | Set Up the PWM2                                      | PWM2<br>Bits[4:0] contain the PWM value                                     |

| \$70                     | 1000 0000<br>1001 1111 | Set Up the PWM3                                      | PWM3 Bits[4:0] contain the PWM value                                        |

| \$70                     | 1010 0000<br>1011 1111 | Set Up the IEND Upward                               | UPWARD<br>Bits[4:0] contain the IEND value                                  |

| \$70                     | 1100 0000<br>1101 1111 | Set Up the IEND Downward                             | DWNWRD<br>Bits[4:0] contain the IEND value                                  |

| \$70                     | 1110 0000<br>1111 1111 | Set Up the Gradual Dimming time and run the sequence | GRAD<br>Bits[4:0] contain the TIME value                                    |

The number of step for a given sequence, depends upon the start and end output current range: since the IPEAK value is encoded in the Bits[4:0] binary scale, a maximum of 31 steps is achievable during a gradual dimming operation.

The number of steps will be automatically recalculated by the chip according to the equation:

Nstep = | existing step position – new step position |

As an example, assuming the previously programmed step was 5 and the new one is 15, then we will have 10 steps to run between the actual location to the end value. If the

timing was set at 16 ms, the total gradual dimming sequence will be 160 ms.

To select the direction of the gradual dimming (either Upward or Downward), one shall send the appropriate register before to activate the sequence as depicted below:

1010 1111  $\rightarrow$  1110 0011  $\rightarrow$  select an UPWARD sequence with 24 ms/step, the end IPEAK current being (IREF \* 2400) / (31 – 16) mA.

1100 0001 → 1110 0100 → select the DOWNWARD sequence with 32 ms/step, the end IPEAK current being (IREF \* 2400) / (31 - 1) mA.

Table 3. OUTPUT CURRENT PROGRAMMED VALUE (ILED = F(Step))

| Step     | ILED (mA) | Step      | ILED (mA) | Step      | ILED (mA) | Step      | ILED (mA) |

|----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0 / \$00 | 0         | 9 / \$09  | 1.25      | 18 / \$12 | 2.12      | 27 \$1B   | 6.90      |

| 1 / \$01 | 0.92      | 10 / \$0A | 1.31      | 19 / \$13 | 2.30      | 28 / \$1C | 9.20      |

| 2 / \$02 | 0.95      | 11 / \$0B | 1.38      | 20 / \$14 | 2.50      | 29 / \$1D | 13.80     |

| 3 / \$03 | 0.98      | 12 / \$0C | 1.45      | 21 / \$15 | 2.76      | 30 / \$1E | 27.60     |

| 4 / \$04 | 1.02      | 13 / \$0D | 1.53      | 22 / \$16 | 3.06      | 31 / \$1F | 27.60     |

| 5 / \$05 | 1.06      | 14 / \$0E | 1.62      | 23 / \$17 | 3.45      |           |           |

| 6 / \$06 | 1.10      | 15 / \$0F | 1.72      | 24 / \$18 | 3.94      |           |           |

| 7 / \$07 | 1.15      | 16 / \$10 | 1.84      | 25 / \$19 | 4.60      |           |           |

| 8 / \$08 | 1.20      | 17 / \$11 | 1.97      | 26 / \$1A | 5.52      |           |           |

Figure 4. Output Current Programmed

Value ( ILED = F(Step) )

#### **PWM OPERATION**

The built—in PWM are fully independent and can be programmed to any value during the normal operation of the NCP5623B chip. The PWM operate with five bits, yielding a 32 steps range to cover the full modulation (0 to 100%) of the associated LED:

- PWM = \$00 → the associated LED is fully OFF, whatever be the programmed ILED value

- PWM > \$00 but < \$1F → the brightness of the associated LED is set depending upon the PWM modulation value

- PWM = \$1F → the associated LED is fully ON, the current being the one defined by the ILED value.

Each PWM is programmable, via the I<sup>2</sup>C port as depicted, at any time under any sequence arrangement as requested by the end system's designer. The PWM does not change the ILED value, but merely modulate the ON/OFF ratio of the associated LED. What's more, none of PWM is changed by NCP5623B during gradual dimming.

Figure 5. NCP5623B Typical Efficiency as a Function of the Vf

NOTE: Efficiency is measured with the three PWM equal to 100%

Figure 6. Basic RGB Application

**DATE 02 FEB 2015**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994 .

- ASME 114.3M, 1894: CONTROLLING DIMENSION: MILLIMETERS. DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.20 MM FROM THE TERMINAL TIP.

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |  |

|-----|-------------|------|--|--|

| DIM | MIN         | MAX  |  |  |

| Α   | 0.50        | 0.60 |  |  |

| A1  | 0.00        | 0.05 |  |  |

| b   | 0.15        | 0.20 |  |  |

| D   | 2.00        | BSC  |  |  |

| D2  | 0.80        | 1.00 |  |  |

| Е   | 2.00        | BSC  |  |  |

| E2  | 0.55        | 0.65 |  |  |

| е   | 0.40        | BSC  |  |  |

| K   | 0.25        |      |  |  |

| L   | 0.30        | 0.50 |  |  |

| L1  | 0.40        | 0.50 |  |  |

### **GENERIC MARKING DIAGRAM\***

XX = Specific Device Code

= Date Code

= Pb-Free Device

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

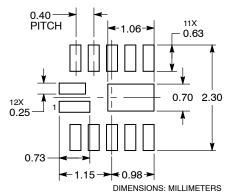

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER: | 98AON21698D       | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | LLGA12, 2X2, 0.4P |                                                                                                                                                                                     | PAGE 1 OF 1 |

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

ON Semiconductor and (III) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability. arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that ON Semiconductor was negligent regarding the design or manufacture of the part. ON Semiconductor is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

**TECHNICAL SUPPORT** North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative