# Low Distortion Digital-to-Analog Converter for Seismic Monitoring

Check for Samples: DAC1280

# **FEATURES**

• Outstanding Performance:

- THD: -125dB

SNR: 120dB (413Hz BW, Gain = 1/1)

Gain Error: 0.1%

Pin Operation: No Registers to Program

• Gain: 1/1 to 1/64

SYNC Input for Phase Control

Power-Down ModeLow Power: 18mW

Analog Supply: +5V or ±2.5VDigital Supply: 1.8V to 3.3V

Small 16-Pin TSSOP Package

Temperature Range: –40°C to +85°C

#### **APPLICATIONS**

Energy Exploration Equipment

Seismic Monitoring Systems

#### DESCRIPTION

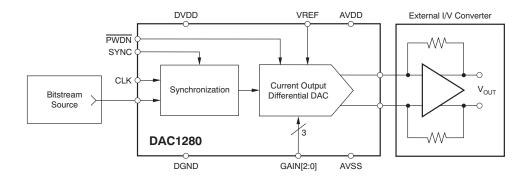

The DAC1280 is a very low distortion digital-to-analog converter (DAC) suited for performance testing of seismic equipment. The DAC1280 provides a high-accuracy output signal from a bitstream input. The device achieves very high linearity in a small package while dissipating only 18mW. Together with the high-performance ADS1281 and ADS1282 analog-to-digital converters (ADCs), these devices create a test and measurement system that meets the exacting demands of energy exploration and seismic monitoring equipment.

The DAC1280 is designed to match the system components (power supply, clock and reference voltage) of the companion ADCs, the ADS1281 and ADS1282. The input to the DAC1280 is a 1s density modulated bitstream. The DAC1280 output is a differential current intended for use with an active I/V converter. The I/V converter provides a voltage output suitable for performance testing of sensors and ADCs

Three gain control pins set the output range in 6dB steps from 0dB to -36db (±2.5V to ±0.039V differential). The attenuation ranges match the gains of the ADS1282 for testing at all gains. The DAC uses a reference voltage and bias resistor to set the full-scale output. The resistor can be adjusted to fine-trim the DAC full-scale.

The SYNC pin aligns the input data sampling to the CLK phase. A power-down pin shuts down the device when not in use. The DAC1280 is available in a small, 16-pin TSSOP package and is fully specified for operation over -40°C to +85°C temperature range with a maximum operating temperature of +125°C.

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION

For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the device product folder at www.ti.com.

# **ABSOLUTE MAXIMUM RATINGS(1)**

Over operating free-air temperature range, unless otherwise noted.

|                                        | DAC        | DAC1280    |      |  |  |

|----------------------------------------|------------|------------|------|--|--|

|                                        | MIN        | MAX        | UNIT |  |  |

| AVDD to AVSS                           | -0.3       | +5.5       | V    |  |  |

| AVSS to DGND                           | -2.8       | +0.3       | V    |  |  |

| DVDD to DGND                           | -0.3       | +3.6       | V    |  |  |

| Input current, momentary               | -100       | +100       | mA   |  |  |

| Input current, continuous              | -10        | +10        | mA   |  |  |

| Analog input or output voltage to DGND | AVSS - 0.3 | AVDD + 0.3 | V    |  |  |

| Digital input voltage to DGND          | -0.3       | DVDD + 0.3 | V    |  |  |

| Maximum junction temperature           |            | +150       | °C   |  |  |

| Operating temperature range            | -40        | +125       | °C   |  |  |

| Storage temperature range              | -60        | +150       | °C   |  |  |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

#### THERMAL INFORMATION

|                  |                                                             | DAC1280 |       |

|------------------|-------------------------------------------------------------|---------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                               | TSSOP   | UNITS |

|                  |                                                             | 16 PINS |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance (2)                  | 111.9   |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance (3)               | 33.3    |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance (4)                    | 52.4    | 900   |

| ΨЈТ              | Junction-to-top characterization parameter <sup>(5)</sup>   | 2.0     | °C/W  |

| ΨЈВ              | Junction-to-board characterization parameter <sup>(6)</sup> | 51.2    |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | _       |       |

- (1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

- (2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- (3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- (4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- (5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

- (6) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining θ<sub>JA</sub>, using a procedure described in JESD51-2a (sections 6 and 7).

- (7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

Submit Documentation Feedback

Copyright © 2010, Texas Instruments Incorporated

#### **ELECTRICAL CHARACTERISTICS**

Minimum/maximum specifications at -40°C to +85°C, typical specifications at +25°C, AVDD = +2.5V, AVSS = -2.5V, DVDD = 3.3V, CLK = 4.096MHz, V<sub>REF</sub> = 5V, and R<sub>REF</sub> = 30kΩ, unless otherwise noted. Refer to circuit configuration shown in Figure 35.

|                                      |                                                  |                 |                        |        | DAC1280      |             |               |

|--------------------------------------|--------------------------------------------------|-----------------|------------------------|--------|--------------|-------------|---------------|

| PARAMETER                            |                                                  | TEST CONDITIONS | MIN                    | TYP    | MAX          | UNIT        |               |

| ANALOG OUTPUTS                       |                                                  |                 |                        |        |              |             |               |

| Full-scale output current            | I <sub>FS</sub> = (IOUTP - IOUTN) <sup>(1)</sup> |                 | Gain = 1/1 to 1/64     |        | ±1250 • Gain |             | μА            |

| Output common-mode volta             | age <sup>(2)</sup>                               |                 |                        | - 0.15 | 0            | + 0.15      | V             |

| DC PERFORMANCE (3)                   |                                                  |                 |                        |        |              |             |               |

| Gain error                           |                                                  |                 | Gain = 1/1             |        | ±0.02        | ±0.25       | %             |

| Gain match                           |                                                  |                 | Relative to Gain = 1/1 |        | ±0.1         | ±0.5        | %             |

| Gain drift <sup>(4)</sup>            |                                                  |                 |                        |        | 4            |             | ppm/°C        |

| Offset                               |                                                  |                 | Gain = 1/1 to 1/64     |        | ±50          | ±800        | ppm of FS     |

| Offset drift <sup>(4)</sup>          |                                                  |                 |                        |        | 0.2          |             | ppm of FS/°C  |

|                                      |                                                  |                 | Gain = 1/1             |        | 1.2          |             | $\mu V_{RMS}$ |

|                                      |                                                  |                 | Gain = 1/2             |        | 1.4          |             | $\mu V_{RMS}$ |

|                                      |                                                  |                 | Gain = 1/4             |        | 1.8          |             | $\mu V_{RMS}$ |

| DC noise <sup>(5)</sup>              |                                                  |                 | Gain = 1/8             |        | 2.9          |             | $\mu V_{RMS}$ |

|                                      |                                                  |                 | Gain = 1/16            |        | 5.5          |             | $\mu V_{RMS}$ |

|                                      |                                                  |                 | Gain = 1/32            |        | 10           |             | $\mu V_{RMS}$ |

|                                      |                                                  |                 | Gain = 1/64            |        | 19           |             | $\mu V_{RMS}$ |

| AC PERFORMANCE                       |                                                  | -               |                        | 1      |              | I           |               |

|                                      |                                                  |                 | Gain = 1/1             |        | -125         | -118        | dB            |

|                                      |                                                  |                 | Gain = 1/2, 1/4, 1/8   |        | -125         |             | dB            |

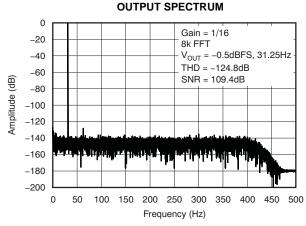

| Total harmonic distortion (6)        | THD                                              |                 | Gain = 1/16            |        | -124         |             | dB            |

| distortion                           |                                                  |                 | Gain = 1/32            |        | -118         |             | dB            |

|                                      |                                                  |                 | Gain = 1/64            |        | -113         |             | dB            |

|                                      |                                                  |                 | Gain = 1/1             | 116    | 120          |             | dB            |

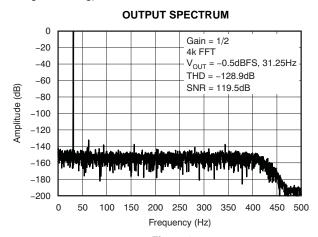

|                                      |                                                  |                 | Gain = 1/2             |        | 119          |             | dB            |

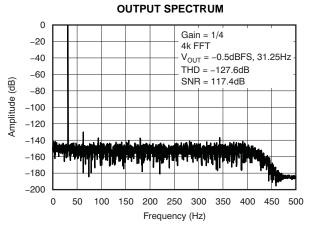

|                                      |                                                  |                 | Gain = 1/4             |        | 117          |             | dB            |

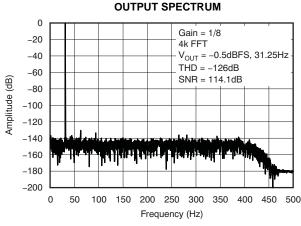

| Signal-to-noise ratio <sup>(7)</sup> | SNR                                              |                 | Gain = 1/8             |        | 114          |             | dB            |

|                                      |                                                  |                 | Gain = 1/16            |        | 109          |             | dB            |

|                                      |                                                  |                 | Gain = 1/32            |        | 105          |             | dB            |

|                                      |                                                  |                 | Gain = 1/64            |        | 99           |             | dB            |

|                                      |                                                  | AVDD, AVSS      | 60Hz ac, gain = 1/8    |        | 85           |             | dB            |

| Power-supply rejection               | y rejection PSR DVDD                             |                 | 60Hz ac                |        | 115          |             | dB            |

| -3dB bandwidth                       |                                                  |                 |                        |        | 8.2          |             | kHz           |

| REFERENCE VOLTAGE II                 | NPUT (VREF)                                      |                 |                        | 1      | 1            | <u>I</u>    | .1            |

| Reference voltage                    | V <sub>REF</sub> = VREF                          | - AVSS          |                        | 2.4    | 5            | AVDD + 0.25 | V             |

| -                                    |                                                  |                 | Operating              |        | 220          |             | kΩ            |

| Input impedance                      |                                                  |                 | Power-down             |        | 10           |             | ΜΩ            |

TDATA modulated 75% and 25% yielding positive full-scale output and negative full-scale output, respectively. Full-scale positive and TDATA modulated 1576 and 25 years properly negative output current is given by:  $\frac{100 \, \text{ITP} - \text{IOUTN}}{100 \, \text{IDM}} = \pm 7.5 \bullet \frac{\text{V}_{\text{REF}}}{\text{D}} \bullet \text{Gain}; \quad \text{V}_{\text{REF}} = 5 \text{V}, \, \text{R}_{\text{REF}} = 30 \text{k}\Omega \text{ nominal}$

$$I_{FS} = IOUTP - IOUTN = \pm 7.5 \bullet \frac{V_{REF}}{R_{BFF}} \bullet Gain; V_{REF} = 5V, R_{REF} = 30k\Omega \text{ nominal}$$

Gain can be trimmed by adjusting  $V_{\text{REF}}/R_{\text{REF}}$  ratio over the range of 40% to 105% of nominal.

- Output common-mode voltage is regulated by the external I/V converter. The specified output common-mode voltage range is: (AVDD + (2) AVSS)/2 ±0.15V.

- Excludes the tolerances of external components.

- Drift is calculated over the specified temperature range using the box calculation method.

- DC noise measured by ADS1282 with complementing gain over 413Hz bandwidth with DAC output = 0V.

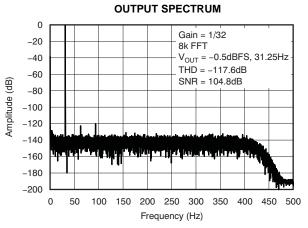

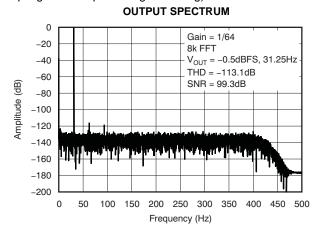

- THD = Total harmonic distortion; measured by ADS1282 with complementing gain including first nine harmonics, DAC output = -0.5dBFS, 31.25Hz.

- SNR = Signal-to-noise ratio; measured by ADS1282 with complementing gain over 413Hz bandwidth, DAC output = -0.5dBFS, 31.25Hz.

Copyright © 2010, Texas Instruments Incorporated

Submit Documentation Feedback

# **ELECTRICAL CHARACTERISTICS (continued)**

Minimum/maximum specifications at  $-40^{\circ}$ C to  $+85^{\circ}$ C, typical specifications at  $+25^{\circ}$ C, AVDD = +2.5V, AVSS = -2.5V, DVDD = 3.3V, CLK = 4.096MHz,  $V_{REF}$  = 5V, and  $R_{REF}$  = 30k $\Omega$ , unless otherwise noted. Refer to circuit configuration shown in Figure 35.

|                                       |                            |             | DAC1280              |             |      |  |

|---------------------------------------|----------------------------|-------------|----------------------|-------------|------|--|

| PARAMETER                             | TEST CONDITIONS            | MIN         | TYP                  | MAX         | UNIT |  |

| REFERENCE RESISTOR (RREF)             | ,                          |             |                      |             |      |  |

| Reference resistor                    |                            | 28          | 30                   | 60          | kΩ   |  |

| DIGITAL INPUTS (DVDD = 1.65V to 3.6V) |                            |             |                      |             |      |  |

| V <sub>IH</sub>                       |                            | 0.8 × DVDD  |                      | DVDD        | V    |  |

| V <sub>IL</sub>                       |                            | DGND        |                      | 0.2 × DVDD  | V    |  |

| Input hysteresis                      |                            |             | 0.5                  |             | V    |  |

| Input leakage                         | 0 < V <sub>IN</sub> < DVDD | -10         |                      | 10          | μА   |  |

| CLOCK INPUT (f <sub>CLK</sub> )       |                            |             |                      |             |      |  |

| Frequency                             |                            | 1           |                      | 4.096       | MHz  |  |

| TDATA INPUT                           |                            |             |                      |             |      |  |

| Frequency                             |                            |             | f <sub>CLK</sub> /16 |             | MHz  |  |

| 1s density modulation                 |                            | 25          |                      | 75          | %    |  |

| POWER SUPPLY                          |                            |             |                      |             |      |  |

| AVSS                                  |                            | -2.6        |                      | 0           | V    |  |

| AVDD                                  |                            | AVSS + 4.75 |                      | AVSS + 5.25 | V    |  |

| DVDD                                  |                            | 1.65        |                      | 3.6         | V    |  |

| AVDD, AVSS current <sup>(8)</sup>     | Gain = 1/1                 |             | 3.6                  | 3.7         | mA   |  |

| AVDD, AVSS current <sup>(c)</sup>     | Power-down                 |             | 1                    | 10          | μΑ   |  |

| DVDD current                          | Operating                  |             | 60                   | 150         | μА   |  |

| DVDD current                          | Power-down <sup>(9)</sup>  |             | 1                    | 10          | μА   |  |

| Davier dissination                    | Gain = 1/1                 |             | 18                   |             | mW   |  |

| Power dissipation                     | Power-down                 |             | 8                    |             | μW   |  |

| TEMPERATURE RANGE                     |                            |             |                      |             |      |  |

| Specified temperature range           |                            | -40         |                      | +85         | °C   |  |

| Operating temperature range           |                            | -40         |                      | +125        | °C   |  |

| Storage temperature range             |                            | -40         |                      | +150        | °C   |  |

<sup>(8)</sup> Typical analog supply current depends on gain,  $V_{REF}$ , and  $R_{REF}$ :  $I_{AVDD}$ ,  $|I_{AVSS}| = 0.94 \bullet \frac{V_{REF}}{R_{REF}} (1 + 22 \bullet \text{Gain})$

(9) CLK and TDATA stopped. Digital inputs maintained at  $V_{\text{IH}}$  or  $V_{\text{IL}}$  levels.

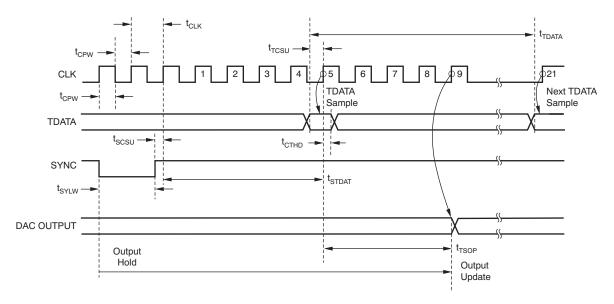

# **TIMING CHARACTERISTICS**

Figure 1.

# **TIMING REQUIREMENTS**

At  $T_A = -40$ °C to +85°C and DVDD = 1.65V to 3.6V.

|                    | PARAMETER                                       | MIN | TYP | MAX  | UNIT             |

|--------------------|-------------------------------------------------|-----|-----|------|------------------|

| t <sub>CLK</sub>   | CLK period (1/f <sub>CLK</sub> )                | 240 |     | 1000 | ns               |

| t <sub>CPW</sub>   | CLK high or low pulse width                     | 100 |     |      | ns               |

| t <sub>SCSU</sub>  | SYNC rising edge to CLK rising edge setup time  | 30  |     |      | ns               |

| t <sub>TCSU</sub>  | TDATA to CLK rising edge setup time             | 30  |     |      | ns               |

| t <sub>CTHD</sub>  | CLK rising edge to TDATA hold time              | 10  |     |      | ns               |

| t <sub>SYLW</sub>  | SYNC low pulse width                            | 2   |     |      | t <sub>CLK</sub> |

| t <sub>STDAT</sub> | Rising CLK after SYNC high to TDATA sample time |     | 5   |      | t <sub>CLK</sub> |

| t <sub>TSOP</sub>  | TDATA sample to output update                   |     | 4   |      | t <sub>CLK</sub> |

| t <sub>TDATA</sub> | TDATA period                                    | _   | 16  |      | t <sub>CLK</sub> |

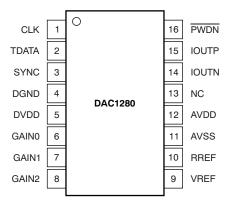

# **DEVICE INFORMATION**

#### PW PACKAGE TSSOP-16 (TOP VIEW)

# **TERMINAL FUNCTIONS**

| TERM  | TERMINAL |                | TERMINAL                                                                       |  |  |  |  |

|-------|----------|----------------|--------------------------------------------------------------------------------|--|--|--|--|

| NAME  | NO.      | 1/0            | DESCRIPTION                                                                    |  |  |  |  |

| CLK   | 1        | Digital Input  | 4.096MHz master clock                                                          |  |  |  |  |

| TDATA | 2        | Digital Input  | Bitstream digital data                                                         |  |  |  |  |

| SYNC  | 3        | Digital Input  | Synchronize control                                                            |  |  |  |  |

| DGND  | 4        | Digital Ground | Digital ground                                                                 |  |  |  |  |

| DVDD  | 5        | Digital Supply | Digital power supply                                                           |  |  |  |  |

| GAIN0 | 6        | Digital Input  | Gain select 0                                                                  |  |  |  |  |

| GAIN1 | 7        | Digital Input  | Gain select 1                                                                  |  |  |  |  |

| GAIN2 | 8        | Digital Input  | Gain select 2                                                                  |  |  |  |  |

| VREF  | 9        | Analog Input   | Voltage reference input                                                        |  |  |  |  |

| RREF  | 10       | Analog         | Full-scale range resistor                                                      |  |  |  |  |

| AVSS  | 11       | Analog Supply  | Negative analog power supply, V <sub>REF</sub> common, R <sub>REF</sub> common |  |  |  |  |

| AVDD  | 12       | Analog Supply  | Positive analog power supply                                                   |  |  |  |  |

| NC    | 13       | _              | No connection; do not connect externally.                                      |  |  |  |  |

| IOUTN | 14       | Analog Output  | Negative signal output current                                                 |  |  |  |  |

| IOUTP | 15       | Analog Output  | Positive signal output current                                                 |  |  |  |  |

| PWDN  | 16       | Digital Input  | Power-down control; active low                                                 |  |  |  |  |

Submit Documentation Feedback

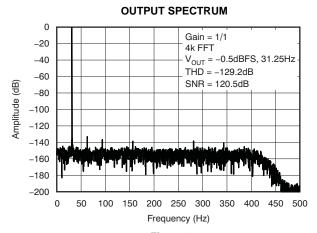

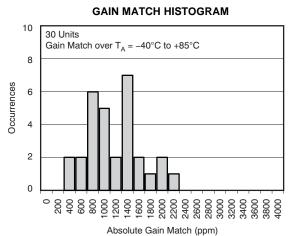

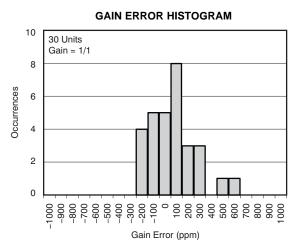

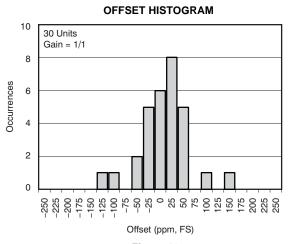

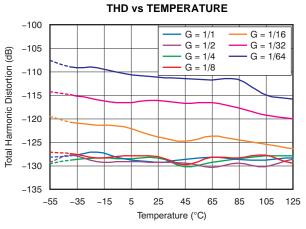

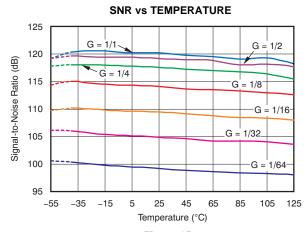

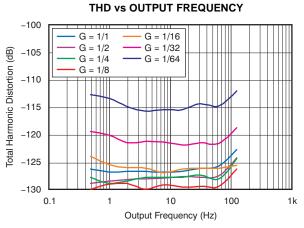

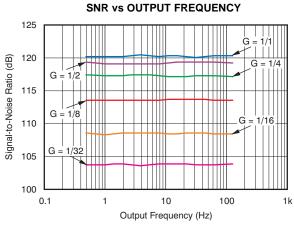

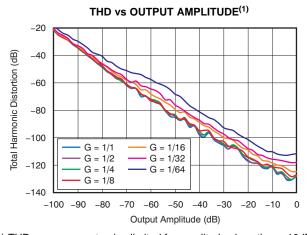

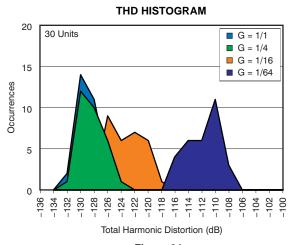

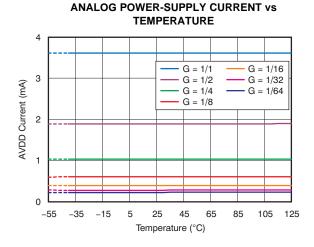

#### TYPICAL CHARACTERISTICS

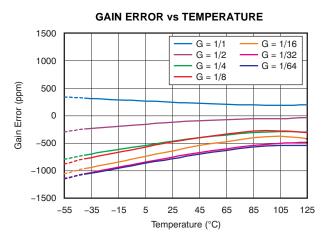

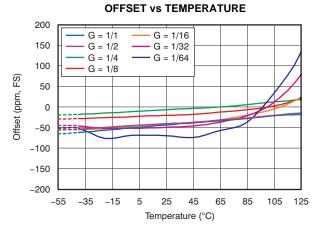

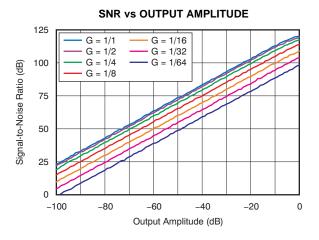

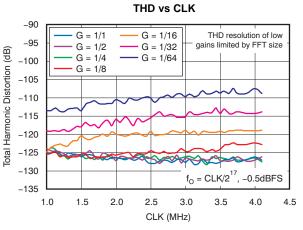

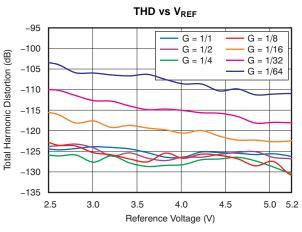

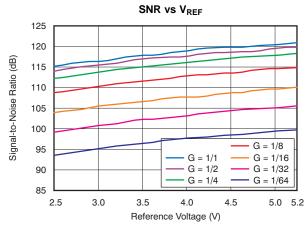

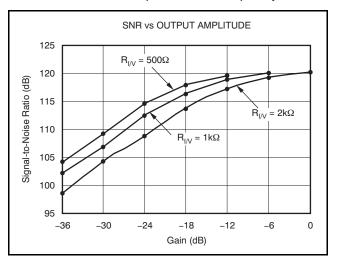

At  $T_A$  = +25°C, AVDD = +2.5V, AVSS = +2.5V, DVDD = +3.3V, CLK = 4.096MHz,  $V_{REF}$  = +5V, and  $R_{REF}$  = 30k $\Omega$ , unless otherwise noted. Data acquired using circuit configuration shown in Figure 35. THD and SNR measured by ADS1282 (1ms sampling and complement gain setting).

Figure 2.

Figure 3.

Figure 4.

Figure 5.

Figure 6.

Figure 7.

# TYPICAL CHARACTERISTICS (continued)

At  $T_A$  = +25°C, AVDD = +2.5V, AVSS = +2.5V, DVDD = +3.3V, CLK = 4.096MHz,  $V_{REF}$  = +5V, and  $R_{REF}$  = 30k $\Omega$ , unless otherwise noted. Data acquired using circuit configuration shown in Figure 35. THD and SNR measured by ADS1282 (1ms sampling and complement gain setting).

Figure 8.

Figure 10.

Figure 12.

Figure 9.

Figure 11.

Figure 13.

Submit Documentation Feedback

# TYPICAL CHARACTERISTICS (continued)

At  $T_A$  = +25°C, AVDD = +2.5V, AVSS = +2.5V, DVDD = +3.3V, CLK = 4.096MHz,  $V_{REF}$  = +5V, and  $R_{REF}$  = 30k $\Omega$ , unless otherwise noted. Data acquired using circuit configuration shown in Figure 35. THD and SNR measured by ADS1282 (1ms sampling and complement gain setting).

Figure 14.

Figure 15.

Figure 16.

Figure 17.

(1) THD measurement noise limited for amplitudes less than  $-10 \mbox{dB}.$

Figure 18.

Figure 19.

# TYPICAL CHARACTERISTICS (continued)

At  $T_A$  = +25°C, AVDD = +2.5V, AVSS = +2.5V, DVDD = +3.3V, CLK = 4.096MHz,  $V_{REF}$  = +5V, and  $R_{REF}$  = 30k $\Omega$ , unless otherwise noted. Data acquired using circuit configuration shown in Figure 35. THD and SNR measured by ADS1282 (1ms sampling and complement gain setting).

**SNR vs CLK** 125  $f_0 = CLK/2^{17}, -0.5dBFS$ 120 Signal-to-Noise Ratio (dB) 115 110 105 100 G = 1/1G = 1/16G = 1/295 G = 1/4G = 1/32G = 1/8G = 1/6490 1.0 15 20 2.5 3.0 3.5 4 0 4.5 CLK (MHz)

Figure 20.

Figure 21.

Figure 22.

Figure 23.

Figure 24.

Figure 25.

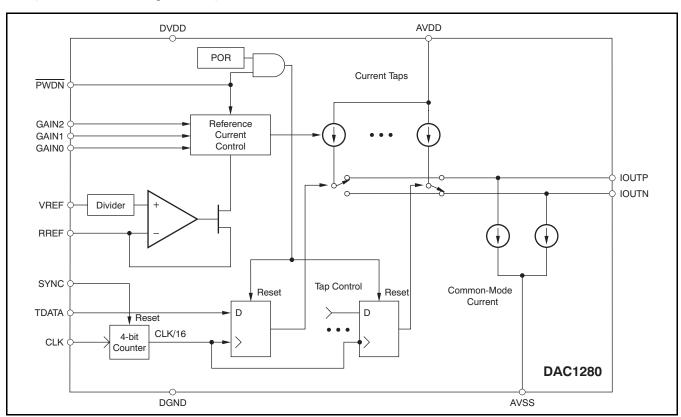

#### DAC1280 OVERVIEW

The DAC1280 is a high-accuracy digital-to-analog converter (DAC) that provides outstanding THD performance together with low noise. The DAC1280 is suitable for the demanding requirements of energy exploration and precision instrumentation where a low-distortion test signal is needed.

Figure 26 shows the DAC1280 block diagram. The DAC provides a signal output proportional to a 1s density input. The DAC design is a multi-tap, current-steering filter that provides a differential current output. An external current-to-voltage (I-V) converter is required to provide a voltage output.  $V_{REF}$  and  $R_{REF}$  program the full-scale current, and GAIN[2:0] pins set the output range.

$V_{REF}$  and  $R_{REF}$  establish an internal current that is mirrored to a multi-tap, current-steering filter stage through a reference current control block. The output of the control block is set by the GAIN[2:0] inputs, which fix the weighted tap currents in one of seven ranges. The magnitude of the tap currents results in the maximum differential output current ranges of  $1250\mu A$  to the lowest range of  $19.5\mu A$ .

The current-steering stage switches the tap current to either output, IOUTP or IOUTN, as a result of the sampling of TDATA. A higher 1s density directs more current toward IOUTP and less to IOUTN. Conversely, a higher density of 0s directs more current to IOUTN than to IOUTP. Steering of the output current yields an average output proportional to the 1s density input.

An integrated power-on-reset (POR) function resets the current taps, resulting in a zero differential output signal at power-up. The active low  $\overline{PWDN}$  input powers down the device to a low-power ( $\mu W$ ) state. The SYNC input synchronizes the DAC1280 TDATA sampling.

Figure 26. DAC1280 Block Diagram

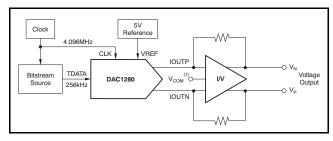

#### **DAC1280 Basics**

The basic requirements of DAC1280 operation are a clock, a bitstream input, an external current-to-voltage converter, and a reference voltage. The bitstream originates either from an FPGA-based digital modulator or playback from a ROM device holding a stored bitstream file. The external reference voltage is +5V and should be precision (low drift and low noise). The current-to-voltage converter is an active circuit. The amplifiers used for the current-to-voltage converter should have good dynamic characteristics (low THD) with low noise. Figure 27 illustrates the system block diagram.

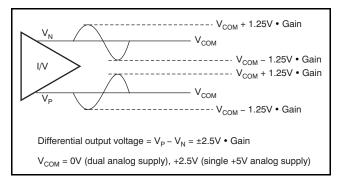

(1)  $V_{COM} = midsupply voltage$ .

Figure 27. DAC1280 System Block Diagram

#### **Output Voltage**

As shown in the system block diagram, the external I/V circuit converts the current output of the DAC to a voltage output. The voltage output of the I/V circuit is differential, as shown in Figure 28. The common-mode output voltage ( $V_{COM}$ ) at the I/V circuit is normally set to the midsupply point of the DAC. The differential output voltage is  $\pm 2.5 \text{V/gain}$ .

Figure 28. I/V Converter Output Voltage

# **Output Scaling**

The full-scale output of the DAC1280 is set by the reference voltage and an external reference resistor. The GAIN[2:0] control pins select one of seven output ranges. In operation, the reference voltage and reference resistor are usually fixed, and the DAC output range is selected by the gain pins.

The DAC1280 differential output current is determined by Equation 1:

Differential Output Current = 7.5 •

$$\frac{V_{REF}}{R_{REF}}$$

• Gain •  $\frac{(TDATA - 50\%)}{25\%}$

#### Where:

- $V_{REF} = 5V$  (nominal)

- $R_{REF} = 30k\Omega$  (nominal)

- Gain = 1/1 to 1/64

- TDATA = TDATA 1s density, ranging 25% to 75% (1)

The DAC full-scale output can be fine-trimmed, if  $\underline{{}^{\vee}_{\text{REF}}}$

desired, by changing the  $\overline{R}_{REF}$  ratio from the nominal values of  $V_{REF} = 5V$  and  $R_{REF} = 30k\Omega$ . See the Electrical Characteristics for the adjustment range.

The external current-to-voltage converter scales the DAC output current into an output voltage. Table 1 shows the DAC1280 gain (differential output current to bitstream density) and the resulting output voltage of the external current-to-voltage converter.

Table 1. DAC1280 Ideal Output Scaling<sup>(1)</sup>

| TDATA 1s DENSITY (%) | IOUTP – IOUTN (μA) | $V_P - V_N (V)$ |

|----------------------|--------------------|-----------------|

| 25                   | -1250 ● Gain       | –2.5 ● Gain     |

| 37.5                 | –625 ● Gain        | -1.25 ● Gain    |

| 50                   | 0                  | 0               |

| 62.5                 | +625 ● Gain        | +1.25 ● Gain    |

| 75                   | +1250 ● Gain       | +2.5 ● Gain     |

<sup>(1)</sup> V<sub>REF</sub> = 5V, R<sub>REF</sub> = 30kΩ, external current-to-voltage converter resistors = 2kΩ. Output current and voltage are differential. Excludes the effects of DAC1280 offset, gain and linearity errors, errors in reference voltage, errors as a result of external resistors, and errors from the external current-to-voltage conversion. Refer to Figure 27.

# **VREF Reference Voltage Input**

The DAC1280 requires an external reference for operation. The reference voltage of the DAC1280 is defined as the voltage difference between VREF and AVSS (that is,  $V_{REF} = VREF - AVSS$ ). The DAC1280 output directly scales with  $V_{REF}$ ; consequently, noise or drift on the reference appear at the DAC1280 output. A low-drift and low-noise precision reference is recommended for best performance.

For best layout, connect the ground pin of the external reference directly to the AVSS terminal to minimize possible crosstalk. A recommended  $0.1\mu\text{F}$  ceramic capacitor connected directly across VREF and AVSS reduces noise susceptibility.

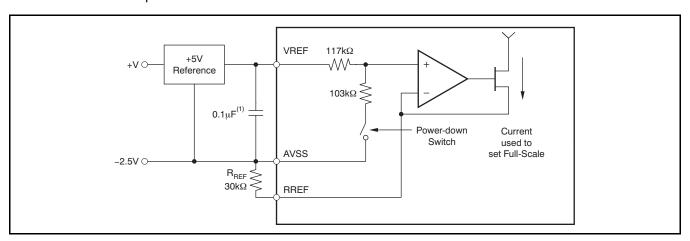

Figure 29 shows the reference input voltage and reference resistor connection to the DAC1280. The DAC1280 loads VREF with  $220k\Omega$ . The  $220k\Omega$  resistor disconnects in power-down mode.

# **RREF Reference Resistor**

A  $30k\Omega$  resistor, connected from VREF to AVSS, is required for operation. This resistor, in combination with VREF, is used to set the DAC full-scale output. The resistor can be used to fine-trim the DAC gain by changing the value from the nominal  $30k\Omega$ . See the *Output Scaling* section for more information.

The external resistor accuracy and temperature drift directly affect the DAC1280 output accuracy. A low-drift, precision resistor is recommended for best performance. Connect the resistor directly to the RREF and AVSS pins using short and direct traces. Keep RREF stray capacitance to a minimum. Refer to Figure 29 for the reference input connection.

(1) Recommended noise capacitor.

Figure 29. Reference Input Connection

#### **Pin Descriptions**

# GAIN[2:0] Pins

The DAC1280 output range can be set in 6dB steps, controlled by three digital inputs. The ranges match the gains of the ADS1282 for testing at all gains. Table 2 shows the output range versus gain settings for the DAC1280.

**NOTE:** It is recommended that the DAC and ADC use complementary gains when testing. ADC instability may result because of the combination of the noise-shaped DAC input and if the ratio of ADC/DAC gain is greater than 2.

#### **IOUTP, IOUTN**

IOUTP and IOUTN are the differential current outputs. The outputs are intended to be used in conjunction with an external current-to-voltage converter, as shown in the circuit of Figure 35. Note that the current-to-voltage converter also sets the DAC1280 DAC output common-mode voltage. See specifications for the allowable common-mode output voltage.

#### **CLK**

CLK is the master clock input to the DAC1280 (nominally 4.096MHz). As with any high-performance ADC or DAC, a high-quality, low-jitter clock source is essential. A crystal oscillator clock source is recommended. Make sure to avoid excess ringing on the clock input: keeping the printed circuit board (PCB) trace short, and using source termination resistors ( $20\Omega$  to  $50\Omega$ ) placed close to the source end, often helps.

#### **TDATA**

TDATA is the digital signal input and determines the output frequency and amplitude. TDATA is encoded as a 1s density bitstream where the DAC1280 output is proportional to the 1s density. When the 1s density input is 75% (that is, on average, three out of four

TDATA bits are '1'), the differential output current is at a positive maximum value; when the 1s density input is at 25% (on average, three out of four TDATA bits are '0'), the differential output current is at a negative maximum value. When the 1s density is 50% (on average, an equal number of '1's and '0's), the differential output current is 0. See Table 1.

TDATA is sampled by the DAC1280 at CLK/16 rate (nominally 256kHz with 4.096MHz master clock), and therefore, the sampling of TDATA can have 16 CLK cycles of uncertainty. SYNC can be used to eliminate the uncertainty by synchronizing TDATA sampling. Synchronizing TDATA sampling yields a consistent test signal phase response.

#### **SYNC**

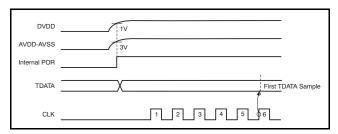

SYNC is an input used to synchronize the CLK cycle at which the DAC1280 samples TDATA. When SYNC is low, the internal CLK is disabled (ignoring TDATA input), and the DAC output is held constant. When SYNC is taken high, the DAC resumes sampling TDATA on the sixth rising CLK edge after SYNC is high. TDATA is then sampled on periodic 16 CLK intervals. Four CLK cycles propagate from the TDATA sample to the physical update of the DAC output. If SYNC is not used, tie SYNC high. Refer to Figure 1 for an illustration of the SYNC timing sequence.

#### **PWDN**

PWDN is an input used to power down the DAC1280. To power down the device, take the PWDN pin low. In power-down mode, the device bias is disabled and the outputs are Hi-Z. Note that the digital inputs must remain defined in power-down mode either as logic low or logic high; do not float the inputs. Disable the CLK and TDATA inputs to minimize power-supply leakage. To exit power-down mode, take PWDN high. The DAC1280 output is reset to zero when the PWDN pin goes high.

Table 2. Differential Current Output vs Gain Setting<sup>(1)</sup>

| GAIN[2:0] PINS | GAIN | GAIN (dB) | IOUTP – IOUTN (μA) | $V_P - V_N(V)$ |

|----------------|------|-----------|--------------------|----------------|

| 000            | 1/1  | 0         | ±1250              | ±2.5           |

| 001            | 1/2  | -6        | ±625               | ±1.25          |

| 010            | 1/4  | -12       | ±312               | ±0.625         |

| 011            | 1/8  | -18       | ±156               | ±0.312         |

| 100            | 1/16 | -24       | ±78.1              | ±0.156         |

| 101            | 1/32 | -30       | ±39.1              | ±0.0781        |

| 110            | 1/64 | -36       | ±19.5              | ±0.0391        |

(1) TDATA 1s density 25%/75%, V<sub>REF</sub> = 5V, R<sub>REF</sub> = 30kΩ, external current-to-voltage converter resistors = 2kΩ. Output current and voltage are differential. Excludes the effects of DAC1280 offset, gain and linearity errors, errors in reference voltage, errors caused by external resistors, and errors as a result of external current-to-voltage conversion. See Figure 27.

Submit Documentation Feedback

#### **Power Supplies**

The DAC1280 has two power supplies, analog and digital. The analog supply is 5V and can be configured for bipolar operation (with AVDD = 2.5V and AVSS = -2.5V), or configured for unipolar operation (with AVDD = 5V and AVSS grounded). The common-mode voltage of the external I/V converter is normally set to the DAC1280 midsupply.

Because AVSS is shared with the reference low terminal, and the analog supply pins draw signal-dependent current, the external reference ground terminal should connect to AVSS using a *star* connection close to the DAC. This approach helps to minimize power-supply coupling to the reference input.

DVDD is the digital supply and operates over the range of 1.65V to 3.6V. Bypass the DVDD as well as the analog supplies with a capacitor (minimum  $1\mu F$ ).

The power supplies can be sequenced in any order. At power-on, the latter occurrence of DVDD exceeding 1V, or (AVDD – AVSS) exceeding 3V, causes an internal power-on reset (POR) to occur. A POR resets the output to zero. After reset, the first sampling of TDATA by the DAC1280 occurs on the sixth CLK rising edge, as Figure 30 shows.

Figure 30. Power-On Sequence

# **Power Consumption**

The total power consumption is the power consumed by the DAC1280 plus that of the external current-to-voltage converter. The power consumption of the DAC1280, in turn, depends on the gain setting. Table 3 summarizes the DAC1280 power consumption.

Table 3. DAC1280 Power Consumption

| GAIN | DAC1280 POWER (mW) |

|------|--------------------|

| 1/1  | 18                 |

| 1/2  | 9.6                |

| 1/4  | 5.3                |

| 1/8  | 3.1                |

| 1/16 | 2.1                |

| 1/32 | 1.5                |

| 1/64 | 1.2                |

#### Offset and Gain Error

The DAC1280 features low offset error ( $\pm 50$ ppmFS, typical) and low gain error ( $\pm 0.02\%$ , gain = 1/1, typical). Gain match is specified as the maximum error of gain = 1/1 relative to gains 1/2 to 1/64 of a single device. Typical gain match error is  $\pm 0.1\%$ .

Offset and gain drift are also very low for the DAC1280. Drift is calculated using the box calculation method:

Drift calculation:

$$\frac{\text{Max} - \text{Min}}{\text{Temp Range}}$$

(ppm/°C) (2)

Where Max and Min are respectively the maximum and minimum offset or gain errors (in ppm) recorded over the specified temperature range of -40°C to +85°C

# Noise Performance (SNR)

The DAC1280 achieves excellent signal-to-noise ratio (SNR) performance. The SNR figures were obtained using the circuit of Figure 35. SNR is measured by the ADS1282 over a bandwidth of 0 to 413Hz (with 1ms sampling). The ADC and DAC have complementing gains for each measurement.

SNR is measured with a signal output of -0.5dBFS and 31.25Hz, then taking the Fast Fourier Transformation (FFT) of the ADC data, and calculating the noise power over the specified bandwidth. The dc, fundamental, and harmonic bins are removed for the SNR calculations. Measured this way, SNR is the combination of the individual noise sources including ADC noise, DAC1280 noise, voltage and current noise of the external op amp, and thermal noise of the I/V resistors.

If desired, SNR can be improved by decreasing the  $2k\Omega$  I/V feedback resistors and then applying correspondingly higher DAC1280 gains. Decreasing the resistor values results in a decrease of the maximum output amplitude as shown in Figure 31, SNR versus output amplitude for I/V resistor values of  $2k\Omega$ ,  $1k\Omega$ , and  $500\Omega$ . If decreasing the I/V feedback resistor, increase the I/V capacitor proportionally to maintain the same low-pass corner frequency.

Figure 31. SNR vs Output Amplitude

# **DC Noise**

DC noise is measured by the ADS1282 with the circuit configuration of Figure 35. The measurement bandwidth is 413Hz and the ADC is set to a complementing gain. The measurement is taken with a 50% 1s density input that results in a 0V differential signal output. DC noise is the standard deviation (RMS, referred to output).

# **Total Harmonic Distortion (THD)**

The DAC1280 achieves excellent THD performance. THD was characterized using the circuit shown in Figure 35 and the ADS1282 with complementary ADC gain settings for each DAC gain. Note that a low-distortion op amp for current-to-voltage conversion (such as the OPA211) is essential in order to achieve rated performance.

# **Settling Time**

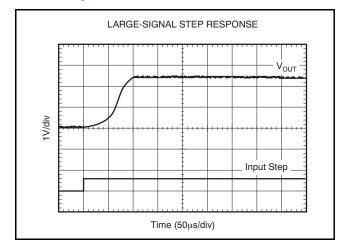

The settling time of the DAC1280 resulting from a step input change consists of the DAC1280 settling time and the I/V filter settling time. Other filter components used in the DAC signal path may also add to the settling time.

When a step input is applied to TDATA, the DAC output begins to change. The DAC completely settles in  $78\mu s$  (CLK = 4.096MHz). As the DAC output is

settling, the I/V filter network is also settling. The suggested I/V RC components (R =  $2k\Omega$ , C = 1nF) result in an I/V time constant of approximately  $2\mu s$ . Figure 32 shows the composite step response of the circuit in Figure 35.

Figure 32. DAC1280 Large-Signal Step Response (Noise Removed for Clarity)

# **Frequency Response**

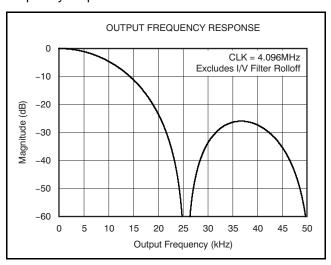

The DAC1280 low-pass filters the bitstream input, resulting in a sinc2 frequency response profile with the first notch (zero) located at  $f_{CLK}/160$  (25.6kHz with CLK = 4.096MHz). However, the aspect of noise shaping of the digital modulator may result in rising noise versus frequency. This rising noise may limit the usable bandwidth to less than the DAC inherent bandwidth. Figure 33 illustrates the DAC1280 frequency response.

Figure 33. Output Frequency Response

www.ti.com

# **Seismic System**

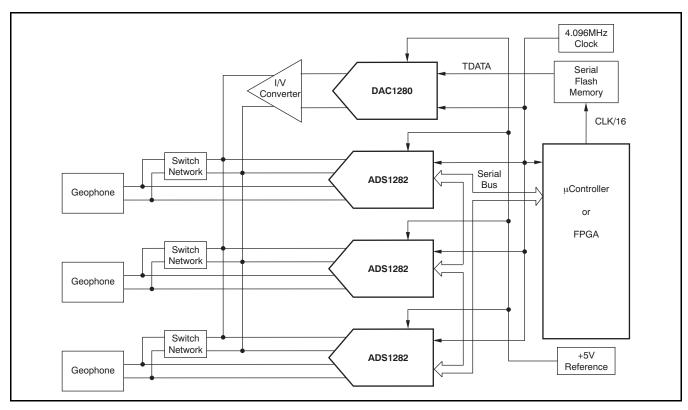

Figure 34 illustrates an example of a three-channel seismic measurement system that consists of the DAC1280 and three ADS1282s.

The DAC1280 drives the ADS1282s and the geophone sensors for testing. The DAC signal can be routed through the ADS1282 input mux to the

geophone or routed through an external switch network. The DAC input signal is sourced from a bitstream pattern stored in the device flash memory (as shown here), or supplied directly from a bitstream modulator implemented in an FPGA.

Figure 34. Three-Channel Seismic System Block Diagram

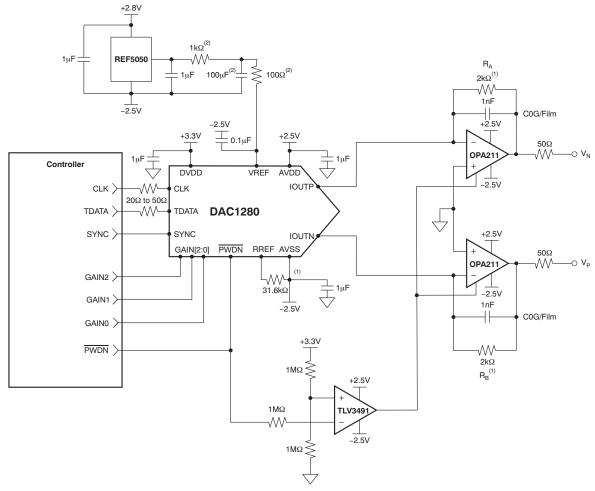

#### **Basic Connection**

Figure 35 shows a basic connection of the DAC1280, with an external op amp current-to-voltage converter. Bipolar analog supplies are shown (±2.5V). Single-supply operation (+5V) is also possible by grounding AVSS; for single-supply operation, bias the current-to-voltage converter noninverting terminals to midsupply.

A low-noise, low-drift, precision reference is recommended for operation with the DAC1280, such as the REF5050. The REF5045 or REF02 are also suitable, depending on the end system SNR requirements. The REF5045 operates from a minimum 5V power supply; the REF5050 operates from a minimum 5.3V power supply; and the REF02 operates from a minimum 8.5V power supply. The optional reference RC filter reduces broadband reference noise. Using the filter network, loading of the VREF input results in -0.5% gain error. The

reference bias resistor is a 31.6k $\Omega$  precision resistor. Increasing the resistor value (from 30k $\Omega$  nominal) reduces the DAC full-scale output by -0.5db, to avoid clipping of the ADC. The filter series resistance and the VREF input impedance interaction results in a gain error of -0.5%

Two OPA211s and R<sub>A</sub>, R<sub>B</sub> implement the current-to-voltage converter. R<sub>A</sub> and R<sub>B</sub> scale the DAC current output to a voltage output. 1nF capacitors filter the DAC sampling noise, and  $50\Omega$  resistors isolate the op amp from capacitive loads. Place the current-to-voltage converter circuit components close to the DAC1280 using a symmetrical layout. A comparator, such as the TLV3491, translates the PWDN logic level signal to the OPA211 level requirements.

- (1) Precision resistors.

- (2) Optional reference noise filter.

Figure 35. Basic Connection

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| DAC1280IPW       | ACTIVE        | TSSOP        | PW                 | 16   | 90             | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | DAC1280                 | Samples |

| DAC1280IPWR      | ACTIVE        | TSSOP        | PW                 | 16   | 2000           | RoHS & Green | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | DAC1280                 | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 26-Feb-2022

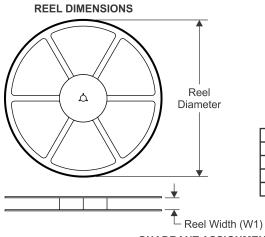

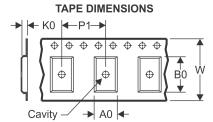

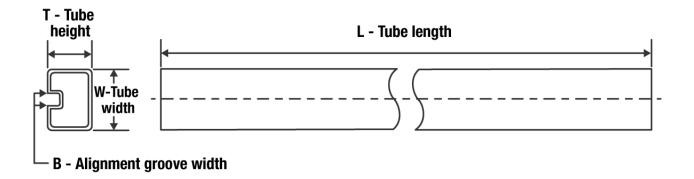

# TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

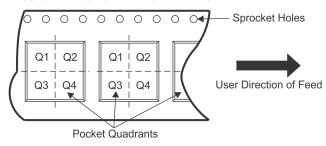

# QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

# \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DAC1280IPWR | TSSOP           | PW                 | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com 26-Feb-2022

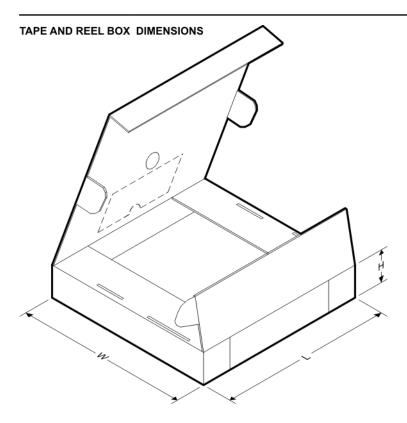

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DAC1280IPWR | TSSOP        | PW              | 16   | 2000 | 853.0       | 449.0      | 35.0        |

# PACKAGE MATERIALS INFORMATION

www.ti.com 26-Feb-2022

# **TUBE**

#### \*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| DAC1280IPW | PW           | TSSOP        | 16   | 90  | 530    | 10.2   | 3600   | 3.5    |

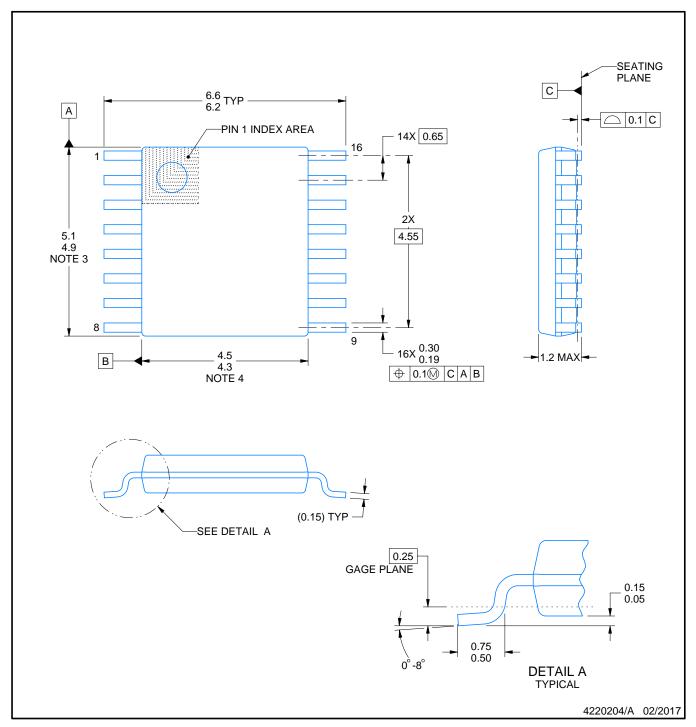

SMALL OUTLINE PACKAGE

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

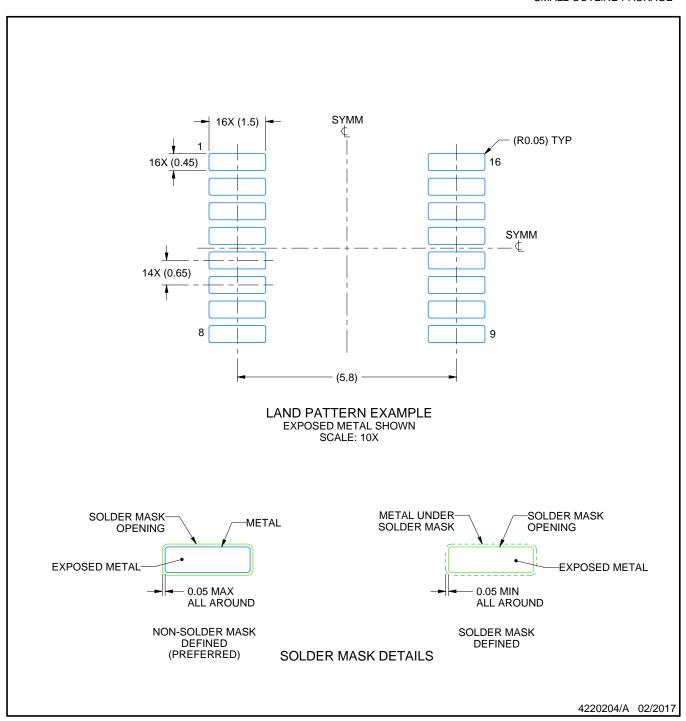

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

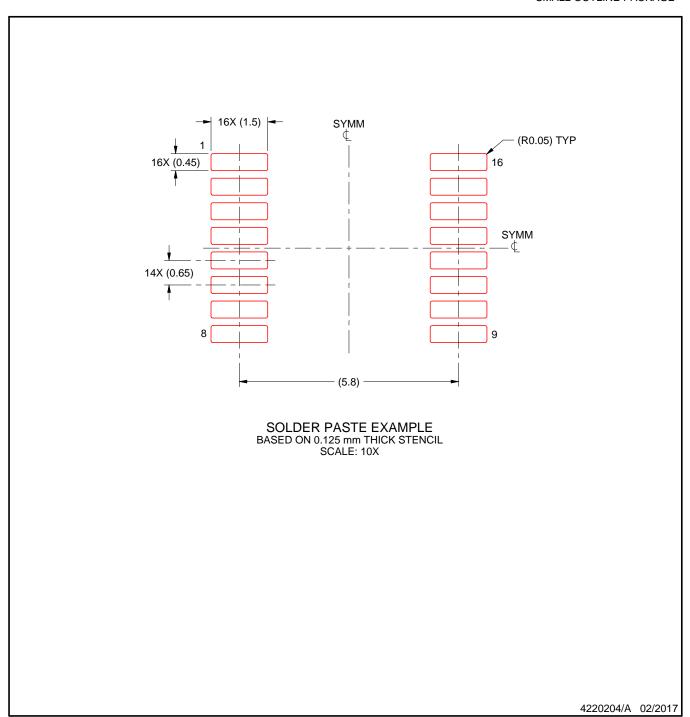

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated