LM5642, LM5642X

www.ti.com

# LM5642/LM5642X High Voltage, Dual Synchronous Buck Converter with Oscillator Synchronization

Check for Samples: LM5642, LM5642X

# FEATURES

- Two Synchronous Buck Regulators

- 180° Out of Phase Operation

- 200 kHz Fixed Nominal Frequency: LM5642

- 375 kHz Fixed Nominal Frequency: LM5642X

- Synchronizable Switching Frequency from 150 kHz to 250 kHz for the LM5642 and 200 kHz to 500 kHz for the LM5642X

- 4.5V to 36V Input Range

- 50 µA Shutdown Current

- Adjustable Output from 1.3V to 90% of Vin

- 0.04% (Typical) Line and Load Regulation Accuracy

- Current Mode Control with or without a Sense Resistor

- Independent Enable/Soft-start Pins Allow Simple Sequential Startup Configuration.

- Configurable for Single Output Parallel Operation. (See Figure 4)

- Adjustable Cycle-by-cycle Current Limit

- Input Under-voltage Lockout

- Output Over-voltage Latch Protection

- Output Under-voltage Protection with Delay

- Thermal Shutdown

- Self Discharge of Output Capacitors when the Regulator is OFF

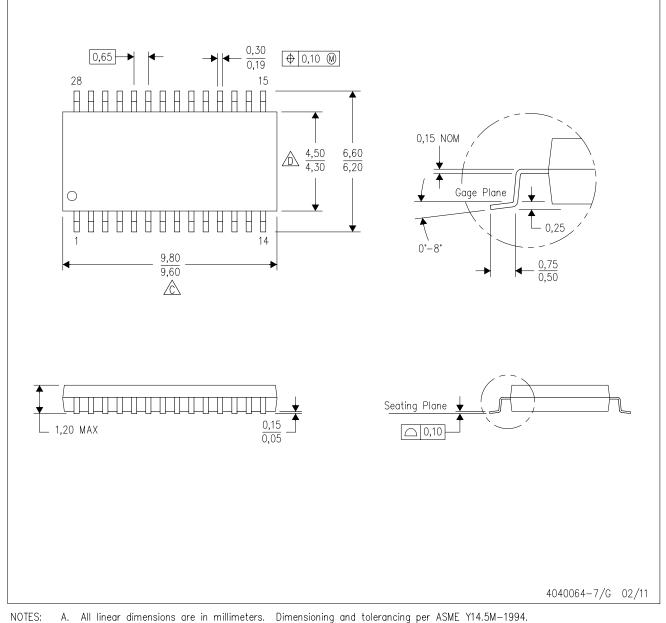

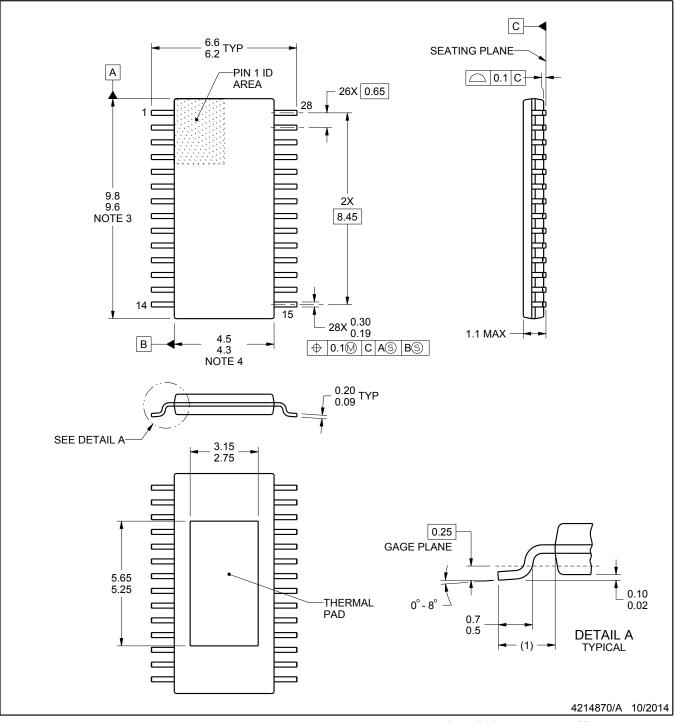

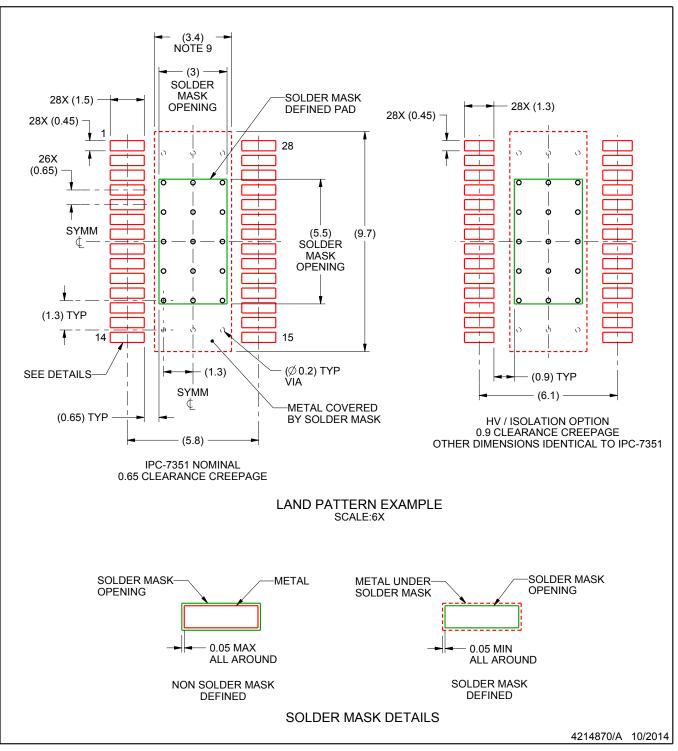

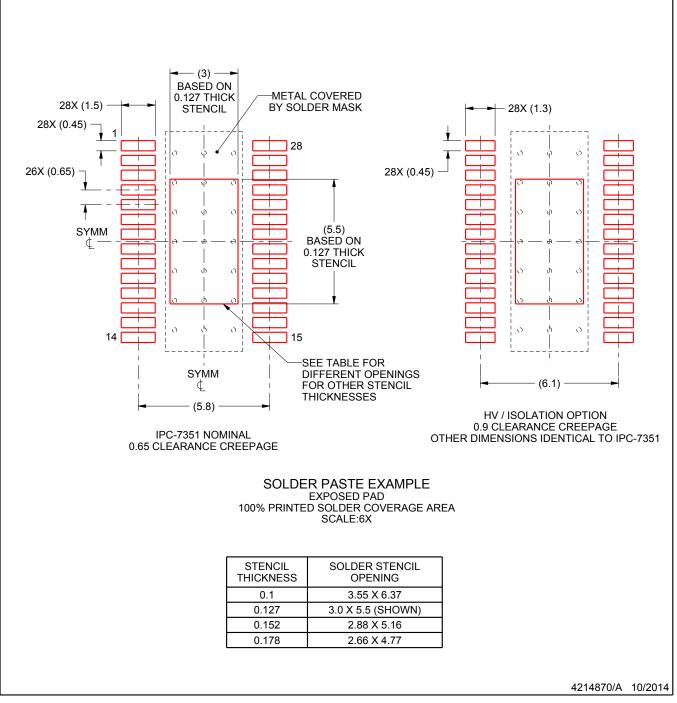

- TSSOP and HTSSOP (Exposed PAD) Packages

# **APPLICATIONS**

- Embedded Computer Systems

- Navigation Systems

- Telecom Systems

- Set-Top Boxes

- WebPAD

- Point Of Load Power Architectures

# DESCRIPTION

The LM5642 series consists of two current mode synchronous buck regulator controllers operating 180° out of phase with each other at a normal switching frequency of 200kHz for the LM5642 and at 375kHz for the LM5642X.

Out of phase operation reduces the input RMS ripple current, thereby significantly reducing the required input capacitance. The switching frequency can be synchronized to an external clock between 150 kHz and 250 kHz for the LM5642 and between 200 kHz and 500 kHz for the LM5642X. The two switching regulator outputs can also be paralleled to operate as a dual-phase, single output regulator.

The output of each channel can be independently adjusted from 1.3V to 90% of Vin. An internal 5V rail is also available externally for driving bootstrap circuitry.

Current-mode feedback control assures excellent line and load regulation and wide loop bandwidth for excellent response to fast load transients. Current is sensed across either the Vds of the top FET or across an external current-sense resistor connected in series with the drain of the top FET.

The LM5642 features analog soft-start circuitry that is independent of the output load and output capacitance making the soft-start behavior more predictable and controllable than traditional soft-start circuits.

Over-voltage protection is available for both outputs. A UV-Delay pin is also available to allow delayed shut off time for the IC during an output under-voltage event.

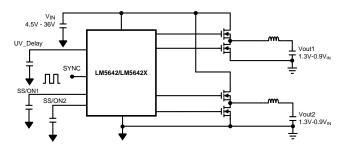

# **Typical Application Circuit**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

www.ti.com

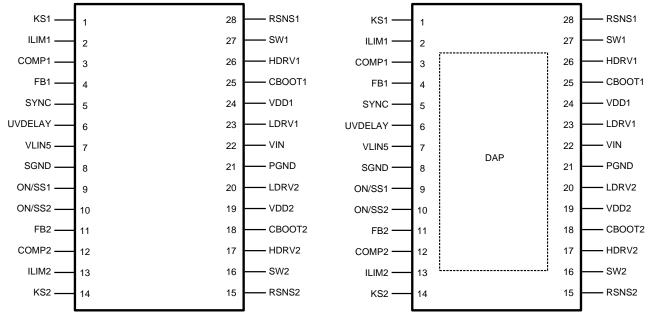

# **Connection Diagram**

Figure 1. Top View

Figure 2. Top View

# **PIN DESCRIPTIONS**

|                  | FIN DESCRIFTIONS                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| KS1 (Pin 1)      | The positive (+) Kelvin sense for the internal current sense amplifier of Channel 1. Use a separate trace to connect this pin to the current-sense point. It should be connected to VIN as close as possible to the current-sense resistor. When no current-sense resistor is used, connect as close as possible to the drain node of the upper MOSFET.                                                   |

| ILIM1 (Pin 2)    | Current limit threshold setting for Channel 1. It sinks a constant current of 9.9 $\mu$ A, which is converted to a voltage across a resistor connected from this pin to VIN. The voltage across the resistor is compared with either the V <sub>DS</sub> of the top MOSFET or the voltage across the external current sense resistor to determine if an over-current condition has occurred in Channel 1. |

| COMP1 (Pin 3)    | Compensation pin for Channel 1. This is the output of the internal transconductance error amplifier. The loop compensation network should be connected between this pin and the signal ground, SGND (Pin 8).                                                                                                                                                                                              |

| FB1 (Pin 4)      | Feedback input for channel 1. Connect to VOUT through a voltage divider to set the Channel 1 output voltage.                                                                                                                                                                                                                                                                                              |

| SYNC (Pin 5)     | The switching frequency of the LM5642 can be synchronized to an external clock.                                                                                                                                                                                                                                                                                                                           |

|                  | SYNC = LOW: Free running at 200 kHz for LM5642, and at 375kHz for LM5642X. Channels are 180° out of phase.                                                                                                                                                                                                                                                                                                |

|                  | SYNC = HIGH: Waiting for external clock                                                                                                                                                                                                                                                                                                                                                                   |

|                  | <b>SYNC = Falling Edge:</b> Channel 1 HDRV pin goes high. Channel 2 HDRV pin goes high after 2.5 µs delay. The maximum SYNC pulse width must be greater than 100 ns.                                                                                                                                                                                                                                      |

| 1                | For SYNC = Low operation, connect this pin to signal ground through a 220 k $\Omega$ resistor.                                                                                                                                                                                                                                                                                                            |

| UV_DELAY (Pin 6) | A capacitor from this pin to ground sets the delay time for UVP. The capacitor is charged from a 5 $\mu$ A current source. When UV_DELAY charges to 2.3V (typical), the system immediately latches off. Connecting this pin to ground will disable the output under-voltage protection.                                                                                                                   |

| VLIN5 (Pin 7)    | The output of an internal 5V LDO regulator derived from VIN. It supplies the internal bias for the chip and powers the bootstrap circuitry for gate drive. Bypass this pin to signal ground with a minimum of 4.7 $\mu$ F ceramic capacitor.                                                                                                                                                              |

| SGND (Pin 8)     | The ground connection for the signal-level circuitry. It should be connected to the ground rail of the system.                                                                                                                                                                                                                                                                                            |

| ON/SS1 (Pin 9)   | Channel 1 enable pin. This pin is internally pulled up to one diode drop above VLIN5. Pulling this pin below 1.2V (open-collector type) turns off Channel 1. If both ON/SS1 and ON/SS2 pins are pulled below 1.2V, the whole chip goes into <i>shut down mode</i> . Adding a capacitor to this pin provides a soft-start feature that minimizes inrush current and output voltage overshoot.              |

| ON/SS2 (Pin 10)  | Channel 2 enable pin. See the description for Pin 9, ON/SS1. May be connected to ON/SS1 for simultaneous startup or for parallel operation.                                                                                                                                                                                                                                                               |

| FB2 (Pin 11)     | Feedback input for channel 2. Connect to VOUT through a voltage divider to set the Channel 2 output voltage.                                                                                                                                                                                                                                                                                              |

# LM5642, LM5642X

SNVS219K-JUNE 2003-REVISED APRIL 2013

www.ti.com

# PIN DESCRIPTIONS (continued)

|                 | · ·                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMP2 (Pin 12)  | Compensation pin for Channel 2. This is the output of the internal transconductance error amplifier. The loop compensation network should be connected between this pin and the signal ground SGND (Pin 8).                                                                                                                                                                                        |

| ILIM2 (Pin 13)  | Current limit threshold setting for Channel 2. See ILIM1 (Pin 2).                                                                                                                                                                                                                                                                                                                                  |

| KS2 (Pin 14)    | The positive (+) Kelvin sense for the internal current sense amplifier of Channel 2. See KS1 (Pin 1).                                                                                                                                                                                                                                                                                              |

| RSNS2 (Pin 15)  | The negative (-) Kelvin sense for the internal current sense amplifier of Channel 2. Connect this pin to the low side of the current sense resistor that is placed between VIN and the drain of the top MOSFET. When the Rds of the top MOSFET is used for current sensing, connect this pin to the source of the top MOSFET. Always use a separate trace to form a Kelvin connection to this pin. |

| SW2 (Pin 16)    | Switch-node connection for Channel 2, which is connected to the source of the top MOSFET of Channel 2. It serves as the negative supply rail for the top-side gate driver, HDRV2.                                                                                                                                                                                                                  |

| HDRV2 (Pin 17)  | Top-side gate-drive output for Channel 2. HDRV is a floating drive output that rides on the corresponding switching-node voltage.                                                                                                                                                                                                                                                                  |

| CBOOT2 (Pin 18) | Bootstrap capacitor connection. It serves as the positive supply rail for the Channel 2 top-side gate drive. Connect this pin to VDD2 (Pin 19) through a diode, and connect the low side of the bootstrap capacitor to SW2 (Pin16).                                                                                                                                                                |

| VDD2 (Pin 19)   | The supply rail for the Channel 2 low-side gate drive. Connected to VLIN5 (Pin 7) through a $4.7\Omega$ resistor and bypassed to power ground with a ceramic capacitor of at least 1µF. Tie this pin to VDD1 (Pin 24).                                                                                                                                                                             |

| LDRV2 (Pin 20)  | Low-side gate-drive output for Channel 2.                                                                                                                                                                                                                                                                                                                                                          |

| PGND (Pin 21)   | The power ground connection for both channels. Connect to the ground rail of the system.                                                                                                                                                                                                                                                                                                           |

| VIN (Pin 22)    | The power input pin for the chip. Connect to the positive (+) input rail of the system. This pin must be connected to the same voltage rail as the top FET drain (or the current sense resistor when used).                                                                                                                                                                                        |

| LDRV1 (Pin 23)  | Low-side gate-drive output for Channel 1.                                                                                                                                                                                                                                                                                                                                                          |

| VDD1 (Pin 24)   | The supply rail for Channel 1 low-side gate drive. Tie this pin to VDD2 (Pin 19).                                                                                                                                                                                                                                                                                                                  |

| CBOOT1 (Pin 25) | Bootstrap capacitor connection. This pin serves as the positive supply rail for the Channel 1 top-side gate drive.<br>See CBOOT2 (Pin 18).                                                                                                                                                                                                                                                         |

| HDRV1 (Pin 26)  | Top-side gate-drive output for Channel 1. See HDRV2 (Pin 17).                                                                                                                                                                                                                                                                                                                                      |

| SW1 (Pin 27)    | Switch-node connection for Channel 1. See SW2 (Pin16).                                                                                                                                                                                                                                                                                                                                             |

| RSNS1 (Pin 28)  | The negative (-) Kelvin sense for the internal current sense amplifier of Channel 1. See RSNS2 (Pin 15).                                                                                                                                                                                                                                                                                           |

| PGND (DAP)      | The power ground connection for both channels. Connect to the ground rail of the system. Use of multiple vias to internal ground plane or GND layer helps to dissipate heat generated by output power.                                                                                                                                                                                             |

|                 |                                                                                                                                                                                                                                                                                                                                                                                                    |

#### SNVS219K – JUNE 2003 – REVISED APRIL 2013

TEXAS INSTRUMENTS

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **ABSOLUTE MAXIMUM RATINGS**<sup>(1)(2)</sup>

| Voltages from the indicated pins to S                        | GND/PGND:   |                                  |

|--------------------------------------------------------------|-------------|----------------------------------|

| VIN, ILIM1, ILIM2, KS1, KS2                                  |             | -0.3V to 38V                     |

| SW1, SW2, RSNS1, RSNS2                                       |             | -0.3 to (V <sub>IN</sub> + 0.3)V |

| FB1, FB2, VDD1, VDD2                                         |             | -0.3V to 6V                      |

| SYNC, COMP1, COMP2, UV Delay                                 |             | -0.3V to (VLIN5 +0.3)V           |

| ON/SS1, ON/SS2 (3)                                           |             | -0.3V to (VLIN5 +0.6)V           |

| CBOOT1, CBOOT2                                               |             | 43V                              |

| CBOOT1 to SW1, CBOOT2 to SW2                                 |             | -0.3V to 7V                      |

| _DRV1, LDRV2                                                 |             | -0.3V to (VDD+0.3)V              |

| HDRV1 to SW1, HDRV2 to SW2                                   |             | -0.3V                            |

| DRV1 to SW1, HDRV2 to SW2<br>DRV1 to CBOOT1, HDRV2 to CBOOT2 |             | +0.3V                            |

| Power Dissipation $(T_A = 25^{\circ}C)^{(4)}$                |             |                                  |

| TSSOP                                                        |             | 1.1W                             |

| HTSSOP                                                       |             | 3.4W                             |

| Ambient Storage Temp. Range                                  |             | −65°C to +150°C                  |

| Soldering Dwell Time, Temp. <sup>(5)</sup>                   | Wave        | 4 sec, 260°C                     |

|                                                              | Infrared    | 10sec, 240°C                     |

|                                                              | Vapor Phase | 75sec, 219°C                     |

| ESD Rating <sup>(6)</sup>                                    |             | 2kV                              |

(1) Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating Range indicates conditions for which the device is intended to be functional, but does not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

- (3) ON/SS1 and ON/SS2 are internally pulled up to one diode drop above VLIN5. Do not apply an external pull-up voltage to these pins. It may cause damage to the IC.

- (4) The maximum allowable power dissipation is calculated by using P<sub>DMAX</sub> = (T<sub>JMAX</sub> T<sub>A</sub>)/θ<sub>JA</sub>, where T<sub>JMAX</sub> is the maximum junction temperature, T<sub>A</sub> is the ambient temperature and θ<sub>JA</sub> is the junction-to-ambient thermal resistance of the specified package. The power dissipation ratings results from using 125°C, 25°C, and 90.6°C/W for T<sub>JMAX</sub>, T<sub>A</sub>, and θ<sub>JA</sub> respectively. A θ<sub>JA</sub> of 90.6°C/W represents the worst-case condition of no heat sinking of the 28-pin TSSOP. The HTSSOP package has a θ<sub>JA</sub> of 29°C/W. The HTSSOP package thermal ratings results from the IC being mounted on a 4 layer JEDEC standard board using the same temperature conditions as the TSSOP package above. A thermal shutdown will occur if the temperature exceeds the maximum junction temperature of the device.

(5) See http://www.ti.com for other methods of soldering plastic small-outline packages.

(6) For testing purposes, ESD was applied using the human-body model, a 100pF capacitor discharged through a 1.5 k $\Omega$  resistor.

# **OPERATING RATINGS** <sup>(1)</sup>

| VIN (VLIN5 tied to VIN)      | 4.5V to 5.5V    |

|------------------------------|-----------------|

| VIN (VIN and VLIN5 separate) | 5.5V to 36V     |

| Junction Temperature         | -40°C to +125°C |

(1) Absolute maximum ratings indicate limits beyond which damage to the device may occur. Operating Range indicates conditions for which the device is intended to be functional, but does not ensure specific performance limits. For ensured specifications and test conditions, see the Electrical Characteristics. The ensured specifications apply only for the test conditions. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

www.ti.com

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified,  $V_{IN} = 28V$ , GND = PGND = 0V, VLIN5 = VDD1 = VDD2. Limits appearing in **boldface** type apply over the specified operating junction temperature range, (-40°C to +125°C, if not otherwise specified). Specifications appearing in plain type are measured using low duty cycle pulse testing with  $T_A = 25°C$ <sup>(1)</sup>, <sup>(2)</sup>. Min/Max limits are specified by design, test, or statistical analysis.

| Symbol                                       | Parameter                                                | Conditions                                                          | Min    | Тур    | Max    | Units |

|----------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------|--------|--------|--------|-------|

| System                                       |                                                          |                                                                     |        |        |        |       |

| ΔV <sub>OUT</sub> /V <sub>OUT</sub>          | Load Regulation                                          | $VIN = 28V$ , $V_{compx} = 0.5V$ to $1.5V$                          |        | 0.04   |        | %     |

|                                              | Line Regulation                                          | $5.5V \le VIN \le 36V, V_{compx} = 1.25V$                           |        | 0.04   |        | %     |

| V <sub>FB1_FB2</sub>                         | Feedback Voltage                                         | 5.5V ≤ VIN ≤ 36V                                                    | 1.2154 | 1.2364 | 1.2574 |       |

|                                              |                                                          | -20°C to 85°C                                                       | 1.2179 | 1.2364 | 1.2549 | V     |

| I <sub>VIN</sub>                             | Input Supply Current                                     | $V_{ON\_SSx} > 2V$<br>5.5V ≤ VIN ≤ 36V                              |        | 1.1    | 2.0    | mA    |

|                                              |                                                          | Shutdown $^{(3)}$<br>V <sub>ON_SS1</sub> = V <sub>ON_SS2</sub> = 0V |        | 50     | 110    | μA    |

| VLIN5                                        | VLIN5 Output Voltage                                     | IVLIN5 = 0  to  25mA,<br>5.5V $\leq$ VIN $\leq$ 36V                 | 4.70   | 5      | 5.30   | V     |

| V <sub>CLos</sub>                            | Current Limit Comparator<br>Offset (VILIMX -VRSNSX)      | IN = 6V                                                             |        | ±2     | ±7.0   | mV    |

| I <sub>CL</sub>                              | Current Limit Sink Current                               |                                                                     | 8.4    | 9.9    | 11.4   | μA    |

| I <sub>ss_SC1</sub> ,<br>I <sub>ss_SC2</sub> | Soft-Start Source Current                                | $V_{ON_{SS1}} = V_{ON_{SS2}} = 1.5V$ (on) 0.5                       |        | 2.4    | 5.0    | μA    |

| I <sub>ss_SK1</sub> ,<br>I <sub>ss_SK2</sub> | Soft-Start Sink Current                                  | $V_{ON\_ss1} = V_{ON\_ss2} = 1.5V$                                  | 2      | 5.5    | 10     | μA    |

| V <sub>ON_SS1</sub> ,<br>V <sub>ON_SS2</sub> | Soft-Start On Threshold                                  |                                                                     | 0.7    | 1.12   | 1.4    | V     |

| V <sub>SSTO</sub>                            | Soft-Start Timeout<br>Threshold                          | (4)                                                                 |        | 3.4    |        | V     |

| I <sub>sc_uvdelay</sub>                      | UV_DELAY Source Current                                  | UV-DELAY = 2V                                                       | 2      | 5      | 9      | μA    |

| I <sub>sk_uvdelay</sub>                      | UV_DELAY Sink Current                                    | UV-DELAY = 0.4V                                                     | 0.2    | 0.48   | 1.2    | mA    |

| V <sub>UVDelay</sub>                         | UV_DELAY Threshold<br>Voltage                            |                                                                     |        | 2.3    |        | V     |

| V <sub>UVP</sub>                             | FB1, FB2, Under Voltage<br>Protection Latch Threshold    | As a percentage of nominal output voltage (falling edge)            | 75     | 80.7   | 86     | %     |

|                                              | Hysteresis                                               |                                                                     |        | 3.7    |        | %     |

| V <sub>OVP</sub>                             | V <sub>OUT</sub> Overvoltage<br>Shutdown Latch Threshold | As a percentage measured at $V_{\text{FB1}},V_{\text{FB2}}$         | 107    | 114    | 122    | %     |

| S <sub>wx R</sub>                            | SW1, SW2 ON-Resistance                                   | $V_{SW1} = V_{SW2} = 0.4V$                                          | 420    | 487    | 560    | Ω     |

(1) A typical is the center of characterization data measured with low duty cycle pulse tsting at  $T_A = 25^{\circ}$ C. Typicals are not ensured.

(2) All limits are specified. All electrical characteristics having room-temperature limits are tested during production with  $T_A = T_J = 25^{\circ}C$ . All hot and cold limits are specified by correlating the electrical characteristics to process and temperature variations and applying statistical process control.

(3) Both switching controllers are off. The linear regulator VLIN5 remains on.

(4) When SS1 and SS2 pins are charged above this voltage and either of the output voltages at Vout1 or Vout2 is still below the regulation limit, the under voltage protection feature is initialized.

# **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise specified,  $V_{IN} = 28V$ , GND = PGND = 0V, VLIN5 = VDD1 = VDD2. Limits appearing in **boldface** type apply over the specified operating junction temperature range, (-40°C to +125°C, if not otherwise specified). Specifications appearing in plain type are measured using low duty cycle pulse testing with  $T_A = 25°C$  <sup>(1)</sup>, <sup>(2)</sup>. Min/Max limits are specified by design, test, or statistical analysis.

| Symbol                                           | Parameter                                          | Conditions                                                                    | Min  | Тур                     | Max  | Units |

|--------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------|------|-------------------------|------|-------|

| Gate Drive                                       |                                                    | · · · · · ·                                                                   |      | 1 1                     |      | 1     |

| I <sub>CBOOT</sub>                               | CBOOTx Leakage Current                             | V <sub>CBOOT1</sub> = V <sub>CBOOT2</sub> = 7V                                |      | 10                      |      | nA    |

| I <sub>SC_DRV</sub>                              | HDRVx and LDRVx Source<br>Current                  | V <sub>CBOOT1</sub> = V <sub>CBOOT2</sub> = 5V, VSWx=0V,<br>HDRVx=LDRVx=2.5V  |      | 0.5                     |      | А     |

| I <sub>sk_HDRV</sub>                             | HDRVx Sink Current                                 | $V_{CBOOTx} = VDDx = 5V, V_{SWx} = 0V, HDRVX = 2.5V$                          |      | 0.8                     |      | А     |

| I <sub>sk_LDRV</sub>                             | LDRVx Sink Current                                 | $V_{CBOOTx} = VDDx = 5V, V_{SWx} = 0V, LDRVX = 2.5V$                          | 2.5V |                         |      | А     |

| R <sub>HDRV</sub>                                | HDRV1 & 2 Source On-<br>Resistance                 |                                                                               |      | 3.1                     |      | Ω     |

|                                                  | HDRV1 & 2 Sink On-<br>Resistance                   |                                                                               |      | 1.5                     |      | Ω     |

| R <sub>LDRV</sub>                                | LDRV1 & 2 Source On-<br>Resistance                 |                                                                               |      | 3.1                     |      | Ω     |

|                                                  | LDRV1 & 2 Sink On-<br>Resistance                   | $V_{DD1} = V_{DD1} = 5V$                                                      |      | 1.1                     |      | Ω     |

| Oscillator ar                                    | nd Sync Controls                                   |                                                                               |      |                         |      |       |

| <b>-</b>                                         | Ossillator Fraguenay                               | $5.5 \le V_{IN} \le 36V$ , LM5642                                             | 166  | <b>166</b> 200 <b>2</b> |      | - kHz |

| F <sub>osc</sub>                                 | Oscillator Frequency                               | $5.5 \le V_{IN} \le 36V$ , LM5642X                                            | 311  | 375                     | 424  | KIIZ  |

| Don_max                                          | Maximum On-Duty Cycle                              | V <sub>FB1</sub> = V <sub>FB2</sub> = 1V, Measured at pins<br>HDRV1 and HDRV2 | 96   | 98.9                    |      | %     |

| T <sub>on_min</sub>                              | Minimum On-Time                                    |                                                                               |      | 166                     |      | ns    |

| SS <sub>OT_delta</sub>                           | HDRV1 and HDRV2 Delta<br>On Time                   | ON/SS1 = ON/SS2 = 2V                                                          |      | 20                      | 250  | ns    |

| V <sub>HS</sub>                                  | SYNC Pin Min High Input                            |                                                                               | 2    | 1.52                    |      | V     |

| V <sub>LS</sub>                                  | SYNC Pin Max Low Input                             |                                                                               |      | 1.44                    | 0.8  | V     |

| Error Amplif                                     | ier                                                |                                                                               |      |                         |      |       |

| $I_{FB1}, I_{FB2}$                               | Feedback Input Bias<br>Current                     | $V_{FB1_FIX} = 1.5V, V_{FB2_FIX} = 1.5V$                                      |      | 80                      | ±200 | nA    |

| I <sub>comp1_SC</sub> ,<br>I <sub>comp2_SC</sub> | COMP Output Source<br>Current                      |                                                                               | 6    | 127                     |      | μA    |

|                                                  |                                                    | -20°C to 85°C                                                                 | 18   |                         |      |       |

| I <sub>comp1_SK</sub> ,<br>I <sub>comp2_SK</sub> | COMP Output Sink Current                           | $V_{FB1\_FIX}$ = $V_{FB2\_FIX}$ = 1.5V and $V_{COMP1}$ = $V_{COMP2}$ = 0.5V   | 6    | 118                     |      | μA    |

|                                                  |                                                    | -20°C to 85°C                                                                 | 18   |                         |      |       |

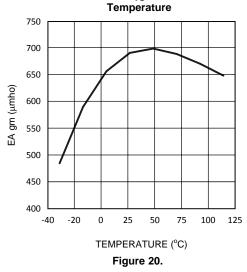

| gm1, gm2                                         | Transconductance                                   |                                                                               |      | 720                     |      | µmho  |

| GI <sub>SNS1</sub> ,<br>GI <sub>SNS2</sub>       | Current Sense Amplifier<br>(1&2) Gain              | V <sub>COMPx</sub> = 1.25V                                                    | 4.2  | 5.2                     | 7.5  |       |

| Voltage Refe                                     | erences and Linear Voltage Ro                      | egulators                                                                     |      | · · ·                   |      | •     |

| UVLO                                             | VLIN5 Under-voltage<br>Lockout<br>Threshold Rising | ON/SS1, ON/SS2 transition<br>from low to high                                 | 3.6  | 4.0                     | 4.4  | V     |

SNVS219K-JUNE 2003-REVISED APRIL 2013

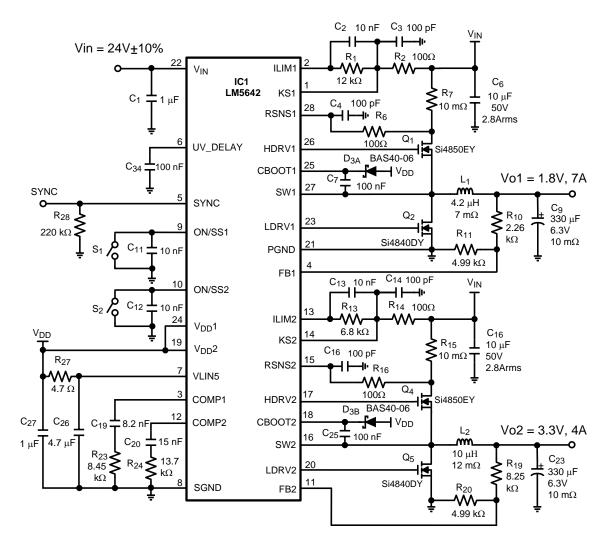

Figure 3. Typical 2 Channel Application Circuit

# LM5642, LM5642X

TEXAS INSTRUMENTS

www.ti.com

SNVS219K-JUNE 2003-REVISED APRIL 2013

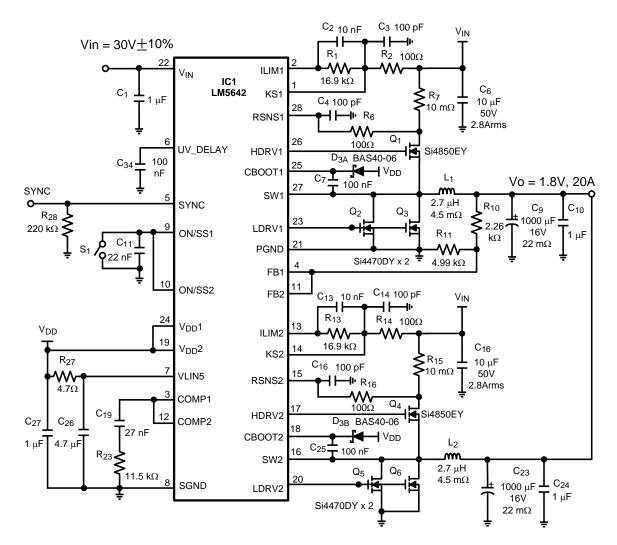

Figure 4. Typical Single Channel Application Circuit

Copyright © 2003–2013, Texas Instruments Incorporated

#### www.ti.com

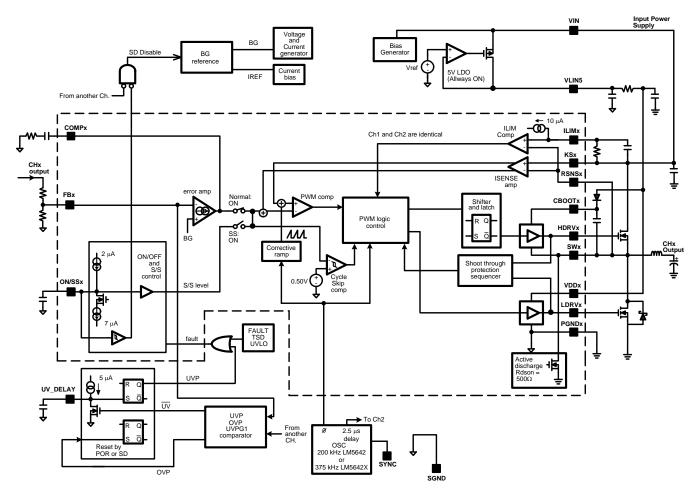

# **BLOCK DIAGRAM**

Figure 5. Block Diagram

#### SNVS219K-JUNE 2003-REVISED APRIL 2013

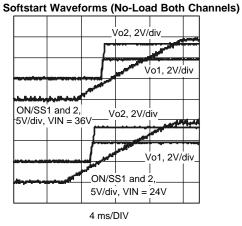

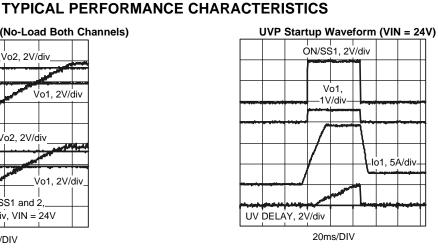

#### Figure 6.

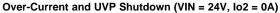

Figure 8.

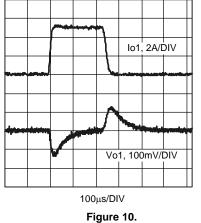

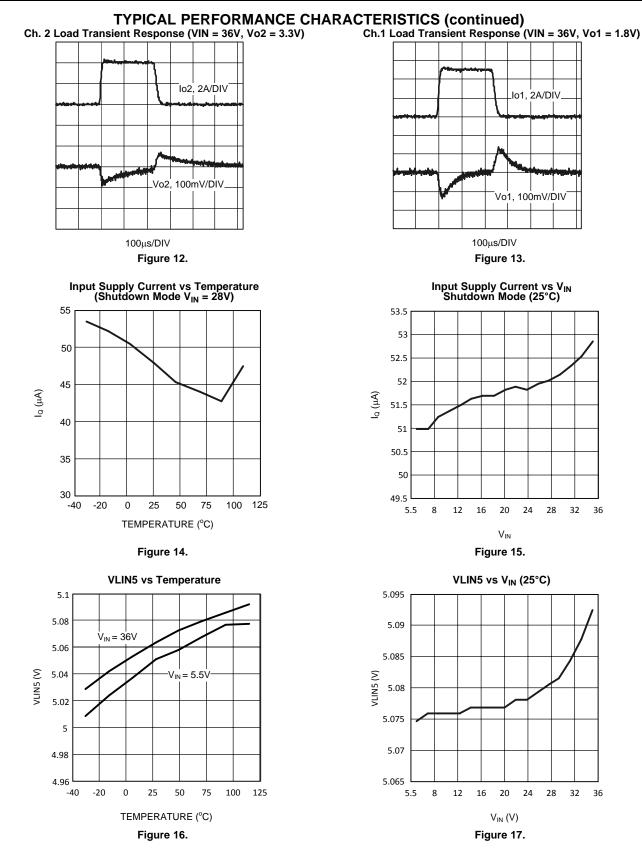

Ch.1 Load Transient Response (VIN = 24V, Vo1 = 1.8V)

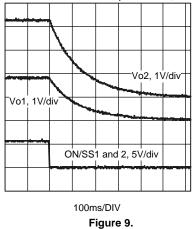

Figure 7.

Shutdown Waveforms (VIN = 24V, No-Load)

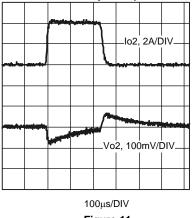

Ch.2 Load Transient Response (VIN = 24V, Vo2 = 3.3V)

Figure 11.

# LM5642, LM5642X

SNVS219K-JUNE 2003-REVISED APRIL 2013

# ÈXAS **ISTRUMENTS**

www.ti.com

### SNVS219K-JUNE 2003-REVISED APRIL 2013

25 50 75 100 125

0

TEMPERATURE (°C) Figure 19.

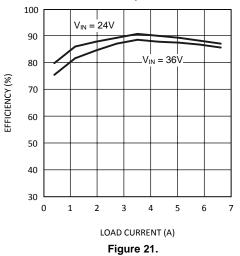

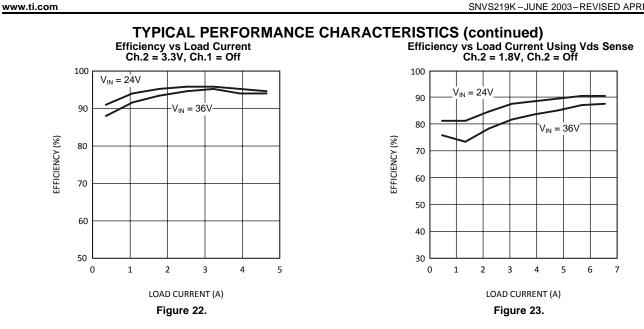

Efficiency vs Load Current Using Resistor Sense Ch.1 = 1.8V, Ch.2 = Off

12

Copyright © 2003–2013, Texas Instruments Incorporated

Efficiency vs Load Current Using Vds Sense Ch.2 = 3.3V, Ch.1 = Off

# LM5642, LM5642X

SNVS219K – JUNE 2003 – REVISED APRIL 2013

FXAS

www.ti.com

(1)

(2)

# **OPERATING DESCRIPTIONS**

### SOFT START

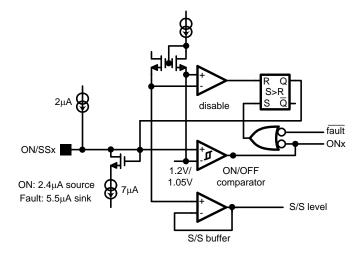

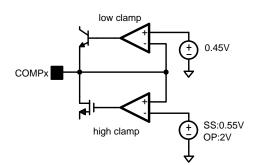

The ON/SS1 pin has dual functionality as both channel enable and soft start control. Referring to the soft start block diagram is shown in Figure 25, the LM5642 will remain in shutdown mode while both soft start pins are grounded.

In a normal application (with a soft start capacitor connected between the ON/SS1 pin and SGND) soft start functions as follows: As the input voltage rises (note, Iss starts to flow when VIN  $\ge 2.2V$ ), the internal 5V LDO starts up, and an internal 2.4 µA current charges the soft start capacitor. During soft start, the error amplifier output voltage at the COMPx pin is clamped at 0.55V and the duty cycle is controlled only by the soft start voltage. As the SSx pin voltage ramps up, the duty cycle increases proportional to the soft start ramp, causing the output voltage to ramp up. The rate at which the duty cycle increases depends on the capacitance of the soft start capacitor. The higher the capacitance, the slower the output voltage ramps up. When the corresponding output voltage exceeds 98% (typical) of the set target voltage, the regulator switches from soft start to normal operating mode. At this time, the 0.55V clamp at the output of the error amplifier releases and peak current feedback control takes over. Once in peak current feedback control mode, the output voltage of the error amplifier will travel within a 0.5V and 2V window to achieve PWM control. See Figure 26.

The amount of capacitance needed for a desired soft-start time can be approximated in the following equation:

$$C_{ss} = \frac{I_{ss} \times t_{ss}}{V_{ss}}$$

where

•  $I_{ss} = 2.4 \ \mu A$  for one channel and  $4.8 \ \mu A$  if the channels are paralleled

t<sub>ss</sub> is the desired soft-start time

Finally,

$$V_{ss} = 1.5 \left( \frac{V_o}{V_{in}} + 1 \right)$$

During soft start, over-voltage protection and current limit remain in effect. The under voltage protection feature is activated when the ON/SS pin exceeds the timeout threshold (3.4V typical). If the ON/SSx capacitor is too small, the duty cycle may increase too rapidly, causing the device to latch off due to output voltage overshoot above the OVP threshold. This becomes more likely in applications with low output voltage, high input voltage and light load. A capacitance of 10 nF is recommended at each soft start pin to provide a smooth monotonic output ramp.

Figure 25. Soft-Start and ON/OFF

SNVS219K-JUNE 2003-REVISED APRIL 2013

Figure 26. Voltage Clamp at COMPx Pin

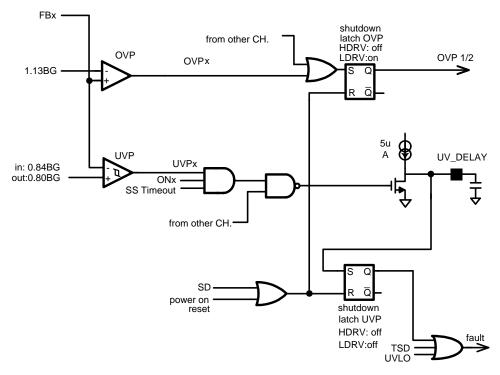

Figure 27. OVP and UVP

# **OVER VOLTAGE PROTECTION (OVP)**

If the output voltage on either channel rises above 113% of nominal, over voltage protection activates. Both channels will latch off. When the OVP latch is set, the high side FET driver, HDRVx, is immediately turned off and the low side FET driver, LDRVx, is turned on to discharge the output capacitor through the inductor. To reset the OVP latch, either the input voltage must be cycled, or both channels must be switched off (both ON/SS pins pulled low).

# UNDER VOLTAGE PROTECTION (UVP) AND UV DELAY

If the output voltage on either channel falls below 80% of nominal, under voltage protection activates. As shown in Figure 27, an under-voltage event will shut off the UV\_DELAY MOSFET, which will allow the UV\_DELAY capacitor to charge with 5µA (typical). If the UV\_DELAY pin voltage reaches the 2.3V threshold both channels will latch off. UV\_DELAY will then be disabled and the UV\_DELAY pin will return to 0V. During UVP, both the high side and low side FET drivers will be turned off. If no capacitor is connected to the UV\_DELAY pin, the UVP latch will be activated immediately. To reset the UVP latch, either the input voltage must be cycled, or both ON/SS pins must be pulled low. The UVP function can be disabled by connecting the UV\_DELAY pin to ground.

Copyright © 2003–2013, Texas Instruments Incorporated

## THERMAL SHUTDOWN

The LM5642 IC will enter thermal shutdown if the die temperature exceeds 160°C. The top and bottom FETs of both channels will be turned off immediately. In addition, both soft start capacitors will begin to discharge through separate 5.5  $\mu$ A current sinks. The voltage on both capacitors will settle to approximately 1.1V, where it will remain until the thermal shutdown condition has cleared. The IC will return to normal operating mode when the die temperature has fallen to below 146°C. At this point the two soft start capacitors will begin to charge with their normal 2.4  $\mu$ A current sources. This allows a controlled return to normal operation, similar to the soft start during turn-on. If the thermal shutdown condition clears before the voltage on the soft start capacitors has fallen to 1.1V, the capacitors will first be discharged to 1.1V, and then immediately begin charging back up.

# **OUTPUT CAPACITOR DISCHARGE**

Each channel has an embedded  $480\Omega$  MOSFET with the drain connected to the SWx pin. This MOSFET will discharge the output capacitor of its channel if its channel is off, or the IC enters a fault state caused by one of the following conditions:

- 1. UVP

- 2. UVLO

If an output over voltage event occurs, the HDRVx will be turned off and LDRVx will be turned on immediately to discharge the output capacitors of both channels through the inductors.

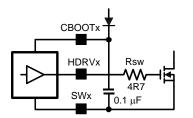

# BOOTSTRAP DIODE SELECTION

The bootstrap diode and capacitor form a supply that floats above the switch node voltage. VLIN5 powers this supply, creating approximately 5V (minus the diode drop) which is used to power the high side FET drivers and driver logic. When selecting a bootstrap diode, Schottky diodes are preferred due to their low forward voltage drop, but care must be taken for circuits that operate at high ambient temperature. The reverse leakage of some Schottky diodes can increase by more than 1000x at high temperature, and this leakage path can deplete the charge on the bootstrap capacitor, starving the driver and logic. Standard PN junction diodes and fast rectifier diodes can also be used, and these types maintain tighter control over reverse leakage current across temperature.

# SWITCHING NOISE REDUCTION

Power MOSFETs are very fast switching devices. In synchronous rectifier converters, the rapid increase of drain current in the top FET coupled with parasitic inductance will generate unwanted Ldi/dt noise spikes at the source node of the FET (SWx node) and also at the VIN node. The magnitude of this noise will increase as the output current increases. This parasitic spike noise may produce excessive electromagnetic interference (EMI), and can also cause problems in device performance. Therefore, it must be suppressed using one of the following methods.

When using resistor based current sensing, it is strongly recommended to add R-C filters to the current sense amplifier inputs as shown in Figure 29. This will reduce the susceptibility to switching noise, especially during heavy load transients and short on time conditions. The filter components should be connected as close as possible to the IC.

As shown in Figure 28, adding a resistor in series with the HDRVx pin will slow down the gate drive, thus slowing the rise and fall time of the top FET, yielding a longer drain current transition time.

Usually a  $3.3\Omega$  to  $4.7\Omega$  resistor is sufficient to suppress the noise. Top FET switching losses will increase with higher resistance values.

Small resistors (1-5 ohms) can also be placed in series with the CBOOTx pin to effectively reduce switch node ringing. A CBOOT resistor will slow the rise time of the FET, whereas a resistor at HDRV will increase both rise and fall times.

Figure 28. HDRV Series Resistor

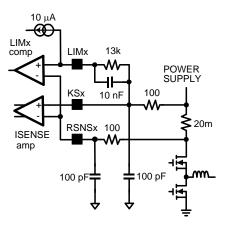

### **CURRENT SENSING AND LIMITING**

As shown in Figure 29, the KSx and RSNSx pins are the inputs of the current sense amplifier. Current sensing is accomplished either by sensing the Vds of the top FET or by sensing the voltage across a current sense resistor connected from VIN to the drain of the top FET. The advantages of sensing current across the top FET are reduced parts count, cost and power loss.

The  $R_{DS-ON}$  of the top FET is not as stable over temperature and voltage as a sense resistor, hence great care must be used in layout for  $V_{DS}$  sensing circuits. At input voltages above 30V, the maximum recommended output current is 5A per channel.

Keeping the differential current-sense voltage below 200mV ensures linear operation of the current sense amplifier. Therefore, the  $R_{DS-ON}$  of the top FET or the current sense resistor must be small enough so that the current sense voltage does not exceed 200 mV when the top FET is on. There is a leading edge blanking circuit that forces the top FET on for at least 166ns. Beyond this minimum on time, the output of the PWM comparator is used to turn off the top FET. Additionally, a minimum voltage of at least 50 mV across Rsns is recommended to ensure a high SNR at the current sense amplifier.

Assuming a maximum of 200 mV across Rsns, the current sense resistor can be calculated as follows:

$$R_{sns max} = \frac{200 \text{ mV}}{I_{max} + \frac{1}{2} I_{rip}}$$

where

- Imax is the maximum expected load current, including overload multiplier (ie: 120%)

- Irip is the inductor ripple current (see Equation 17)

(3)

The above equation gives the maximum allowable value for Rsns. Conduction losses will increase with larger Rsns, thus lowering efficiency.

The peak current limit is set by an external resistor connected between the ILIMx pin and the KSx pin. An internal 10  $\mu$ A current sink on the ILIMx pin produces a voltage across the resistor to set the current limit threshold which is then compared to the current sense voltage. A 10 nF capacitor across this resistor is required to filter unwanted noise that could improperly trip the current limit comparator.

SNVS219K – JUNE 2003 – REVISED APRIL 2013

Figure 29. Current Sense and Current Limit

Current limit is activated when the inductor current is high enough to cause the voltage at the RSNSx pin to be lower than that of the ILIMx pin. This toggles the Ilim comparator, thus turning off the top FET immediately. The comparator is disabled when the top FET is turned off and during the leading edge blanking time. The equation for current limit resistor,  $R_{lim}$ , is as follows:

$$R_{\text{lim}} = \frac{(I_{\text{lim}} + \frac{1}{2}I_{\text{rip}})R_{\text{sns}}}{10 \ \mu\text{A}}$$

where

٠

Ilim is the load current at which the current limit comparator will be tripped

(4)

When sensing current across the top FET, replace Rsns with the R<sub>DS-ON</sub> of the FET. This calculated Rlim value specifies that the minimum current limit will not be less than Imax. It is recommended that a 1% tolerance resistor be used.

When sensing across the top FET ( $V_{DS}$  sensing),  $R_{DS-ON}$  will show more variation than a current-sense resistor, largely due to temperature variation.  $R_{DS-ON}$  will increase proportional to temperature according to a specific temperature coefficient. Refer to the FET manufacturer's datasheet to determine the range of  $R_{DS-ON}$  values over operating temperature or see the Component Selection section (Equation 27) for a calculation of maximum  $R_{DS-ON}$ . This will prevent  $R_{DS-ON}$  variations from prematurely tripping the current limit comparator as the operating temperature increases.

To ensure accurate current sensing using  $V_{DS}$  sensing, special attention in board layout is required. The KSx and RSNSx pins require separate traces to form a Kelvin connection at the corresponding current sense nodes. In addition, the filter components R14, R16, C14, C15 should be removed.

# INPUT UNDER VOLTAGE LOCKOUT (UVLO)

The input under-voltage lock out threshold, which is sensed via the VLIN5 internal LDO output, is 4.0V (typical). Below this threshold, both HDRVx and LDRVx will be turned off and the internal 480Ω MOSFETs will be turned on to discharge the output capacitors through the SWx pins. When the input voltage is below the UVLO threshold, the ON/SS pins will sink 5mA to discharge the soft start capacitors and turn off both channels. As the input voltage increases again above 4.0V, UVLO will be de-activated, and the device will restart through a normal soft start phase. If the voltage at VLIN5 remains below 4.5V, but above the 4.0V UVLO threshold, the device cannot be ensured to operate within specification.

If the input voltage is between 4.0V and 5.2V, the VLIN5 pin will not regulate, but will follow approximately 200 mV below the input voltage.

# **DUAL-PHASE PARALLEL OPERATION**

In applications with high output current demand, the two switching channels can be configured to operate as a two phase converter to provide a single output voltage with current sharing between the two switching channels. This approach greatly reduces the stress and heat on the output stage components while lowering input ripple current. The inductor ripple currents also cancel to a varying degree which results in lowered output ripple voltage. Figure 4 shows an example of a typical two-phase circuit. Because precision current sense is the primary design criteria to ensure accurate current sharing between the two channels, both channels must use external sense resistors for current sensing. To minimize the error between the error amplifiers of the two channels, tie the feedback pins FB1 and FB2 together and connect to a single voltage divider for output voltage sensing. Also, tie the COMP1 and COMP2 together and connect to the compensation network. ON/SS1 and ON/SS2 must be tied together to enable and disable both channels simultaneously.

## EXTERNAL FREQUENCY SYNC

The LM5642 series has the ability to synchronize to external sources in order to set the switching frequency. This allows the LM5642 to use frequencies from 150 kHz to 250 kHz and the LM5642X to use frequencies from 200 kHz to 500 kHz. Lowering the switching frequency allows a smaller minimum duty cycle, DMIN, and hence a greater range between input and output voltage. Increasing switching frequency allows the use of smaller output inductors and output capacitors (see Component Selection). In general, synchronizing all the switching frequencies in multi-converter systems makes filtering of the switching noise easier.

The sync input can be from a system clock, from another switching converter in the system, or from any other periodic signal with a logic low-level less than 1.4V and a logic high level greater than 2V. Both CMOS and TTL level inputs are acceptable.

The LM5642 series uses a fixed delay between Channel 1 and Channel 2. The nominal switching frequency of 200kHz for the LM5642 corresponds to a switching period of 5µs. Channel 2 always turns its high-side switch on 2.5µs after Channel 1 Figure 30 (a). When the converter is synchronized to a frequency other than 200kHz, the switching period is reduced or increased, while the fixed delay between Channel 1 and Channel 2 remains constant. The phase difference between channels is therefore no longer 180°. At the extremes of the sync range, the phase difference drops to 135° Figure 30 (b) and Figure 30 (c). The result of this lower phase difference is a reduction in the maximum duty cycle of one channel that will not overlap the duty cycle of the other. As shown in Input Capacitor Selection section, when the duty cycle D1 for Channel 1 overlaps the duty cycle D2 for Channel 2, the input rms current increases, requiring more input capacitors or input capacitors with higher ripple current ratings. The new, reduced maximum duty cycle can be calculated by multiplying the sync frequency (in Hz) by 2.5x10<sup>-6</sup> (the fixed delay in seconds). The same logic applies to the LM5642X. However the LM5642X has a nominal switching frequency of 375kHz which corresponds to a period of 2.67µs. Therefore channel 2 of the LM5642X always begins it's period after 1.33µs.

$D_{MAX} = FSYNC^{*}2.5x10^{-6}$

(5)

At a sync frequency of 150 kHz, for example, the maximum duty cycle for Channel 1 that will not overlap Channel 2 would be 37.5%. At 250 kHz, it is the duty cycle for Channel 2 that is reduced to a  $D_{MAX}$  of 37.5%.

SNVS219K – JUNE 2003 – REVISED APRIL 2013

www.ti.com

Figure 30. Period Fixed Delay Example

# **Component Selection**

# **OUTPUT VOLTAGE SETTING**

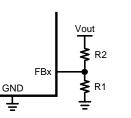

The output voltage for each channel is set by the ratio of a voltage divider as shown in Figure 31. The resistor values can be determined by the following equation:

$$R_1 = \frac{R_2}{\left(\frac{V_{nom}}{V_{fb}} - 1\right)}$$

where

(6)

Although increasing the value of R1 and R2 will increase efficiency, this will also decrease accuracy. Therefore, a maximum value is recommended for R2 in order to keep the output within .3% of Vnom. This maximum R2 value should be calculated first with the following equation:

$$R_{2 \max} = \frac{.3\% \cdot V_{\text{nom}}}{200 \,\text{nA}}$$

where

• 200nA is the maximum current drawn by FBx pin

(7)

Figure 31. Output Voltage Setting

Example: Vnom = 5V, Vfb = 1.2364V, Ifbmax = 200nA.

$$R_{2 \text{ max}} = \frac{.003 \cdot 5V}{200 \text{ nA}} = 75 \text{ k}\Omega$$

Choose 60K

$$R_{1} = \frac{60k}{\left(\frac{5V}{1.2364} - 1\right)} = 19.71 \, k\Omega \cong 20 \, k\Omega$$

(9)

(8)

The Cycle Skip and Dropout modes of the LM5642 series regulate the minimum and maximum output voltage/duty cycle that the converter can deliver. Both modes check the voltage at the COMP pin. Minimum output voltage is determined by the Cycle Skip Comparator. This circuitry skips the high side FET ON pulse when the COMP pin voltage is below 0.5V at the beginning of a cycle. The converter will continue to skip every other pulse until the duty cycle (and COMP pin voltage) rise above 0.5V, effectively halving the switching frequency.

Maximum output voltage is determined by the Dropout circuitry, which skips the low side FET ON pulse whenever the COMP pin voltage exceeds the ramp voltage derived from the current sense. Up to three low side pulses may be skipped in a row before a minimum on-time pulse must be applied to the low side FET.

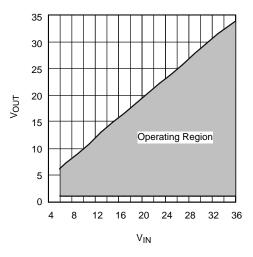

Figure 32 shows the range of ouput voltage (for Io = 3A) with respect to input voltage that will keep the converter from entering either Skip Cycle or Dropout mode.

For input voltages below 5.5V, VLIN5 must be connected to Vin through a small resistor (approximately 4.7 ohm). This will ensure that VLIN5 does not fall below the UVLO threshold.

Figure 32. Output Voltage Range

#### **Output Capacitor Selection**

In applications that exhibit large, fast load current swings, the slew rate of such a load current transient will likely be beyond the response speed of the regulator. Therefore, to meet voltage transient requirements during worst-case load transients, special consideration should be given to output capacitor selection. The total combined ESR of the output capacitors must be lower than a certain value, while the total capacitance must be greater than a certain value. Also, in applications where the specification of output voltage regulation is tight and ripple voltage must be low, starting from the required output voltage ripple will often result in fewer design iterations.

### ALLOWED TRANSIENT VOLTAGE EXCURSION

The allowed output voltage excursion during a load transient ( $\Delta Vc_s$ ) is:

$$\Delta V_{c_s} = (\delta\% - \varepsilon\%) \cdot V_{nom} - \frac{1}{2} V_{rip}.$$

where

- $\pm \delta$ % is the output voltage regulation window

- ±ε% is the output voltage initial accuracy

Example: Vnom = 5V,  $\delta\%$  = 7%,  $\epsilon\%$  = 3.4%, Vrip = 40mV peak to peak.

$$\Delta V_{c_s} = (7\% - 3.4\%) \times 5V - \frac{40 \text{ mV}}{2}$$

= 160 mV. (11)

### MAXIMUM ESR CALCULATION

Unless the rise and fall times of a load transient are slower than the response speed of the control loop, if the total combined ESR (Re) is too high, the load transient requirement will not be met, no matter how large the capacitance.

The maximum allowed total combined ESR is:

$$R_{e_{max}} = \frac{\Delta V_{c_{s}}}{\Delta I_{c_{s}}}$$

(12)

Since the ripple voltage is included in the calculation of  $\Delta Vc_s$ , the inductor ripple current should not be included in the worst-case load current excursion. Simply use the worst-case load current excursion for  $\Delta lc_s$ .

Example:  $\Delta Vc_s = 160 \text{ mV}$ ,  $\Delta Ic_s = 3A$ . Then Re\_max = 53.3 m $\Omega$ .

Maximum ESR criterion can be used when the associated capacitance is high enough, otherwise more capacitors than the number determined by this criterion should be used in parallel.

#### MINIMUM CAPACITANCE CALCULATION

In a switch mode power supply, the minimum output capacitance is typically dictated by the load transient requirement. If there is not enough capacitance, the output voltage excursion will exceed the maximum allowed value even if the maximum ESR requirement is met. The worst-case load transient is an unloading transient that happens when the input voltage is the highest and when the current switching cycle has just finished. The corresponding minimum capacitance is calculated as follows:

$$C_{\min} = \frac{L \cdot \left[\Delta V_{c_s} - \sqrt{(\Delta V_{c_s})^2 - (\Delta I_{c_s} \cdot R_e)^2}\right]}{V_{nom} \cdot R_e^2}$$

(13)

Notice it is already assumed the total ESR, Re, is no greater than Re\_max, otherwise the term under the square root will be a negative value. Also, it is assumed that L has already been selected, therefore the minimum L value should be calculated before  $C_{min}$  and after Re (see Inductor Selection below). Example: Re = 20 m $\Omega$ , Vnom = 5V,  $\Delta Vc_s$  = 160 mV,  $\Delta Ic_s$  = 3A, L = 8  $\mu$ H

$$C_{\min} = \frac{8 \ \mu \text{H} \cdot \left[ 160 \ \text{mV} - \sqrt{(160 \ \text{mV})^2 - (34 \ \text{x} \ 20 \ \text{m} \Omega)^2} \right]}{5 \ \text{x} \ (20 \ \text{m} \Omega)^2}$$

= 47 \ \mu \text{F}.

Generally speaking,  $C_{min}$  decreases with decreasing Re,  $\Delta Ic_s$ , and L, but with increasing Vnom and  $\Delta Vc_s$ .

(14)

**EXAS**

(10)

#### Inductor Selection

The size of the output inductor can be determined from the desired output ripple voltage, Vrip, and the impedance of the output capacitors at the switching frequency. The equation to determine the minimum inductance value is as follows:

$$L_{\min} = \frac{V_{in} - V_{nom}}{f \cdot V_{in}} \cdot \frac{V_{nom} \cdot R_{e}}{V_{rip}}$$

(15)

In the above equation, Re is used in place of the impedance of the output capacitors. This is because in most cases, the impedance of the output capacitors at the switching frequency is very close to Re. In the case of ceramic capacitors, replace Re with the true impedance at the switching frequency.

**Example:** Vin = 36V, Vo = 3.3V,  $V_{RIP}$  = 60 mV, Re = 20 m $\Omega$ , F = 200 kHz.

$$L_{\min} = \frac{36 - 3.3}{200 \text{kHz x } 36} \times \frac{3.3 \times 0.02}{.060} = 5 \mu \text{H}$$

(16)

The actual selection process usually involves several iterations of all of the above steps, from ripple voltage selection, to capacitor selection, to inductance calculations. Both the highest and the lowest input and output voltages and load transient requirements should be considered. If an inductance value larger than Lmin is selected, make sure that the Cmin requirement is not violated.

Priority should be given to parameters that are not flexible or more costly. For example, if there are very few types of capacitors to choose from, it may be a good idea to adjust the inductance value so that a requirement of 3.2 capacitors can be reduced to 3 capacitors.

Since inductor ripple current is often the criterion for selecting an output inductor, it is a good idea to doublecheck this value. The equation is:

$$I_{rip} = \frac{(V_{in} - V_{nom})}{f \cdot L} \cdot D$$

(17)

Also important is the ripple content, which is defined by Irip /Inom. Generally speaking, a ripple content of less than 50% is ok. Larger ripple content will cause too much power loss in the inductor.

**Example:** Vin = 36V, Vo = 3.3V, F = 200 kHz, L = 5  $\mu$ H, 3A max I<sub>OUT</sub>

$$I_{rip} = \frac{36 - 3.3}{200 \text{kHz x } 5 \text{x} 10^{-6}} \times \frac{3.3}{36} = 3\text{A}$$

(18)

3A is 100% ripple which is too high.

In this case, the inductor should be reselected on the basis of ripple current.

**Example:** 40% ripple, 40% • 3A = 1.2A

$$1.2A = \frac{36 - 3.3}{L \times 200 \text{ kHz}} \times \frac{3.3}{36}$$

(19)

$$L = \frac{36 - 3.3}{200 \text{ kHz} \times 1.2A} \times \frac{3.3}{36} = 12.5 \mu \text{ H}$$

(20)

When choosing the inductor, the saturation current should be higher than the maximum peak inductor current and the RMS current rating should be higher than the maximum load current.

#### **Input Capacitor Selection**

The fact that the two switching channels of the LM5642 are 180° out of phase will reduce the RMS value of the ripple current seen by the input capacitors. This will help extend input capacitor life span and result in a more efficient system. Input capacitors must be selected that can handle both the maximum ripple RMS current at highest ambient temperature as well as the maximum input voltage. In applications in which output voltages are less than half of the input voltage, the corresponding duty cycles will be less than 50%. This means there will be no overlap between the two channels' input current pulses.

(16)

Copyright © 2003–2013, Texas Instruments Incorporated

# LM5642, LM5642X

SNVS219K-JUNE 2003-REVISED APRIL 2013

The equation for calculating the maximum total input ripple RMS current for duty cycles under 50% is:

$$I_{irrm} = \sqrt{I_1^2 D_1 (1 - D_1) + I_2^2 D_2 (1 - D_2) - 2I_1 I_2 D_1 D_2}$$

where

- I1 is maximum load current of Channel 1

- 12 is the maximum load current of Channel 2

- D1 is the duty cycle of Channel 1

- D2 is the duty cycle of Channel 2

Example: Imax\_1 = 3.6A, Imax\_2 = 3.6A, D1 = 0.42, and D2 = 0.275

$$H_{\rm irrm} = \left[ (3.6A)^2 \cdot 0.42 \cdot (1 - 0.42) + (3.6A)^2 \cdot 0.275 \cdot (1 - 0.275) - 2 \cdot 3.6A \cdot 3.6A \cdot 0.42 \cdot 0.275 \right]^{.5}$$

= 1.66A.

Choose input capacitors that can handle 1.66A ripple RMS current at highest ambient temperature. In applications where output voltages are greater than half the input voltage, the corresponding duty cycles will be greater than 50%, and there will be overlapping input current pulses. Input ripple current will be highest under these circumstances. The input RMS current in this case is given by:

$$I_{irrm} = \begin{bmatrix} I_1 (1 - D_1) + I_2 (1 - D_2) \end{bmatrix}^2 (D_1 + D_2 - 1) \\ + \begin{bmatrix} I_1 (1 - D_1) - I_2 (D_2) \end{bmatrix}^2 (1 - D_2) + \\ \begin{bmatrix} I_2 (1 - D_2) - I_1 (D_1) \end{bmatrix}^2 (1 - D_1) \end{bmatrix}^{(2)}$$

(23)

Where, again, 11 and 12 are the maximum load currents of channel 1 and 2, and D1 and D2 are the duty cycles. This equation should be used when both duty cycles are expected to be higher than 50%.

If the LM5642 is being used with an external clock frequency other than 200kHz, or 375 kHz for the LM5642X, the preceding equations for input rms current can still be used. The selection of the first equation or the second changes because overlap can now occur at duty cycles that are less than 50%. From the EXTERNAL FREQUENCY SYNC section, the maximum duty cycle that ensures no overlap between duty cycles (and hence input current pulses) is:

$$D_{MAX} = F_{SYNC}^{*} 2.5 \times 10^{-6}$$

There are now three distinct possibilities which must be considered when selecting the equation for input rms current. The following applies for the LM5642, and also the LM5642X by replacing 200 kHz with 375 kHz:

- 1. Both duty cycles  $D_1$  and  $D_2$  are less than  $D_{MAX}$ . In this case, the first, simple equation can always be used.

- 2. One duty cycle is greater than D<sub>MAX</sub> and the other duty cycle is less than D<sub>MAX</sub>. In this case, the system designer can take advantage of the fact that the sync feature reduces D<sub>MAX</sub> for one channel, but lengthens it for the other channel. For  $F_{SYNC}$  < 200kHz,  $D_1$  is reduced to  $D_{MAX}$  while  $D_2$  actually increases to (1- $D_{MAX}$ ). For F<sub>SYNC</sub> > 200kHz, D<sub>2</sub> is reduced to D<sub>MAX</sub> while D<sub>1</sub> increases to (1-D<sub>MAX</sub>). By using the channel reduced to D<sub>MAX</sub> for the lower duty cycle, and the channel that has been increased for the higher duty cycle, the first, simple rms input current equation can be used.

- 3. Both duty cycles are greater than D<sub>MAX</sub>. This case is identical to a system at 200 kHz where either duty cycle is 50% or greater. Some overlap of duty cycles is specified, and hence the second, more complicated rms input current equation must be used.

Input capacitors must meet the minimum requirements of voltage and ripple current capacity. The size of the capacitor should then be selected based on hold up time requirements. Bench testing for individual applications is still the best way to determine a reliable input capacitor value. Input capacitors should always be placed as close as possible to the current sense resistor or the drain of the top FET. When high ESR capacitors such as tantalum are used, a 1µF ceramic capacitor should be added as closely as possible to the high-side FET drain and low-side FET source.

ISTRUMENTS

**EXAS**

(22)

(21)

(24)

#### **MOSFET Selection**

### **BOTTOM FET SELECTION**

During normal operation, the bottom FET is switching on and off at almost zero voltage. Therefore, only conduction losses are present in the bottom FET. The most important parameter when selecting the bottom FET is the on-resistance ( $R_{DS-ON}$ ). The lower the on-resistance, the lower the power loss. The bottom FET power loss peaks at maximum input voltage and load current. The equation for the maximum allowed on-resistance at room temperature for a given FET package, is:

$$R_{dson_max} = \frac{1}{I_{max}^2 \cdot \left(1 - \frac{V_{nom}}{V_{in_max}}\right)} \times \frac{T_{j_max} - T_{a_max}}{\left[1 + TC \cdot (T_{i_max} - 25^{\circ}C/W)\right] \cdot R_{\theta ia}}$$

where

- Tj\_max is the maximum allowed junction temperature in the FET

- Ta\_max is the maximum ambient temperature

- $R_{\theta ia}$  is the junction-to-ambient thermal resistance of the FET

- TC is the temperature coefficient of the on-resistance which is typically in the range of 4000ppm/°C (25)

If the calculated  $R_{DS-ON\ (MAX)}$  is smaller than the lowest value available, multiple FETs can be used in parallel. This effectively reduces the  $I_{max}$  term in the above equation, thus reducing  $R_{DS-ON}$ . When using two FETs in parallel, multiply the calculated  $R_{DS-ON\ (MAX)}$  by 4 to obtain the  $R_{DS-ON\ (MAX)}$  for each FET. In the case of three FETs, multiply by 9.

$$R_{ds_max} = \frac{1}{(3.6A)^2 \cdot \left(1 - \frac{5V}{30V}\right)} \times \frac{100^{\circ}C - 60^{\circ}C}{\left[1 + 0.01/^{\circ}C \cdot (100^{\circ}C - 25^{\circ}C)\right] \cdot 60^{\circ}C/W}$$

= 35.3 m Ω

(26)

If the selected FET has an Rds value higher than 35.3 $\Omega$ , then two FETs with an R<sub>DS-ON</sub> less than 141 m $\Omega$  (4 x 35.3 m $\Omega$ ) can be used in parallel. In this case, the temperature rise on each FET will not go to Tj\_max because each FET is now dissipating only half of the total power.

#### TOP FET SELECTION

The top FET has two types of losses: switching loss and conduction loss. The switching losses mainly consist of crossover loss and losses related to the low-side FET body diode reverse recovery. Since it is rather difficult to estimate the switching loss, a general starting point is to allot 60% of the top FET thermal capacity to switching losses. The best way to precisely determine switching losses is through bench testing. The equation for calculating the on resistance of the top FET is thus:

$$R_{ds_{max}} = \frac{V_{in_{min}} \cdot \cdot \cdot 4}{I_{max}^{2} \cdot V_{nom}} x$$

$$\frac{T_{j_{max}} - T_{a_{max}}}{\left[1 + TC \cdot (T_{j_{max}} - 25^{\circ}C/W)\right] \cdot R_{\theta ja}}$$

(27)

Example: Tj\_max = 100°C, Ta\_max = 60°C, Rqja = 60°C/W, Vin\_min = 5.5V, Vnom = 5V, and Iload\_max = 3.6A.

TEXAS INSTRUMENTS

www.ti.com

(28)

$$R_{ds_max} = \frac{5.5V \times .4}{(3.6A)^2 \times 5V} \times \frac{100^{\circ}\text{C} - 60^{\circ}\text{C}}{[1 + 0.01/^{\circ}\text{C} \cdot (100^{\circ}\text{C} - 25^{\circ}\text{C})] \cdot 60^{\circ}\text{C}/\text{W}}$$

= 13 m Ω

When using FETs in parallel, the same guidelines apply to the top FET as apply to the bottom FET.

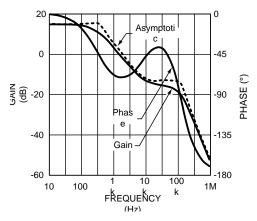

# Loop Compensation

The general purpose of loop compensation is to meet static and dynamic performance requirements while maintaining stability. Loop gain is what is usually checked to determine small-signal performance. Loop gain is equal to the product of control-output transfer function and the feedback transfer function (the compensation network transfer function). Generally speaking it is desirable to have a loop gain slope that is roughly -20dB /decade from a very low frequency to well beyond the crossover frequency. The crossover frequency should not exceed one-fifth of the switching frequency. The higher the bandwidth, the faster the load transient response speed will be. However, if the duty cycle saturates during a load transient, further increasing the small signal bandwidth will not help. Since the control-output transfer function usually has very limited low frequency gain, it is a good idea to place a pole in the compensation at zero frequency, so that the low frequency gain will be relatively large. A large DC gain means high DC regulation accuracy (i.e. DC voltage changes little with load or line variations). The rest of the compensation scheme depends highly on the shape of the control-output plot.

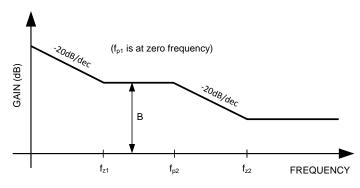

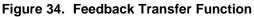

Figure 33. Control-Output Transfer Function

As shown in Figure 33, the control-output transfer function consists of one pole (fp), one zero (fz), and a double pole at fn (half the switching frequency). The following can be done to create a -20dB /decade roll-off of the loop gain: Place the first pole at 0Hz, the first zero at fp, the second pole at fz, and the second zero at fn. The resulting feedback transfer function is shown in Figure 34.

The control-output corner frequencies, and thus the desired compensation corner frequencies, can be determined approximately by the following equations:

$$f_{z} = \frac{1}{2\pi R_{e}C_{o}}$$

$$f_{P} = \frac{1}{2\pi R_{O}C_{O}} + \frac{1 - D - .5}{2\pi f L C_{O}}$$

(29)

Since fp is determined by the output network, it will shift with loading (Ro). It is best to use a minimum lout value of approximately 100mA when determining the maximum Ro value.

Example: Re = 20 m $\Omega$ , Co = 100 uF, Romax = 5V/100 mA = 50 $\Omega$ :

$$f_{z} = \frac{1}{2\pi \cdot 20 \text{ m}\Omega \cdot 100 \,\mu\text{F}} = 80 \,\text{kHz}$$

$$f_{p \text{ min}} = \frac{1}{2\pi \cdot 50\Omega \cdot 100 \,\mu\text{F}} + \frac{1}{2\pi \cdot 200 \text{k} \cdot 8 \,\mu \cdot 100 \,\mu\text{F}} = 995 \,\text{Hz}$$

(32)

First determine the minimum frequency (fpmin) of the pole across the expected load range, then place the first compensation zero at or below that value. Once fpmin is determined, Rc1 should be calculated using:

$$R_{c1} = \frac{B}{gm} \left( \frac{R_1 + R_2}{R_1} \right)$$

where

- B is the desired gain in V/V at fp (fz1)

- gm is the transconductance of the error amplifier

- R1 and R2 are the feedback resistors

A gain value around 10dB (3.3v/v) is generally a good starting point.

Example: B = 3.3v/v, gm = 650m, R1 =  $20 \text{ kK}\Omega$ , R2 =  $60.4 \text{ k}\Omega$ :

$$R_{c1} = \frac{3.3}{650\,\mu} \left( \frac{20\,k + 60.4\,k}{20\,k} \right) = 20.4\,k\,\Omega \simeq 20\,k\,\Omega$$

(34)

Bandwidth will vary proportional to the value of Rc1. Next, Cc1 can be determined with the following equation:

$$C_{c1} = \frac{1}{2\pi \cdot f_{p \min} \cdot R_{c1}}$$

(35)

Example: fpmin = 995 Hz, Rc1 = 20 k $\Omega$ :

$$C_{c1} = \frac{1}{2\pi \cdot 995 \, \text{Hz} \cdot 20 \, \text{k}\Omega} \cong 8 \, \text{nF}$$

(36)

The compensation network (Figure 35) will also introduce a low frequency pole which will be close to 0 Hz.

A second pole should also be placed at fz. This pole can be created with a single capacitor Cc2 and a shorted Rc2 (see Figure 35). The minimum value for this capacitor can be calculated by:

$$C_{c2 \min} = \frac{1}{2\pi \cdot f_z \cdot R_{c1}}$$

(37)

Cc2 may not be necessary, however it does create a more stable control loop. This is especially important with high load currents and in current sharing mode.

Example: fz = 80 kHz,  $Rc1 = 20 \text{ k}\Omega$ :

$$C_{c2 \min} = \frac{1}{2\pi \cdot 80 \text{ kHz} \cdot 20 \text{ k}\Omega} \cong 100 \text{ pF}$$

(38)

#### Copyright © 2003–2013, Texas Instruments Incorporated

SNVS219K-JUNE 2003-REVISED APRIL 2013

(33)

(30)

www.ti.com

(39)

A second zero can also be added with a resistor in series with Cc2. If used, this zero should be placed at fn, where the control to output gain rolls off at -40dB/dec. Generally, fn will be well below the 0dB level and thus will have little effect on stability. Rc2 can be calculated with the following equation:

$$R_{c2} = \frac{1}{2\pi \cdot f_n \cdot C_{c2}}$$

Figure 35. Compensation Network

## PCB Layout Considerations

To produce an optimal power solution with the LM5642 series, good layout and design of the PCB are as important as the component selection. The following are several guidelines to aid in creating a good layout.

## KELVIN TRACES FOR SENSE LINES

When using the current sense resistor to sense the load current connect the KS pin using a separate trace to VIN, as close as possible to the current-sense resistor. The RSNS pin should be connected using a separate trace to the low-side of the current sense resistor. The traces should be run parallel to each other to give common mode rejection. Although it can be difficult in a compact design, these traces should stay away from the output inductor and switch node if possible, to avoid coupling stray flux fields. When a current-sense resistor is not used the KS pin should be connected as close as possible to the drain node of the upper MOSFET and the RSNS pin should be connected as close as possible to the source of the upper MOSFET using Kelvin traces. To further help minimize noise pickup on the sense lines is to use RC filtering on the KS and RSNS pins.

## SEPARATE PGND AND SGND