Errata sheet

## STM32F405/407xx and STM32F415/417xx device errata

## **Applicability**

This document applies to the part numbers of STM32F405/407xx and STM32F415/417xx devices and the device variants as stated in this page.

It gives a summary and a description of the device errata, with respect to the device datasheet and reference manual RM0090. Deviation of the real device behavior from the intended device behavior is considered to be a device limitation. Deviation of the description in the reference manual or the datasheet from the intended device behavior is considered to be a documentation erratum. The term *"errata"* applies both to limitations and documentation errata.

#### Table 1. Device summary

| Reference    | Part numbers                                                                 |

|--------------|------------------------------------------------------------------------------|

| STM32F405xx  | STM32F405OG, STM32F405OE, STM32F405RG, STM32F405VG, STM32F405ZG              |

| STM32F407xx, | STM32F407IG, STM32F407VG, STM32F407ZG, STM32F407ZE, STM32F407IE, STM32F407VE |

| STM32F415xx  | STM32F415OG, STM32F415RG, STM32F415VG, STM32F415ZG                           |

| STM32F417xx  | STM32F417VG, STM32F417IG, STM32F417ZG, STM32F417VE, STM32F417ZE, STM32F417IE |

### Table 2. Device variants

| Reference                 | Silicon revision codes        |                       |  |  |  |

|---------------------------|-------------------------------|-----------------------|--|--|--|

| Reference                 | Device marking <sup>(1)</sup> | REV_ID <sup>(2)</sup> |  |  |  |

|                           | А                             | 0x1000                |  |  |  |

|                           | Z                             | 0x1001                |  |  |  |

|                           | 1                             | 0x1003                |  |  |  |

| STM32F405xx, STM32F407xx, | 2                             | 0x1007                |  |  |  |

| STM32F415xx, STM32F417xx  | Y                             | 0x100F                |  |  |  |

|                           | 4                             | 0x100F                |  |  |  |

|                           | 5                             | 0x101F                |  |  |  |

|                           | 6                             | UX TO IF              |  |  |  |

1. Refer to the device datasheet for how to identify this code on different types of package.

2. REV\_ID[15:0] bitfield of DBGMCU\_IDCODE register.

## 1 Summary of device errata

The following table gives a quick reference to the STM32F405/407xx and STM32F415/417xx device limitations and their status:

- A = limitation present, workaround available

- N = limitation present, no workaround available

- P = limitation present, partial workaround available

"-" = limitation absent

Applicability of a workaround may depend on specific conditions of target application. Adoption of a workaround may cause restrictions to target application. Workaround for a limitation is deemed partial if it only reduces the rate of occurrence and/or consequences of the limitation, or if it is fully effective for only a subset of instances on the device or in only a subset of operating modes, of the function concerned.

|          |         |                                                                                             |            |            |            | Sta        | itus       |            |            |            |

|----------|---------|---------------------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Function | Section | Limitation                                                                                  | Re<br>v. A | Re<br>v. Z | Re<br>v. 1 | Re<br>v. 2 | Re<br>v. Y | Re<br>v. 4 | Re<br>v. 5 | Re<br>v. 6 |

|          | 2.1.1   | Interrupted loads to SP can cause erroneous behavior                                        | A          | А          | А          | А          | А          | А          | А          | А          |

| Core     | 2.1.2   | VDIV or VSQRT instructions might not complete correctly when very short ISRs are used       | А          | А          | А          | А          | А          | А          | А          | А          |

|          | 2.1.3   | Store immediate overlapping exception return operation might vector to incorrect interrupt  | А          | А          | А          | А          | А          | А          | А          | А          |

|          | 2.2.1   | ART Accelerator prefetch queue instruction is not supported                                 | N          | -          | -          | -          | -          | -          | -          | -          |

|          | 2.2.2   | MCU device ID is incorrect                                                                  | Α          | -          | -          | -          | -          | -          | -          | -          |

|          | 2.2.3   | Debugging Stop mode and SysTick timer                                                       | Α          | Α          | Α          | Α          | Α          | А          | Α          | Α          |

|          | 2.2.4   | Debugging Stop mode with WFE entry                                                          | Α          | Α          | Α          | Α          | Α          | А          | Α          | А          |

|          | 2.2.5   | Debugging Sleep/Stop mode with WFE/WFI entry                                                | Α          | Α          | Α          | Α          | Α          | А          | Α          | А          |

|          | 2.2.6   | 2.2.6 Wake-up sequence from Standby mode when using more than one wake-up source            |            | Α          | А          | А          | А          | А          | А          | А          |

|          | 2.2.7   | Full JTAG configuration without NJTRST pin cannot be used                                   | А          | А          | А          | А          | А          | А          | А          | A          |

|          | 2.2.8   | PDR_ON pin not available on LQFP100 package except for revision A devices                   | -          | N          | N          | N          | N          | N          | N          | N          |

| System   | 2.2.9   | Incorrect BOR option byte when consecutively<br>programming BOR option byte                 | A          | A          | А          | А          | А          | А          | А          | A          |

|          | 2.2.10  | Configuration of PH10 and PI10 as external interrupts is erroneous                          | N          | N          | N          | N          | N          | N          | N          | N          |

|          | 2.2.11  | Slowing down APB clock during a DMA transfer                                                | Α          | Α          | Α          | Α          | Α          | Α          | Α          | А          |

|          | 2.2.12  | MPU attribute to RTC and IWDG registers incorrectly managed                                 | Α          | Α          | А          | А          | А          | А          | А          | А          |

|          | 2.2.13  | Delay after an RCC peripheral clock enabling                                                | Α          | Α          | Α          | Α          | Α          | А          | А          | А          |

|          | 2.2.14  | Battery charge monitoring lower than 2.4 V                                                  | Р          | Р          | Р          | Р          | Р          | Р          | Р          | Р          |

|          | 2.2.15  | Internal noise impacting the ADC accuracy                                                   | Α          | Α          | Α          | Α          | Α          | А          | А          | А          |

|          | 2.2.16  | RDP level 2 and sector write protection configuration                                       | Α          | Α          | Α          | Α          | Α          | А          | А          | А          |

|          | 2.2.17  | Possible delay in backup domain protection disabling/enabling after programming the DBP bit | A          | А          | А          | А          | А          | А          | А          | А          |

|          | 2.2.18  | PC13 signal transitions disturb LSE                                                         | Α          | Α          | Α          | Α          | Α          | А          | Α          | А          |

#### Table 3. Summary of device limitations

## STM32F405/407xx and STM32F415/417xx

Summary of device errata

|          |         |                                                                                                                                               |            |            |            | Sta        | itus       |            |            |            |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Function | Section | Limitation                                                                                                                                    | Re<br>v. A | Re<br>v. Z | Re<br>v. 1 | Re<br>v. 2 | Re<br>v. Y | Re<br>v. 4 | Re<br>v. 5 | Re<br>v. 6 |

| System   | 2.2.19  | In some specific cases, DMA2 data corruption occurs<br>when managing AHB and APB2 peripherals in a<br>concurrent way                          | А          | A          | A          | А          | А          | А          | A          | А          |

|          | 2.3.1   | Dummy read cycles inserted when reading synchronous memories                                                                                  | N          | N          | N          | N          | N          | N          | N          | N          |

| FSMC     | 2.3.2   | FSMC synchronous mode and NWAIT signal disabled                                                                                               | А          | А          | А          | А          | A          | А          | А          | А          |

|          | 2.3.3   | FSMC NOR/PSRAM controller: asynchronous read access on bank 2 to 4 returns wrong data when bank 1 is in synchronous mode (BURSTEN bit is set) | A          | A          | A          | A          | A          | A          | A          | А          |

| ADC      | 2.4.1   | ADC sequencer modification during conversion                                                                                                  | Α          | А          | А          | Α          | Α          | Α          | Α          | Α          |

|          | 2.5.1   | DMA request not automatically cleared by clearing DMAEN                                                                                       | А          | А          | А          | А          | Α          | А          | А          | А          |

| DAC      | 2.5.2   | DMA underrun flag not set when an internal trigger<br>is detected on the clock cycle of the DMA request<br>acknowledge                        | N          | N          | N          | N          | N          | N          | N          | N          |

|          | 2.6.1   | PWM re-enabled in automatic output enable mode despite of system break                                                                        | Р          | Р          | Ρ          | Ρ          | Р          | Ρ          | Ρ          | Ρ          |

| TIM      | 2.6.3   | Consecutive compare event missed in specific conditions                                                                                       | N          | N          | N          | N          | N          | N          | N          | N          |

| 2.6.4    |         | Output compare clear not working with external counter reset                                                                                  | Р          | Р          | Р          | Р          | Р          | Р          | Р          | Ρ          |

| 2        | 2.7.1   | RVU flag not reset in Stop                                                                                                                    | Α          | А          | А          | Α          | Α          | Α          | А          | Α          |

|          | 2.7.2   | PVU flag not reset in Stop                                                                                                                    | Α          | Α          | А          | Α          | Α          | Α          | Α          | Α          |

| IWDG     | 2.7.3   | RVU flag not cleared at low APB clock frequency                                                                                               | Α          | А          | А          | Α          | Α          | Α          | А          | Α          |

|          | 2.7.4   | PVU flag not cleared at low APB clock frequency                                                                                               | Α          | Α          | А          | Α          | Α          | А          | А          | Α          |

|          | 2.8.1   | Spurious tamper detection when disabling the tamper channel                                                                                   | N          | N          | Ν          | N          | N          | N          | N          | N          |

|          | 2.8.2   | RTC calendar registers are not locked properly                                                                                                | Α          | А          | Α          | Α          | Α          | Α          | А          | Α          |

|          | 2.8.3   | RTC interrupt can be masked by another RTC interrupt                                                                                          | А          | А          | А          | А          | А          | А          | А          | A          |

| RTC      | 2.8.4   | Calendar initialization may fail in case of consecutive INIT mode entry                                                                       | Α          | А          | А          | А          | Α          | А          | А          | А          |

|          | 2.8.5   | Alarm flag may be repeatedly set when the core is stopped in debug                                                                            | N          | N          | N          | N          | N          | N          | N          | N          |

|          | 2.8.6   | Detection of a tamper event occurring before<br>enabling the tamper detection is not supported in<br>edge detection mode                      | А          | А          | A          | А          | А          | А          | А          | А          |

|          | 2.9.1   | SMBus standard not fully supported                                                                                                            | Α          | А          | А          | Α          | Α          | Α          | А          | Α          |

|          | 2.9.2   | Start cannot be generated after a misplaced Stop                                                                                              | Α          | А          | А          | Α          | Α          | Α          | А          | Α          |

|          | 2.9.3   | Mismatch on the "Setup time for a repeated Start condition" timing parameter                                                                  |            | А          | А          | А          | A          | А          | А          | А          |

| I2C      | 2.9.4   | Data valid time ( $t_{VD;DAT}$ ) violated without the OVR flag being set                                                                      | А          | А          | А          | А          | А          | А          | А          | А          |

|          | 2.9.5   | Both SDA and SCL maximum rise times (t <sub>r</sub> ) violated when the VDD_I2C bus voltage is higher than $((V_{DD}+0.3)/0.7)~V$             | А          | A          | A          | А          | А          | A          | A          | A          |

|          | 2.9.6   | Spurious bus error detection in Master mode                                                                                                   | Α          | Α          | А          | Α          | Α          | Α          | Α          | Α          |

## STM32F405/407xx and STM32F415/417xx

Summary of device errata

|          |         |                                                                                                                      | Status     |            |            |            |            |            |            |            |

|----------|---------|----------------------------------------------------------------------------------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|

| Function | Section | Limitation                                                                                                           | Re<br>v. A | Re<br>v. Z | Re<br>v. 1 | Re<br>v. 2 | Re<br>v. Y | Re<br>v. 4 | Re<br>v. 5 | Re<br>v. 6 |

|          | 2.10.1  | Idle frame is not detected if the receiver clock speed is deviated                                                   | N          | N          | N          | N          | N          | N          | N          | N          |

|          | 2.10.2  | In full-duplex mode, the Parity Error (PE) flag can be cleared by writing to the data register                       | А          | А          | А          | А          | А          | А          | А          | A          |

|          | 2.10.3  | Parity Error (PE) flag is not set when receiving in Mute mode using address mark detection                           | N          | N          | N          | N          | N          | N          | N          | N          |

|          | 2.10.4  | Break frame is transmitted regardless of CTS input line status                                                       | N          | N          | N          | N          | N          | N          | N          | N          |

| USART    | 2.10.5  | RTS signal abnormally driven low after a protocol violation                                                          | А          | А          | А          | А          | А          | А          | А          | A          |

|          | 2.10.6  | Start bit detected too soon when sampling for NACK signal from the smartcard                                         | N          | N          | N          | N          | N          | N          | N          | N          |

|          | 2.10.7  | Break request can prevent the transmission complete flag (TC) from being set                                         | А          | А          | А          | А          | А          | А          | А          | A          |

|          | 2.10.8  | Guard time not respected when data are sent on TXE events                                                            | А          | А          | А          | А          | А          | А          | A          | A          |

|          | 2.10.9  | RTS is active while RE or UE = 0                                                                                     | А          | А          | А          | Α          | А          | Α          | Α          | Α          |

|          | 2.11.4  | Wrong CRC calculation when the polynomial is even                                                                    | Α          | А          | А          | Α          | Α          | Α          | Α          | Α          |

| SPI/I2S  | 2.11.5  | Corrupted last bit of data and/or CRC received in Master mode with delayed SCK feedback                              | А          | А          | А          | А          | А          | А          | A          | A          |

|          | 2.11.6  | BSY flag may stay high at the end of a data transfer in Slave mode                                                   |            | А          | А          | А          | А          | А          | А          | Α          |

|          | 2.11.7  | I2S2 in full-duplex mode may not work properly when<br>SCK and WS signals are mapped on PI1 and PI0,<br>respectively | А          | A          | А          | А          | A          | А          | А          | А          |

|          | 2.11.1  | BSY bit may stay high when SPI is disabled                                                                           | Α          | А          | А          | Α          | А          | Α          | Α          | Α          |

|          | 2.11.2  | In I <sup>2</sup> S slave mode, enabling I2S while WS is active causes desynchronization                             |            | А          | А          | А          | А          | А          | А          | A          |

|          | 2.11.3  | Anticipated communication upon SPI transit from slave receiver to master                                             | А          | А          | А          | А          | А          | А          | A          | A          |

|          | 2.12.1  | Wrong data written during SDIO hardware flow control                                                                 | N          | N          | N          | N          | N          | N          | N          | N          |

|          | 2.12.2  | Wrong CCRCFAIL status after a response without CRC is received                                                       | А          | А          | А          | А          | А          | А          | Α          | A          |

| SDIO     | 2.12.3  | SDIO clock divider Bypass mode may not work properly                                                                 | А          | А          | А          | А          | А          | А          | А          | A          |

|          | 2.12.4  | Data corruption in SDIO clock dephasing (NEGEDGE) mode                                                               | N          | N          | N          | N          | N          | N          | N          | N          |

|          | 2.12.5  | CE-ATA multiple write command and card busy signal management                                                        | А          | А          | А          | А          | А          | А          | Α          | A          |

| 2.12.6   |         | No underrun detection with wrong data transmission                                                                   | Α          | А          | А          | Α          | Α          | Α          | А          | Α          |

| bxCAN    | 2.13.1  | bxCAN time-triggered communication mode not supported                                                                |            | N          | N          | N          | N          | N          | N          | N          |

|          | 2.14.3  | Data in RxFIFO is overwritten when all channels are disabled simultaneously                                          | А          | А          | А          | А          | А          | А          | А          | A          |

| OTG_FS   | 2.14.4  | OTG host blocks the receive channel when receiving IN packets and no TxFIFO is configured                            | А          | А          | А          | А          | А          | А          | А          | A          |

|          | 2.14.5  | Host channel-halted interrupt not generated when the channel is disabled                                             | А          | А          | А          | А          | А          | А          | А          | А          |

## STM32F405/407xx and STM32F415/417xx

Summary of device errata

|          |         |                                                                                                                                  | Status |            |            |            |            |            |            |            |  |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------|--------|------------|------------|------------|------------|------------|------------|------------|--|

| Function | Section | n Limitation                                                                                                                     |        | Re<br>v. Z | Re<br>v. 1 | Re<br>v. 2 | Re<br>v. Y | Re<br>v. 4 | Re<br>v. 5 | Re<br>v. 6 |  |

|          | 2.14.6  | Wrong software-read OTG_FS_DCFG register values                                                                                  | А      | А          | А          | A          | A          | А          | А          | А          |  |

| OTG_FS   | 2.14.1  | Transmit data FIFO is corrupted when a write<br>sequence to the FIFO is interrupted with accesses<br>to certain OTG_FS registers | A      | A          | A          | A          | A          | A          | A          | A          |  |

|          | 2.14.2  | Host packet transmission may hang when connecting through a hub to a low-speed device                                            | N      | N          | N          | N          | N          | N          | N          | N          |  |

|          | 2.15.1  | Transmit data FIFO is corrupted when a write<br>sequence to the FIFO is interrupted with accesses<br>to certain OTG_HS registers | А      | A          | А          | А          | А          | А          | А          | А          |  |

| OTG_HS 2 | 2.15.2  | Host packet transmission may hang when connecting<br>the full speed interface through a hub to a low-speed<br>device             | N      | N          | N          | N          | N          | N          | N          | N          |  |

|          | 2.16.1  | Incorrect L3 checksum is inserted in transmitted IPv6<br>packets without TCP, UDP or ICMP payloads                               | А      | А          | А          | А          | Α          | А          | А          | А          |  |

|          | 2.16.2  | The ethernet MAC processes invalid extension headers in the received IPv6 frames                                                 |        | N          | N          | N          | N          | N          | N          | N          |  |

|          | 2.16.3  | MAC stuck in the idle state on receiving the TxFIFO<br>flush command exactly one clock cycle after a<br>transmission completes   |        | Ρ          | Ρ          | Р          | Р          | Ρ          | Р          | Ρ          |  |

|          | 2.16.4  | Transmit frame data corruption                                                                                                   | А      | А          | А          | Α          | Α          | А          | Α          | Α          |  |

|          | 2.16.5  | Incorrect status and corrupted frames when RxFIFO overflow occurs on the penultimate word of Rx frames                           | A      | A          | А          | A          | A          | А          | А          | A          |  |

| ETH      | 2.16.6  | Successive write operations to the same register might not be fully taken into account                                           | А      | А          | А          | А          | А          | А          | А          | А          |  |

|          | 2.16.7  | Incorrect remote wakeup on global unicast packet                                                                                 | Р      | Р          | Р          | Р          | Р          | Р          | Р          | Р          |  |

|          | 2.16.8  | Overflow status bits of missed frame and buffer<br>overflow counters are cleared without a read<br>operation                     |        | A          | А          | A          | А          | А          | А          | А          |  |

|          | 2.16.9  | MAC may provide incorrect Rx status for the MAC control frames when receive checksum offload is enabled                          |        | А          | А          | А          | А          | А          | А          | A          |  |

|          | 2.16.10 | MAC may provide an inaccurate Rx status when receive checksum offload is enabled in cut-through mode                             | Ρ      | Р          | Ρ          | Р          | Р          | Ρ          | Ρ          | Р          |  |

|          | 2.16.11 | MAC may not drop received giant error frames                                                                                     | Α      | Α          | Α          | Α          | Α          | А          | А          | Α          |  |

The following table gives a quick reference to the documentation errata.

### Table 4. Summary of device documentation errata

| Function | Section | Documentation erratum                 |

|----------|---------|---------------------------------------|

| TIM      | 2.6.2   | TRGO and TRGO2 trigger output failure |

## 2 Description of device errata

The following sections describe the errata of the applicable devices with Arm<sup>®</sup> core and provide workarounds if available. They are grouped by device functions.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

### 2.1 Core

Reference manual and errata notice for the Arm<sup>®</sup> Cortex<sup>®</sup>-M4F core revision r0p1 is available from http:// infocenter.arm.com.

#### 2.1.1 Interrupted loads to SP can cause erroneous behavior

This limitation is registered under Arm ID number 752770 and classified into "Category B". Its impact to the device is minor.

#### Description

If an interrupt occurs during the data-phase of a single word load to the stack-pointer (SP/R13), erroneous behavior can occur. In all cases, returning from the interrupt will result in the load instruction being executed an additional time. For all instructions performing an update to the base register, the base register will be erroneously updated on each execution, resulting in the stack-pointer being loaded from an incorrect memory location.

The affected instructions that can result in the load transaction being repeated are:

- LDR SP, [Rn],#imm

- LDR SP, [Rn,#imm]!

- LDR SP, [Rn,#imm]

- LDR SP, [Rn]

- LDR SP, [Rn,Rm]

The affected instructions that can result in the stack-pointer being loaded from an incorrect memory address are:

- LDR SP,[Rn],#imm

- LDR SP,[Rn,#imm]!

As compilers do not generate these particular instructions, the limitation is only likely to occur with hand-written assembly code.

#### Workaround

Both issues may be worked around by replacing the direct load to the stack-pointer, with an intermediate load to a general-purpose register followed by a move to the stack-pointer.

#### 2.1.2 VDIV or VSQRT instructions might not complete correctly when very short ISRs are used

This limitation is registered under Arm ID number 776924 and classified into "Category B". Its impact to the device is limited.

#### Description

The VDIV and VSQRT instructions take 14 cycles to execute. When an interrupt is taken a VDIV or VSQRT instruction is not terminated, and completes its execution while the interrupt stacking occurs. If lazy context save of floating point state is enabled then the automatic stacking of the floating point context does not occur until a floating point instruction is executed inside the interrupt service routine.

Lazy context save is enabled by default. When it is enabled, the minimum time for the first instruction in the interrupt service routine to start executing is 12 cycles. In certain timing conditions, and if there is only one or two instructions inside the interrupt service routine, then the VDIV or VSQRT instruction might not write its result to the register bank or to the FPSCR.

The failure occurs when the following condition is met:

- 1. The floating point unit is enabled

- 2. Lazy context saving is not disabled

- 3. A VDIV or VSQRT is executed

- 4. The destination register for the VDIV or VSQRT is one of s0 s15

- 5. An interrupt occurs and is taken

- 6. The interrupt service routine being executed does not contain a floating point instruction

- 7. Within 14 cycles after the VDIV or VSQRT is executed, an interrupt return is executed

A minimum of 12 of these 14 cycles are utilized for the context state stacking, which leaves 2 cycles for instructions inside the interrupt service routine, or 2 wait states applied to the entire stacking sequence (which means that it is not a constant wait state for every access).

In general, this means that if the memory system inserts wait states for stack transactions (that is, external memory is used for stack data), then this erratum cannot be observed.

The effect of this erratum is that the VDIV or VQSRT instruction does not complete correctly and the register bank and FPSCR are not updated, which means that these registers hold incorrect, out of date, data.

#### Workaround

A workaround is only required if the floating point unit is enabled. A workaround is not required if the stack is in external memory.

There are two possible workarounds:

- Disable lazy context save of floating point state by clearing LSPEN to 0 (bit 30 of the FPCCR at address 0xE000EF34).

- Ensure that every interrupt service routine contains more than 2 instructions in addition to the exception return instruction.

### 2.1.3 Store immediate overlapping exception return operation might vector to incorrect interrupt

This limitation is registered under Arm ID number 838869 and classified into "Category B (rare)". Its impact to the device is minor.

#### Description

The core includes a write buffer that permits execution to continue while a store is waiting on the bus. Under specific timing conditions, during an exception return while this buffer is still in use by a store instruction, a late change in selection of the next interrupt to be taken might result in there being a mismatch between the interrupt acknowledged by the interrupt controller and the vector fetched by the processor.

The failure occurs when the following condition is met:

- 1. The handler for interrupt A is being executed.

- 2. Interrupt B, of the same or lower priority than interrupt A, is pending.

- 3. A store with immediate offset instruction is executed to a bufferable location.

- STR/STRH/STRB <Rt>, [<Rn>,#imm]

- STR/STRH/STRB <Rt>, [<Rn>,#imm]!

- STR/STRH/STRB <Rt>, [<Rn>],#imm

- 4. Any number of additional data-processing instructions can be executed.

- 5. A BX instruction is executed that causes an exception return.

- 6. The store data has wait states applied to it such that the data is accepted at least two cycles after the BX is executed.

- Minimally, this is two cycles if the store and the BX instruction have no additional instructions between them.

- The number of wait states required to observe this erratum needs to be increased by the number of cycles between the store and the interrupt service routine exit instruction.

- 7. Before the bus accepts the buffered store data, another interrupt C is asserted which has the same or lower priority as A, but a greater priority than B.

#### Example:

The processor should execute interrupt handler C, and on completion of handler C should execute the handler for B. If the conditions above are met, then this erratum results in the processor erroneously clearing the pending state of interrupt C, and then executing the handler for B twice. The first time the handler for B is executed it will be at interrupt C's priority level. If interrupt C is pended by a level-based interrupt which is cleared by C's handler then interrupt C will be pended again once the handler for B has completed and the handler for C will be executed.

As the STM32 interrupt C is level based, it eventually becomes pending again and is subsequently handled.

#### Workaround

For software not using the memory protection unit, this erratum can be worked around by setting DISDEFWBUF in the Auxiliary Control Register.

In all other cases, the erratum can be avoided by ensuring a DSB occurs between the store and the BX instruction. For exception handlers written in C, this can be achieved by inserting the appropriate set of intrinsics or inline assembly just before the end of the interrupt function, for example:

#### ARMCC:

```

...

__schedule_barrier();

__asm{DSB};

__schedule_barrier();

}

```

#### GCC:

```

...

_asm volatile ("dsb 0xf"::::"memory");

}

```

## 2.2 System

#### 2.2.1 ART Accelerator prefetch queue instruction is not supported

#### Description

The ART Accelerator prefetch queue instruction is not supported on revision A devices. This limitation does not prevent the ART Accelerator from using the cache enable/disable capability and the selection of the number of wait states according to system frequency.

#### Workaround

- Revision A: None.

- Other revisions: fixed.

### 2.2.2 MCU device ID is incorrect

#### Description

On revision A devices, the STM32F40x and STM32F41x have the same MCU device ID as the STM32F20x and STM32F21x devices. Reading the revision identifier returns 0x2000 instead of 0x1000. The device ID and revision ID can be read from address 0xE004 2000.

#### Workaround

- Revision A:

- To differentiate the STM32F4xxx from the STM32F2xxx series, read the MCU device ID and the core device:

- For STM32F2xxx

- MCU device ID = STM32F2xxx device ID

- Core device = Cortex<sup>®</sup>-M3

- For STM32F4xxx

- MCU device ID = STM32F4xxx device ID

- Core device = Cortex<sup>®</sup>-M4

- Other revisions: fixed.

#### 2.2.3 Debugging Stop mode and SysTick timer

#### Description

If the SysTick timer interrupt is enabled during the Stop mode debug (DBG\_STOP bit set in the DBGMCU\_CR register), it wakes up the system from Stop mode.

#### Workaround

To debug the Stop mode, disable the SysTick timer interrupt.

#### 2.2.4 Debugging Stop mode with WFE entry

#### Description

When the Stop debug mode is enabled (DBG\_STOP bit set in the DBGMCU\_CR register), the software debugging is allowed during Stop mode. However, if the application software uses the WFE instruction to enter Stop mode, after wake-up, some instructions may be missed if the WFE is followed by sequential instructions. This affects only Stop debug mode with WFE entry.

#### Workaround

To debug Stop mode with WFE entry, the WFE instruction must be inside a dedicated function with one instruction (NOP) between the execution of the WFE and the Bx LR. For example:

```

__asm void _WFE(void)

WFE

NOP

BX lr }

```

#### 2.2.5 Debugging Sleep/Stop mode with WFE/WFI entry

#### Description

When the Sleep debug or Stop debug mode is enabled (DBG\_SLEEP bit or DBG\_STOP bit are set in the DBGMCU\_CR register), software debugging is allowed during Sleep or Stop mode. After wake-up, some unreachable instructions can be executed if the following conditions are met:

- The application software disables the Prefetch queue,

- the number of wait states configured for the flash memory interface is higher than zero, and

- the linker places the WFE or WFI instruction on a 4-byte aligned addresses (0x080xx xxx4).

#### Workaround

Apply one of the following measures:

- Add three NOPs after WFI/WFE instruction.

- Keep one AHB master active during Sleep (example keep DMA1 or DMA2 RCC clock enable bit set).

- Execute WFI/WFE instruction from routines inside the SRAM.

### 2.2.6 Wake-up sequence from Standby mode when using more than one wake-up source

#### Description

The various wake-up sources are logically OR-ed in front of the rising-edge detector that generates the wake-up flag (WUF). The WUF needs to be cleared before Standby mode entry, otherwise the MCU wakes up immediately. If one of the configured wake-up sources is kept high during the clearing of the WUF (by setting the CWUF bit), it may mask further wake-up events on the input of the edge detector. As a consequence, the MCU may not be able to wake up from Standby mode.

#### Workaround

To avoid this problem, apply the following sequence before entering Standby mode:

- 1. Disable all used wake-up sources.

- 2. Clear all related wake-up flags.

- 3. Reenable all used wake-up sources.

- 4. Enter Standby mode.

Note: Be aware that, when applying this workaround, if one of the wake-up sources is still kept high, the MCU enters Standby mode but then it wakes up immediately and generates a power reset.

#### 2.2.7 Full JTAG configuration without NJTRST pin cannot be used

#### Description

When using the JTAG debug port in debug mode, the connection with the debugger is lost if the NJTRST pin (PB4) is used as a GPIO. Only the 4-wire JTAG port configuration is impacted.

#### Workaround

Use the SWD debug port instead of the full 4-wire JTAG port.

#### 2.2.8 PDR\_ON pin not available on LQFP100 package except for revision A devices

#### Description

On all device revisions except for revision A, the PDR\_ON pin (pin 99), available on LQFP100 package, is replaced by VSS. As a consequence, the POR/PDR feature is always enabled.

#### Workaround

- Applications using revision A devices with PDR\_ON pin connected to V<sub>DD</sub> (POR/PDR feature enabled): Connect the former PDR ON pin to V<sub>SS</sub> on revision Z devices.

- Applications using revision A devices with PDR\_ON pin connected to V<sub>SS</sub> (POR/PDR feature disabled): No modification is required when migrating to other device revisions. However, it is no longer possible to supply the product from a 1.7 V V<sub>DD</sub> on LQFP100 package since V<sub>DD</sub> minimum value is 1.8 V when the POR/PDR feature is enabled.

#### 2.2.9 Incorrect BOR option byte when consecutively programming BOR option byte

#### Description

When the AHB prescaler is greater than 2, and consecutive BOR option byte program operations are performed without resetting the device, then an incorrect value may be programmed in the BOR option byte.

#### Workaround

To program consecutive BOR option byte values, either configure the AHB prescaler to 1 or 2, or perform a system reset between each BOR option byte program operation.

#### 2.2.10 Configuration of PH10 and PI10 as external interrupts is erroneous

#### Description

PH10 or PI10 is selected as the source for the EXTI10 external interrupt by setting bits EXTI10[3:0] of the SYSCFG\_EXTICR3 register to 0x0111 or 0x1000, respectively. Instead, this operation wrongly enables PH2 and PI2 as external interrupt inputs.

As a result, it is not possible to use PH10/PI10 as interrupt sources if PH2/PI2 are not selected as interrupt source as well. This means that bits EXTI10[3:0] of the SYSCFG\_EXTICR3 register and bits EXTI2[3:0] of the SYSCFG\_EXTICR1 must be programmed to the same value:

- 0x0111 to select PH10/PH2

- 0x1000 to select PI10/PI2

#### Workaround

None.

#### 2.2.11 Slowing down APB clock during a DMA transfer

#### Description

When the CPU modifies the APB clock (slows down the clock by changing the AHB/APB prescaler from 1 to 2, 1 to 4, 1 to 8 or 1 to 16) while the DMA is performing a write access to the same APB peripherals, the current DMA transfer is blocked. Only a system reset recovers.

#### Workaround

Before slowing down the APB clock, wait until the end of the DMA transfer on this APB.

#### 2.2.12 MPU attribute to RTC and IWDG registers incorrectly managed

#### Description

If the MPU is used and the nonbufferable attribute is set to the RTC or IWDG memory map region, the CPU access to the RTC or IWDG registers may be treated as bufferable, provided there is no APB prescaler configured (AHB/APB prescaler is equal to 1).

#### Workaround

If the nonbufferable attribute is required for these registers, perform by software a read after the write to guaranty the completion of the write access.

#### 2.2.13 Delay after an RCC peripheral clock enabling

#### Description

A delay may be observed between an RCC peripheral clock enable and the effective peripheral enabling. It must be taken into account in order to manage the peripheral read/write from/to registers.

This delay depends on the peripheral mapping:

- If the peripheral is mapped on the AHB: the delay may be equal to two AHB cycles.

- If the peripheral is mapped on the APB: the delay may be equal to 1 + (AHB/APB prescaler) cycles.

#### Workaround

Apply one of the following measures:

- Use the DSB instruction to stall the Arm<sup>®</sup> Cortex<sup>®</sup>-M4 CPU pipeline until the instruction has completed.

- Insert "n" NOPs between the RCC enable bit write and the peripheral register writes (n = 2 for AHB peripherals, n = 1 + AHB/APB prescaler for APB peripherals).

- Simply insert a dummy read operation from the corresponding register just after enabling the peripheral clock.

#### 2.2.14 Battery charge monitoring lower than 2.4 V

#### Description

If  $V_{DD} = V_{DDA}$  is lower than or equal to 2.4 V, the  $V_{BAT}$  conversion correctness is not guaranteed in full temperature and voltage ranges. When  $V_{BAT}$  is set, the voltage divider bridge is enabled, and  $V_{BAT}$  / 2 is connected to the ADC input. In order to correctly monitor the battery charge, the input of the ADC must not be higher than  $V_{DDA}$  - 0.6 V. Thus,  $V_{BAT}$  / 2 <  $V_{DD}$  – 0.6 V implies that  $V_{DD}$  > 2.4 V.

#### Workaround

None.  $V_{DD} = V_{DDA}$  must be greater than 2.4 V.

#### 2.2.15 Internal noise impacting the ADC accuracy

#### Description

An internal noise generated on V<sub>DD</sub> supplies and propagated internally may impact the ADC accuracy. This noise is always present whatever the power mode of the MCU (Run or Sleep).

#### Workaround

Use the following sequence to adapt the accuracy level to the application requirements:

- 1. Configure the flash memory ART with prefetch OFF and data + instruction cache ON.

- Use averaging and filtering algorithms on ADC output codes.

For more detailed workarounds, refer to the application note "*How to improve ADC accuracy when using STM32F2xx and STM32F4xx microcontrollers*" (AN4073).

#### 2.2.16 RDP level 2 and sector write protection configuration

#### Description

When the MCU is protected with RDP level2, the configuration of the sector write protection remains changeable by the user code.

#### Workaround

Protect sensitive sectors and the FLASH\_OPTCR register using the Arm<sup>®</sup> Cortex<sup>®</sup>-M MPU (memory protection unit) taking special care of ISR management.

## 2.2.17 Possible delay in backup domain protection disabling/enabling after programming the DBP bit

#### Description

Depending on the AHB/APB1 prescaler, a delay between DBP bit programming and the effective disabling/ enabling of the backup domain protection can be observed and must be taken into account. The higher the APB1 prescaler value, the higher the delay.

#### Workaround

Apply one of the following measures:

- Insert a dummy read operation to the PWR\_CR register just after programming the DBP bit.

- Wait for the end of the operation (reset through the BDRST bit or write to the backup domain) via a polling loop on targeted registers.

#### 2.2.18 PC13 signal transitions disturb LSE

#### Description

The PC13 input/output toggling disturbs the LSE clock. As a result, PC13 may not be usable when LSE is used.

#### Workaround

Use an external clock with the LSE in bypass mode.

## 2.2.19 In some specific cases, DMA2 data corruption occurs when managing AHB and APB2 peripherals in a concurrent way

#### Description

When the DMA2 is managing concurrent requests of AHB and APB2 peripherals, the transfer on the AHB can be performed several times. Impacted peripheral are:

- QUADSPI: indirect mode read and write transfers

- FSMC: read and write operation with external device having FIFO

- GPIO: DMA2 transfers to GPIO registers (in memory-to-peripheral transfer mode). The transfers from the GPIOs register are not impacted.

The data corruption is due to multiple DMA2 accesses over the AHB peripheral port impacting peripherals embedding a FIFO.

For transfer to the internal SRAM through the DMA2 AHB peripheral port, the accesses can be performed several times but without data corruptions in cases of concurrent requests.

#### Workaround

- Use the DMA2 AHB memory port when reading/writing from/to QUADSPI and FSMC instead of DMA2 AHB default peripheral port.

- Use the DMA2 AHB memory port when writing to GPIOs instead of DMA2 AHB default peripheral port.

For more details about DMA controller features, refer to the section *Take benefits of DMA2 controller and* system architecture flexibility of the application note "Using the STM32F2, STM32F4 and STM32F7 Series DMA controller" (AN4031).

### 2.3 FSMC

#### 2.3.1 Dummy read cycles inserted when reading synchronous memories

#### Description

When performing a burst read access from a synchronous memory, two dummy read accesses are performed at the end of the burst cycle whatever the type of burst access.

The extra data values read are not used by the FSMC and there is no functional failure.

#### Workaround

None.

#### 2.3.2 FSMC synchronous mode and NWAIT signal disabled

#### Description

When the FSMC operates in synchronous mode with the NWAIT signal disabled, if the polarity (WAITPOL in the FSMC\_BCRx register) of the NWAIT signal is identical to that of the NWAIT input signal level, the system hangs and no fault is generated.

#### Workaround

Do not set the PD6 port to AF12 (NWAIT input). Configure the NWAIT polarity to active high by setting the WAITPOL bit of the FSMC\_BCRx register.

# 2.3.3 FSMC NOR/PSRAM controller: asynchronous read access on bank 2 to 4 returns wrong data when bank 1 is in synchronous mode (BURSTEN bit is set)

#### Description

If an interrupt occurs during a CPU AHB read access to one NOR/PSRAM bank (bank 2 to 4) which is enabled in asynchronous mode, while bank 1 of the NOR/PSRAM controller is configured in synchronous read mode (BURSTEN bit set), then the FSMC NOR/PSRAM controller returns wrong data. This limitation does not occur when using the DMA or when only bank 1 is used in synchronous mode.

#### Workaround

If multiple banks are enabled in mixed asynchronous and synchronous modes, use any NOR/PSRAM bank for synchronous read accesses, except for bank 1. As a consequence the continuous clock feature is not available.

## 2.4 ADC

#### 2.4.1 ADC sequencer modification during conversion

#### Description

When a software start-of-conversion is used as an ADC trigger, and if the ADC\_SQRx or ADC\_JSQRx register is modified during the conversion, the current conversion is reset and the ADC does not automatically restart the new conversion sequence. The hardware start-of-conversion trigger is not impacted and the ADC automatically restarts the new sequence when the next hardware trigger occurs.

#### Workaround

When a software start-of-conversion is used, apply the following sequence:

- 1. First set the SWSART bit in the ADC\_CR2 register.

- 2. Then restart the new conversion sequence.

## 2.5 DAC

#### 2.5.1 DMA request not automatically cleared by clearing DMAEN

#### Description

Upon an attempt to stop a DMA-to-DAC transfer, the DMA request is not automatically cleared by clearing the DAC channel bit of the DAC\_CR register (DMAEN) or by disabling the DAC clock.

If the application stops the DAC operation while the DMA request is pending, the request remains pending while the DAC is reinitialized and restarted, with the risk that a spurious DMA request is serviced as soon as the DAC is enabled again.

#### Workaround

Apply the following sequence to stop the current DMA-to-DAC transfer and restart the DAC:

1. Check if DMAUDR bit is set in DAC\_CR.

- 2. Clear the DAC channel DMAEN bit.

- 3. Disable the DAC clock.

- 4. Reconfigure the DAC, DMA and the triggers.

- 5. Restart the application.

# 2.5.2 DMA underrun flag not set when an internal trigger is detected on the clock cycle of the DMA request acknowledge

#### Description

When the DAC channel operates in DMA mode (DMAEN of DAC\_CR register set), the DMA channel underrun flag (DMAUDR of DAC\_SR register) fails to rise upon an internal trigger detection if that detection occurs during the same clock cycle as a DMA request acknowledge. As a result, the user application is not informed that an underrun error occurred.

This issue occurs when software and hardware triggers are used concurrently to trigger DMA transfers.

#### Workaround

None.

#### 2.6 TIM

#### 2.6.1 PWM re-enabled in automatic output enable mode despite of system break

#### Description

In automatic output enable mode (AOE bit set in TIMx\_BDTR register), the break input can be used to do a cycle-by-cycle PWM control for a current mode regulation. A break signal (typically a comparator with a current threshold) disables the PWM output(s) and the PWM is re-armed on the next counter period.

However, a system break (typically coming from the CSS Clock security System) is supposed to stop definitively the PWM to avoid abnormal operation (for example with PWM frequency deviation).

In the current implementation, the timer system break input is not latched. As a consequence, a system break indeed disables the PWM output(s) when it occurs, but PWM output(s) is (are) re-armed on the following counter period.

#### Workaround

Preferably, implement control loops with the output clear enable function (OCxCE bit in the TIMx\_CCMR1/CCMR2 register), leaving the use of break circuitry solely for internal and/or external fault protection (AOE bit reset).

#### 2.6.2 TRGO and TRGO2 trigger output failure

#### Description

Some reference manual revisions may omit the following information.

The timers can be linked using ITRx inputs and TRGOx outputs. Additionally, the TRGOx outputs can be used as triggers for other peripherals (for example ADC). Since this circuitry is based on pulse generation, care must be taken when initializing master and slave peripherals or when using different master/slave clock frequencies:

- If the master timer generates a trigger output pulse on TRGOx prior to have the destination peripheral clock enabled, the triggering system may fail.

- If the frequency of the destination peripheral is modified on-the-fly (clock prescaler modification), the triggering system may fail.

As a conclusion, the clock of the slave timer or slave peripheral must be enabled prior to receiving events from the master timer, and must not be changed on-the-fly while triggers are being received from the master timer. This is a documentation issue rather than a product limitation.

#### Workaround

No application workaround is required or applicable as long as the application handles the clock as indicated.

#### 2.6.3 Consecutive compare event missed in specific conditions

#### Description

Every match of the counter (CNT) value with the compare register (CCR) value is expected to trigger a compare event. However, if such matches occur in two consecutive counter clock cycles (as consequence of the CCR value change between the two cycles), the second compare event is missed for the following CCR value changes:

- in edge-aligned mode, from ARR to 0:

- first compare event: CNT = CCR = ARR

- second (missed) compare event: CNT = CCR = 0

- <u>in center-aligned mode while up-counting</u>, from ARR-1 to ARR (possibly a new ARR value if the period is also changed) at the crest (that is, when TIMx\_RCR = 0):

- first compare event: CNT = CCR = (ARR-1)

- second (missed) compare event: CNT = CCR = ARR

- in center-aligned mode while down-counting, from 1 to 0 at the valley (that is, when TIMx\_RCR = 0):

- first compare event: CNT = CCR = 1

- second (missed) compare event: CNT = CCR = 0

This typically corresponds to an abrupt change of compare value aiming at creating a timer clock single-cyclewide pulse in toggle mode.

As a consequence:

- In toggle mode, the output only toggles once per counter period (squared waveform), whereas it is expected to toggle twice within two consecutive counter cycles (and so exhibit a short pulse per counter period).

- In center mode, the compare interrupt flag does note rise and the interrupt is not generated.

Note: The timer output operates as expected in modes other than the toggle mode.

#### Workaround

None.

#### 2.6.4 Output compare clear not working with external counter reset

#### Description

The output compare clear event (ocref\_clr) is not correctly generated when the timer is configured in the following slave modes: Reset mode, Combined reset + trigger mode, and Combined gated + reset mode.

The PWM output remains inactive during one extra PWM cycle if the following sequence occurs:

- 1. The output is cleared by the ocref\_clr event.

- 2. The timer reset occurs before the programmed compare event.

#### Workaround

Apply one of the following measures:

- Use BKIN (or BKIN2 if available) input for clearing the output, selecting the Automatic output enable mode (AOE = 1).

- Mask the timer reset during the PWM ON time to prevent it from occurring before the compare event (for

example with a spare timer compare channel open-drain output connected with the reset signal, pulling the

timer reset line down).

## 2.7 IWDG

### 2.7.1 RVU flag not reset in Stop

#### Description

Successful write to the IWDG\_RLR register raises the RVU flag and prevents further write accesses to the register until the RVU flag is automatically cleared by hardware. However, if the device enters Stop mode while the RVU flag is set, the hardware never clears that flag, and writing to the IWDG\_RLR register is no longer possible.

#### Workaround

Ensure that the RVU flag is cleared before entering Stop mode.

#### 2.7.2 PVU flag not reset in Stop

#### Description

Successful write to the IWDG\_PR register raises the PVU flag and prevents further write accesses to the register until the PVU flag is automatically cleared by hardware. However, if the device enters Stop mode while the PVU flag is set, the hardware never clears that flag, and writing to the IWDG\_PR register is no longer possible.

#### Workaround

Ensure that the PVU flag is cleared before entering Stop mode.

#### 2.7.3 RVU flag not cleared at low APB clock frequency

#### Description

Successful write to the IWDG\_RLR register raises the RVU flag and prevents further write accesses to the register until the RVU flag is automatically cleared by hardware. However, at APB clock frequency lower than twice the IWDG clock frequency, the hardware never clears that flag, and writing to the IWDG\_RLR register is no longer possible.

#### Workaround

Set the APB clock frequency higher than twice the IWDG clock frequency.

#### 2.7.4 PVU flag not cleared at low APB clock frequency

#### Description

Successful write to the IWDG\_PR register raises the PVU flag and prevents further write accesses to the register until the PVU flag is automatically cleared by hardware. However, at APB clock frequency lower than twice the IWDG clock frequency, the hardware never clears that flag, and writing to the IWDG\_PR register is no longer possible.

#### Workaround

Set the APB clock frequency higher than twice the IWDG clock frequency.

## 2.8 RTC

#### 2.8.1 Spurious tamper detection when disabling the tamper channel

#### Description

If the tamper detection is configured for detecting on the falling edge event (TAMPFLT = 00 and TAMPxTRG = 1) and if the tamper event detection is disabled when the tamper pin is at high level, a false tamper event is detected.

#### Workaround

None.

#### 2.8.2 RTC calendar registers are not locked properly

#### Description

When reading the calendar registers with BYPSHAD = 0, the RTC\_TR and RTC\_DR registers may not be locked after reading the RTC\_SSR register. This happens if the read operation is initiated one APB clock period before the shadow registers are updated. This can result in a non-consistency of the three registers. Similarly, the RTC\_DR register can be updated after reading the RTC\_TR register instead of being locked.

#### Workaround

Apply one of the following measures:

- Use BYPSHAD = 1 mode (bypass shadow registers), or

- If BYPSHAD = 0, read SSR again after reading SSR/TR/DR to confirm that SSR is still the same, otherwise read the values again.

#### 2.8.3 RTC interrupt can be masked by another RTC interrupt

#### Description

One RTC interrupt request can mask another RTC interrupt request if they share the same EXTI configurable line. For example, interrupt requests from Alarm A and Alarm B or those from tamper and timestamp events are OR-ed to the same EXTI line (refer to the *EXTI line connections* table in the *Extended interrupt and event controller (EXTI)* section of the reference manual).

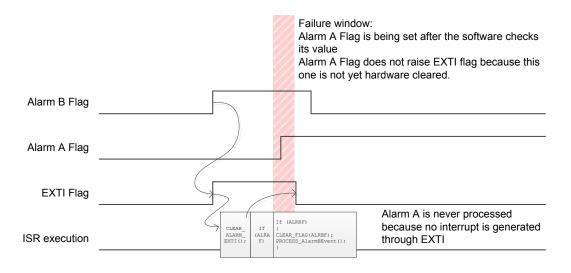

The following code example and figure illustrate the failure mechanism: The Alarm A event is lost (fails to generate interrupt) as it occurs in the failure window, that is, after checking the Alarm A event flag but before the effective clear of the EXTI interrupt flag by hardware. The effective clear of the EXTI interrupt flag is delayed with respect to the software instruction to clear it.

#### Alarm interrupt service routine:

```

void RTC_Alarm_IRQHandler(void)

{

CLEAR_ALARM_EXTI(); /* Clear the EXTI line flag for RTC alarms*/

If(ALRAF) /* Check if Alarm A triggered ISR */

{

CLEAR_FLAG(ALRAF); /* Clear the Alarm A interrupt pending bit */

PROCESS_AlarmAEvent(); /* Process Alarm A event */

}

If(ALRBF) /* Check if Alarm B triggered ISR */

{

CLEAR_FLAG(ALRBF); /* Clear the Alarm B interrupt pending bit */

PROCESS_AlarmBEvent(); /* Process Alarm B event */

}

}

```

#### Figure 1. Masked RTC interrupt

DT47477V1

#### Workaround

In the interrupt service routine, apply three consecutive event flag ckecks - source one, source two, and source one again, as in the following code example:

```

void RTC Alarm IRQHandler(void)

CLEAR ALARM EXTI(); /* Clear the EXTI's line Flag for RTC Alarm */

If (ALRAF) /* Check if AlarmA triggered ISR */

{

CLEAR FLAG(ALRAF); /* Clear the AlarmA interrupt pending bit */

PROCESS AlarmAEvent(); /* Process AlarmA Event */

}

If (ALRBF) /* Check if AlarmB triggered ISR */

{

CLEAR FLAG(ALRBF); /* Clear the AlarmB interrupt pending bit */

PROCESS_AlarmBEvent(); /* Process AlarmB Event */

}

If (ALRAF) /* Check if AlarmA triggered ISR */

{

CLEAR FLAG(ALRAF); /* Clear the AlarmA interrupt pending bit */

PROCESS AlarmAEvent(); /* Process AlarmA Event */

```

#### 2.8.4 Calendar initialization may fail in case of consecutive INIT mode entry

#### Description

If the INIT bit of the RTC\_ISR register is set between one and two RTCCLK cycles after being cleared, the INITF flag is set immediately instead of waiting for synchronization delay (which should be between one and two RTCCLK cycles), and the initialization of registers may fail.

Depending on the INIT bit clearing and setting instants versus the RTCCLK edges, it can happen that, after being immediately set, the INITF flag is cleared during one RTCCLK period then set again. As writes to calendar registers are ignored when INITF is low, a write during this critical period might result in the corruption of one or more calendar registers.

#### Workaround

After existing the initialization mode, clear the BYPSHAD bit (if set) then wait for RSF to rise, before entering the initialization mode again.

Note: It is recommended to write all registers in a single initialization session to avoid accumulating synchronization delays.

#### 2.8.5 Alarm flag may be repeatedly set when the core is stopped in debug

#### Description

When the core is stopped in debug mode, the clock is supplied to subsecond RTC alarm downcounter even when the device is configured to stop the RTC in debug.

As a consequence, when the subsecond counter is used for alarm condition (the MASKSS[3:0] bitfield of the RTC\_ALRMASSR and/or RTC\_ALRMBSSR register set to a non-zero value) and the alarm condition is met just before entering a breakpoint or printf, the ALRAF and/or ALRBF flag of the RTC\_SR register is repeatedly set by hardware during the breakpoint or printf, which makes any attempt to clear the flag(s) ineffective.

#### Workaround

None.

## 2.8.6 Detection of a tamper event occurring before enabling the tamper detection is not supported in edge detection mode

#### Description

When the tamper detection is enabled in edge detection mode (TAMPFLT = 00):

- When TAMPxTRG = 0 (rising edge detection): if the tamper input is already high before enabling the tamper detection, the tamper event may or may not be detected when enabling the tamper detection. The probability to detect it increases with the APB frequency.

- When TAMPxTRG = 1 (falling edge detection): if the tamper input is already low before enabling the tamper detection, the tamper event is not detected when enabling the tamper detection.

#### Workaround

Check the I/O state by software in the GPIO registers, just after enabling the tamper detection and before writing sensitive values in the backup registers. This ensures that no active edge occurred before enabling the tamper event detection.

### 2.9 I2C

#### 2.9.1 SMBus standard not fully supported

#### Description

The I2C peripheral is not fully compliant with the SMBus v2.0 standard since it does not support the capability to NACK an invalid byte/command.

#### Workaround

A higher-level mechanism must be used to verify that a write operation is being performed correctly at the target device, such as:

- the SMBAL pin if it is supported by the host

- the alert response address (ARA) protocol

- the host-notify protocol

#### 2.9.2 Start cannot be generated after a misplaced Stop

#### Description

If a master generates a misplaced Stop on the bus (bus error) while the microcontroller I2C peripheral attempts to switch to Master mode by setting the START bit, the Start condition is not properly generated.

#### Workaround

In the I<sup>2</sup>C standard, it is allowed to send a Stop only at the end of the full byte (8 bits + acknowledge), so this scenario is not allowed. Other derived protocols such as CBUS allow it, but they are not supported by the I2C peripheral.

A software workaround consists in asserting the software reset using the SWRST bit of the I2C\_CR1 control register.

#### 2.9.3 Mismatch on the "Setup time for a repeated Start condition" timing parameter

#### Description

In case of repeated Start, the "Setup time for a repeated Start condition" (named Tsu;sta in the I<sup>2</sup>C specification) can be slightly violated when the I2C operates in Master standard mode at a frequency between 88 kHz and 100 kHz.

The issue can occur only in the following configuration:

- In Master mode

- In Standard mode at a frequency between 88 kHz and 100 kHz (no limitation in Fast mode)

- SCL rise time:

- If the slave does not stretch the clock and the SCL rise time is more than 300 ns (if the SCL rise time is less than 300 ns, the issue does not occur).

- If the slave stretches the clock.

The setup time can be violated independently of the APB peripheral frequency.

#### Workaround

Reduce the frequency down to 88 kHz or use the I<sup>2</sup>C Fast mode, if it is supported by the slave.

#### 2.9.4 Data valid time (t<sub>VD:DAT</sub>) violated without the OVR flag being set

#### Description

The data valid time ( $t_{VD;DAT}$ ,  $t_{VD;ACK}$ ) described by the I<sup>2</sup>C standard can be violated (as well as the maximum data hold time of the current data ( $t_{HD;DAT}$ )) under the conditions described below. This violation cannot be detected because the OVR flag is not set (no transmit buffer underrun is detected).

This limitation can occur only under the following conditions:

- in Slave transmit mode

- with clock stretching disabled (NOSTRETCH = 1)

- if the software is late to write to the DR data register, but not late enough to set the OVR flag (the data register is written before)

#### Workaround

If the master device allows it, use the clock stretching mechanism by clearing the bit NOSTRETCH of the I2C\_CR1 register.

If the master device does not allow it, ensure that the software is fast enough when polling the TXE or ADDR flag to immediately write to the DR data register. For instance, use an interrupt on the TXE or ADDR flag and boost its priority to the higher level.

# 2.9.5 Both SDA and SCL maximum rise times (t<sub>r</sub>) violated when the VDD\_I2C bus voltage is higher than ((V<sub>DD</sub> + 0.3) / 0.7) V

#### Description

When an external legacy I<sup>2</sup>C bus voltage ( $V_{DD\_I2C}$ ) is set to 5 V while the MCU is powered from  $V_{DD}$ , the internal 5-Volt tolerant circuitry is activated as soon the input voltage ( $V_{IN}$ ) reaches the  $V_{DD}$  + diode threshold level. An additional internal large capacitance then prevents the external pull-up resistor ( $R_P$ ) from rising the SDA and SCL signals within the maximum timing ( $t_r$ ), which is 300 ns in Fast mode and 1000 ns in Standard mode. The rise time ( $t_r$ ) is measured from  $V_{IL}$  and  $V_{IH}$  with levels set at 0.3  $V_{DD\_I2C}$  and 0.7  $V_{DD\_I2C}$ .

#### Workaround

The external  $V_{DD_{12C}}$  bus voltage must be limited to a maximum value of (( $V_{DD}$  + 0.3) / 0.7) V. As a result, when the MCU is powered from  $V_{DD}$  = 3.3 V,  $V_{DD_{12C}}$  must not exceed 5.14 V to be compliant with I<sup>2</sup>C specifications.

#### 2.9.6 Spurious bus error detection in Master mode

#### Description

In Master mode, a bus error can be detected by mistake, thus causing the BERR flag to be wrongly raised in the status register. This generates a spurious Bus Error interrupt if the interrupt is enabled. A bus error detection has no effect on the transfer in Master mode, therefore the I2C transfer can continue normally.

#### Workaround

If a bus error interrupt is generated in Master mode, the BERR flag must be cleared by software. No other action is required and the ongoing transfer can be handled normally.

#### 2.10 USART

#### 2.10.1 Idle frame is not detected if the receiver clock speed is deviated

#### Description

If the USART receives an idle frame followed by a character, and the clock of the transmitter device is faster than the USART receiver clock, the USART receive signal falls too early when receiving the character start bit, with the result that the idle frame is not detected (the IDLE flag is not set).

#### Workaround

None.

#### 2.10.2 In full-duplex mode, the Parity Error (PE) flag can be cleared by writing to the data register

#### Description

In full-duplex mode, when the Parity Error flag is set by the receiver at the end of a reception, it may be cleared while transmitting by reading the USART\_SR register to check the TXE or TC flags and writing data to the data register. Consequently, the software receiver can read the PE flag as '0' even if a parity error occurred.

#### Workaround

The Parity Error flag should be checked after the end of reception and before transmission.

#### 2.10.3 Parity Error (PE) flag is not set when receiving in Mute mode using address mark detection

#### Description

If the USART receiver is in Mute mode, and is configured to exit from Mute mode using the address mark detection, when the USART receiver recognizes a valid address with a parity error, it exits from Mute mode without setting the Parity Error flag.

#### Workaround

None.

#### 2.10.4 Break frame is transmitted regardless of CTS input line status

#### Description

When the CTS hardware flow control is enabled (CTSE = 1) and the send break bit (SBK) is set, the transmitter sends a break frame at the end of the current transmission regardless of CTS input line status. Consequently, if an external receiver device is not ready to accept a frame, the transmitted break frame is lost.

#### Workaround

None.

### 2.10.5 RTS signal abnormally driven low after a protocol violation

#### Description

When RTS hardware flow control is enabled, the RTS signal goes high when data is received. If this data was not read and new data is sent to the USART (protocol violation), the RTS signal goes back to low level at the end of this new data.

Consequently, the sender gets the wrong information that the USART is ready to receive further data. On the USART side, an overrun is detected, which indicates that data has been lost.

#### Workaround

A workaround is required only if the other USART device violates the communication protocol, which is not the case in most applications.

Two workarounds can be used:

- After data reception and before reading the data in the data register, the software takes over the control of the RTS signal as a GPIO, and holds it high as long as needed. If the USART device is not ready, the software holds the RTS pin high, and releases it when the device is ready to receive new data.

- Make sure the time required by the software to read the received data is always lower than the duration of the second data reception. For example, this can be ensured by handling all the receptions in DMA mode.

#### 2.10.6 Start bit detected too soon when sampling for NACK signal from the smartcard

#### Description

According to ISO/IEC 7816-3 standard, when a character parity error is detected, the receiver shall transmit a NACK error signal  $10.5 \pm 0.2$  ETUs after the character START bit falling edge. In this case, the transmitter is able to detect correctly the NACK signal until  $11 \pm 0.2$  ETUs after the character START bit falling edge. In Smartcard mode, the USART peripheral monitors the NACK signal during the receiver time frame ( $10.5 \pm 0.2$  ETUs), while it should wait for it during the transmitter one ( $11 \pm 0.2$  ETUs). In real cases, this would not be a problem as the card itself needs to respect a 10.7 ETU period when sending the NACK signal. However, this may be an issue to undertake a certification.

#### Workaround

None.

#### 2.10.7 Break request can prevent the transmission complete flag (TC) from being set

#### Description

After the end of transmission of a data (D1), the transmission complete (TC) flag is not set if the following conditions are met:

- CTS hardware flow control is enabled,

- D1 is being transmitted,

- a break transfer is requested before the end of D1 transfer,

- CTS is de-asserted before the end of D1 data transfer.

#### Workaround

If the application needs to detect the end of a data transfer, check that the TC flag is set, and issue a break request.

#### 2.10.8 Guard time not respected when data are sent on TXE events

#### Description

In Smartcard mode, when sending a data on TXE event, the programmed guard time is not respected, that is the data written in the data register is transferred to the bus without waiting the completion of the guard-time duration corresponding to the previous transmitted data.

#### Workaround

Since in Smartcard mode the TC flag is set at the end of the guard time duration, wait until TC is set, then write the data.

### 2.10.9 RTS is active while RE or UE = 0

#### Description

The RTS line is driven low as soon as the RTSE bit is set, even if the USART is disabled (UE = 0) or if the receiver is disabled (RE = 0) that is not ready to receive data.

#### Workaround

After setting the UE and RE bits, configure the I/O used for RTS as an alternate function.

## 2.11 SPI/I2S

#### 2.11.1 BSY bit may stay high when SPI is disabled

#### Description

The BSY flag may remain high upon disabling the SPI while operating in:

- master transmit mode and the TXE flag is low (data register full).

- master receive-only mode (simplex receive or half-duplex bidirectional receive phase) and an SCK strobing

edge has not occurred since the transition of the RXNE flag from low to high.

- slave mode and NSS signal is removed during the communication.

#### Workaround

When the SPI operates in:

- master transmit mode, disable the SPI when TXE = 1 and BSY = 0.

- master receive-only mode, ignore the BSY flag.

- slave mode, do not remove the NSS signal during the communication.

## 2.11.2 In I<sup>2</sup>S slave mode, enabling I2S while WS is active causes desynchronization

#### Description